计算机体系结构实验报告.docx

《计算机体系结构实验报告.docx》由会员分享,可在线阅读,更多相关《计算机体系结构实验报告.docx(16页珍藏版)》请在冰点文库上搜索。

计算机体系结构实验报告

《计算机体系结构》

实验报告

计算机实验教学中心

实验名称FIFO存储器实验地点信息楼418实验日期2015.10

一、实验目的

掌握FIFO存储器的工作特性和读写方法

二、实验设备

PC、唐都实验箱

三、实验原理

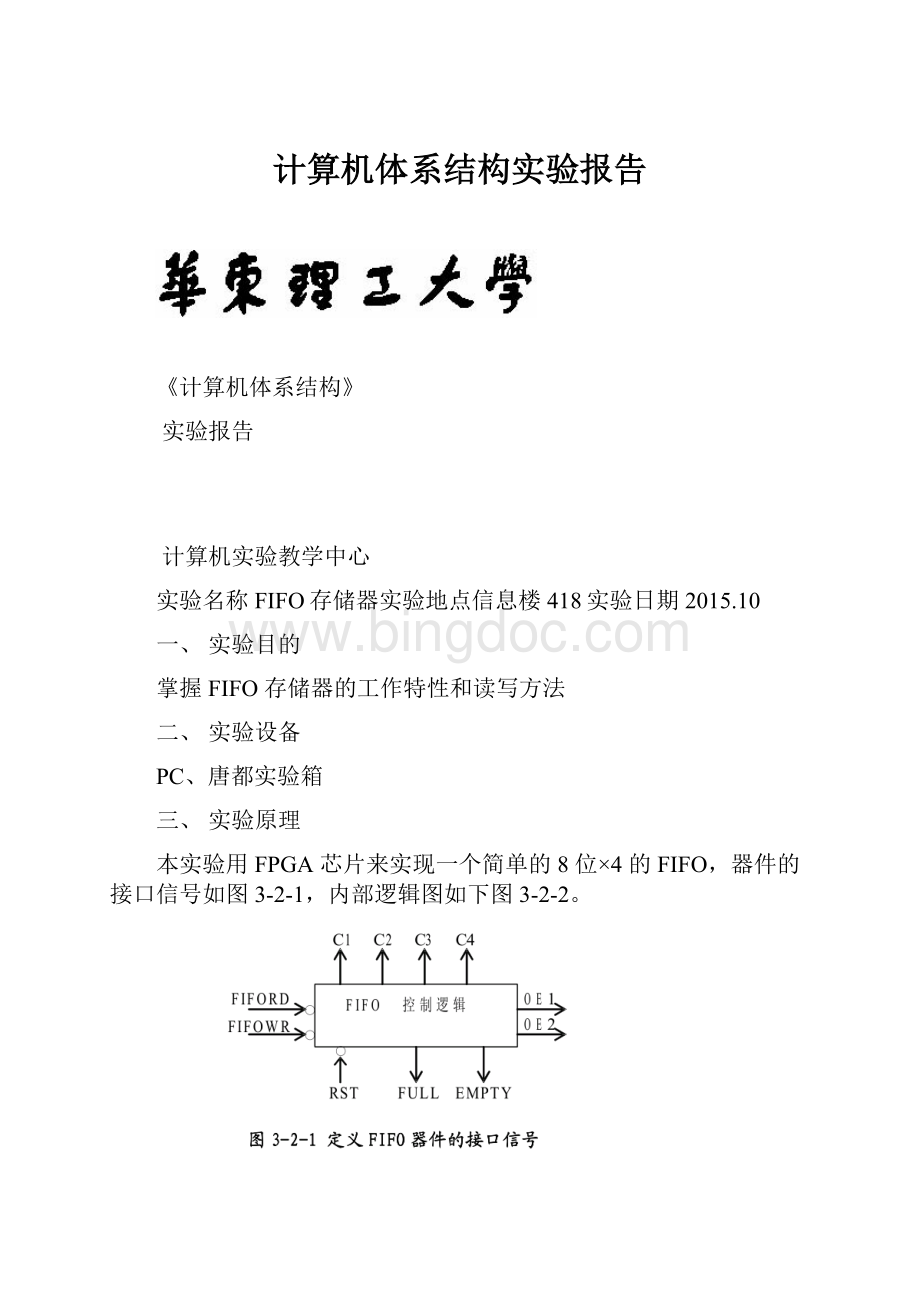

本实验用FPGA芯片来实现一个简单的8位×4的FIFO,器件的接口信号如图3-2-1,内部逻辑图如下图3-2-2。

其各信号的功能为:

EMPTY:

FIFO存储器空标志,高电平有效。

FULL:

FIFO存储器满标志,高电平有效。

RST:

清FIFO存储器为空。

FIFOWR:

FIFO存储器写入信号,低电平有效。

FIFORD:

FIFO存储器读信号,低电平有效。

ID0~ID7:

FIFO存储器输入数据线。

OD0~OD7:

FIFO存储器输出数据线。

四、实验操作及运行结果

1、按实验连接图接线。

注意:

连线时实验箱电源要处于关闭状态。

2、确保接线正确后,将实验箱连到电脑:

电源线+串口电缆(com口)+并口Jtag下载线(打印机口),并打开实验箱电源。

3、在软件QuartusII8.0中选择“File->OpenProject”选项,按照以下路径查找实验过程中需要下载到FPGA中的数据“C:

\TangDu\CMX\FPGA\FIFO\FIFO.qpf(.sof)”(该路径为“FIFO实验”的全路径,以后每次试验都需要用到的公共路径名为“C:

\TangDu\CMX\FPGA”),打开该文件后,单击软件中的“Programmer”选项,单击“Start”完成下载。

如果下载成功在界面Progress中可以看到100%的标志字样。

4、运行结果

接线图中B03和B04是FIFO空状态、满状态指示信号,分别接到扩展单元指示灯E0、E1上,用来反映FIFO当前的状态。

1)实验时,按动系统右下脚的CLR清零开关可使读、写信号计数清零。

这时指示灯E0亮,表示FIFO为空。

2)使用CON单元编号为SD27到SD20的开关模拟输入总线给出一个数据,按动时序与操作台单元的开关ST,可将该数写入到FIFO中。

这时指示灯E0灭,表示FIFO中已经有数据存在,说明当前FIFO的输出是有效的;依次写四次后,满标志置位,这时指示灯E1亮。

3)然后连续按动开关KK,给出读信号,将顺序读出所存的四个数,扩展总线的数据显

示灯EB7到EB0显示所读出的数据,四个数全部读出后,空标志置位,E0灯亮。

检查执行是否与理论值一致。

五、实验中出现的问题和解决方法

在实验中我们小组遇到了安装USB转串口驱动程序的问题,后参照老师给予的文档成功安装了驱动程序。

在连线过程中,有一根线出现了短路,导致实验结果运行错误,后经我们排查后发现,其中的一根导线断裂,更换后,成功运行实验。

我饿们这次实验掌握FIFO存储器的工作特性和读写方法,达到了实验目的,提高了小组成员的动手能力,收获很大。

实验名称多通路运算器和寄存器堆实验地点信息楼418实验日期2015.10

一、实验目的

掌握多通路的运算器与寄存器堆的工作原理及设计方法

2、实验设备

PC、唐都实验箱

3、实验原理

从IN单元读入一个数据,存入R0;从IN单元读入

另一个数据,存于R1;将R0和R1相加,结果存于R0;将R0和R1相加,结果存于R3,同

时打入暂存器A中;再将R0的值送OUT单元显示。

根据指令要求,得出用时钟进行驱动的状态机描述,即得出其有限状态机,如图1-2-4所

示。

下面分析每个状态中的基本操作:

S0:

空操作,系统复位后的状态

S1:

IN->R0;从IN单元往R0中打一个数

S2:

IN->R1;从IN单元往R1中打一个数

S3:

R0->A,R1->B;同时把R0、R1中的数打入暂存器A、B中

S4:

A+B->R0;将A+B的结果送往R0

S5:

A+B->R3,A+B->A;增加暂存器旁路,将A+B的结果送往R3的同时打入暂存器A

中

S6:

R0->OUT;把R0中的数送入输出单元显示。

4、实验操作及运行结果

1、把时序与操作台单元的“MODE”短路块插上,使系统工作在四节拍模式,按实验连接图接线。

注意:

连线时实验箱电源要处于关闭状态。

2、确保接线正确后,将实验箱连到电脑:

电源线+并口Jtag下载线(打印机口),并打开实验箱电源。

3、在软件QuartusII8.0中选择“File->OpenProject”选项,按照以下路径查找实验过程中需要下载到FPGA中的数据“C:

\TangDu\CMX\FPGA\ALU®\ALU®.qpf(.sof)”,打开该文件后,单击软件中的“Programmer”选项,单击“Start”完成下载。

如果下载成功在界面Progress中可以看到100%的标志字样。

4、用串口电缆连接实验箱和电脑打印机口,接通电源,打开软件CMX,进行串口测试(如果串口线未连接或者串口线故障则自动弹出错误信息对话框):

端口→串口选择→COM1或者COM2;然后,测试串口通讯是否成功:

端口→串口测试。

5、如果串口通讯成功,在PC机上运行TD-CMX,进入联机软件界面,选择菜单命令“【实

实验连接图

验】—【ALU®实验】”,打开数据通路图。

6、首先按CON单元的CLR开关进行系统清零,状态机为S0态。

然后,采用单节拍运行方式

来观察数据流通。

1)用连接成的双通道双端口运算器和双端口寄存器堆的结构实现以下一段程序:

从IN单元读入一个数据,存入R0;从IN单元读入另一个数据,存于R1;将R0和R1相加,结果存于R0;将R0和R1相加,结果存于R3,同时打入暂存器A中;再将R0的值送OUT单元显示

2)根据指令要求,得出用时钟进行驱动的状态机描述,即得出其有限状态机

S0:

空操作,系统复位后的状态

S1:

IN->R0;从IN单元往R0中打一个数

S2:

IN->R1;从IN单元往R1中打一个数

S3:

R0->A,R1->B;同时把R0、R1中的数打入暂存器A、B中

S4:

A+B->R0;将A+B的结果送往R0

S5:

A+B->R3,A+B->A;增加暂存器旁路,将A+B的结果送往R3的同时打入暂存器A中

S6:

R0->OUT;把R0中的数送入输出单元显示

3)每个状态运行4个周期(T1—T4),即每个状态按4次单节拍运行按钮

。

请在S1和S2状态,通过IN单元的开关分别输入两个数(比如1和3)。

观察数据通路图中数据的变化,并检查是否与状态的描述相符合。

最后观察OUT液晶单元是否显示正确(如果从IN单元输入的两个数分别为1和3,则OUT单元输出应该为4)。

五、实验中出现的问题和解决方法

在实验中我们小组连接完线路后,正常运行,直到最后一步无法正常显示结果,但结果已在ALU中正常显示,却没办法在out中显示,我猜测,一定是数据总线和out总线的连接出现了问题,于是我们检查了这两个部分,发现在out单元,有一根先出现了短路,更换导线后,结果正常显示。

这次实验我们明白掌握多通路的运算器与寄存器堆的工作原理及设计方法,通用软件更加直接明了的看见其运行过程。

收获很大。

实验名称基于RISC技术的模型机设计实验地点信息楼418实验日期2015.11

一、实验目的

掌握RISC处理器的指令系统特征和一般设计原则

二、实验设备

PC、唐都实验箱

三、实验原理

1.指令系统设计

本实验采用RISC思想设计的模型机选用常用的八条指令:

MOV、ADD、NOT、AND、

OR、LOAD、SAVE和JMP作为指令系统,寻址方式采用寄存器寻址及直接寻址两种方式。

指令格式采用单字节及双字节两种格式:

单字节指令(MOV、ADD、NOT、AND、OR、JMP)格式如下:

其中,OP-CODE为操作码,RS为源寄存器,RD为目的寄存器,并规定:

双字节指令(LOAD、SAVE)格式如下

其中括号中的1表示指令的第一字节,2表示指令的第二字节,OP-CODE为操作码,RS

为源寄存器,RD为目的寄存器,P为操作数地址,占用一个字节。

根据上述指令格式,表2-3-1列出了本模型机的八条机器指令的具体格式、汇编符号和指

令功能:

其中LOAD和SAVE指令中的M位用来判断操作的对象,当M=0时LOAD和SAVE指令是对IO进行操作,当M=1时LOAD和SAVE指令是对存储器进行操作。

系统采用外设和主存储器各自独立编码的编址方式,I/O译码单元由采用地址总线高两位

作二四译码来实现,原理图如图2-3-1所示。

由于用的是地址总线的高两位进行译码,I/O地址空间被分为四个区,如表2-3-2所示:

2.RISC处理器的模型计算机系统设计

本处理器的时钟及节拍电位如图2-3-2所示,数据通路图如图2-3-3所示,是采用双总线结

构来构建RISC处理器的,其指令周期流程图可设计如图2-3-4所示,在通路中除控制器单元由

FPGA单元来设计实现外,其它单元全是由这里实验系统上的单元电路来实现的。

3.控制器设计

(1)数据通路图中的控制器部分需要在FPGA中设计。

(2)用VHDL语言设计RISC子模块的功能描述程序,顶层原理图如图2-3-5:

4、实验操作及运行结果

1、把时序与操作台单元的“MODE”短路块拔掉,使系统工作在三节拍模式,按实验连接图接线。

注意:

连线时实验箱电源要处于关闭状态。

2、确保接线正确后,将实验箱连到电脑:

电源线+并口Jtag下载线(打印机口),并打开实验箱电源。

3、在软件QuartusII8.0中选择“File->OpenProject”选项,按照以下路径查找实验过程中需要下载到FPGA中的数据“C:

\TangDu\CMX\FPGA\RISC\RISC.sof”,打开该文件后,单击软件中的“Programmer”选项,单击“Start”完成下载。

如果下载成功在界面Progress中可以看到100%的标志字样。

4、用串口电缆连接实验箱和电脑打印机口,接通电源,打开软件CMX,进行串口测试(如果串口线未连接或者串口线故障则自动弹出错误信息对话框):

端口→串口选择→COM1或者COM2;然后,测试串口通讯是否成功:

端口→串口测试。

5、如果串口通讯成功,在PC机上运行TD-CMX,进入联机软件界面,选择菜单命令“【实

实验连接图

验】—【RISC实验】”,打开数据通路图。

6、在CMX软件界面中,通过选择【转储】—【装载】将文件C:

\TangDu\CMX\Sample\RISC模型机设计实验.txt装入指令区。

数据装载成功会在输出区有提示信息。

7、上述txt文件将以下程序段读入指令区:

地址(H)内容(H)助记符说明

0050LOADIN→R0

0140

0251LOADIN→R1

0340

0406MOVR1→R2

0518ADDR0+R2→R0

0660SAVER0→OUT

0780

0858LOAD[10]→R0

0910

0A70JMPR0→PC

1000

实验数据流通图

8、采用两种方法来观察数据流动:

1)将时序与操作单元的开关KK1、KK3置为‘运行’档,开关KK2置为‘单拍’档。

先按动CON单元的总清零开关CLR,程序从00H地址开始运行。

按动ST按钮单步运行,每按动一次ST按钮,观察数据流通图,分析数据与控制信号是否正确(是否实现了第7步的程序段功能)。

在执行程序时,需要在IN单元输入两个数据(对应最开始的两条LOAD指令,IN输入的数据分别送入R0、R1)。

2)采用单节拍运行方式

来观察数据流通。

每条指令运行三个周期。

观察数据流通图,分析数据与控制信号是否正确。

五、实验中出现的问题和解决方法

在实验中我们小组遇到了无法安装RISC.sof的问题,后参照老师给予的文档成功安装了驱动程序。

在实验中我们在实验电路的连接过程中发现了很多问题,后经一一排除,这次实验的连线很多,我们努力做到了细心仔细,没有出现过连线失误,很快将试验线路连接好,成功做出实验。

我饿们这次实验掌握RISC处理器的指令系统特征和一般设计原则,达到了实验目的,提高了小组成员的动手能力,对我们了解risc处理器的帮助很大,收获很大。