计算机系统结构课后答案chap2answer讲解学习.docx

《计算机系统结构课后答案chap2answer讲解学习.docx》由会员分享,可在线阅读,更多相关《计算机系统结构课后答案chap2answer讲解学习.docx(10页珍藏版)》请在冰点文库上搜索。

计算机系统结构课后答案chap2answer讲解学习

计算机系统结构课后答案chap2-answer

第二章计算机指令集结构设计

2.1名词解释

1.堆栈型机器——CPU中存储操作数的单元是堆栈的机器。

2.累加型机器——CPU中存储操作数的单元是累加器的机器。

3.通用寄存器型机器——CPU中存储操作数的单元是通用寄存器的机器。

4.CISC——复杂指令集计算机。

5.RISC——精简指令集计算机。

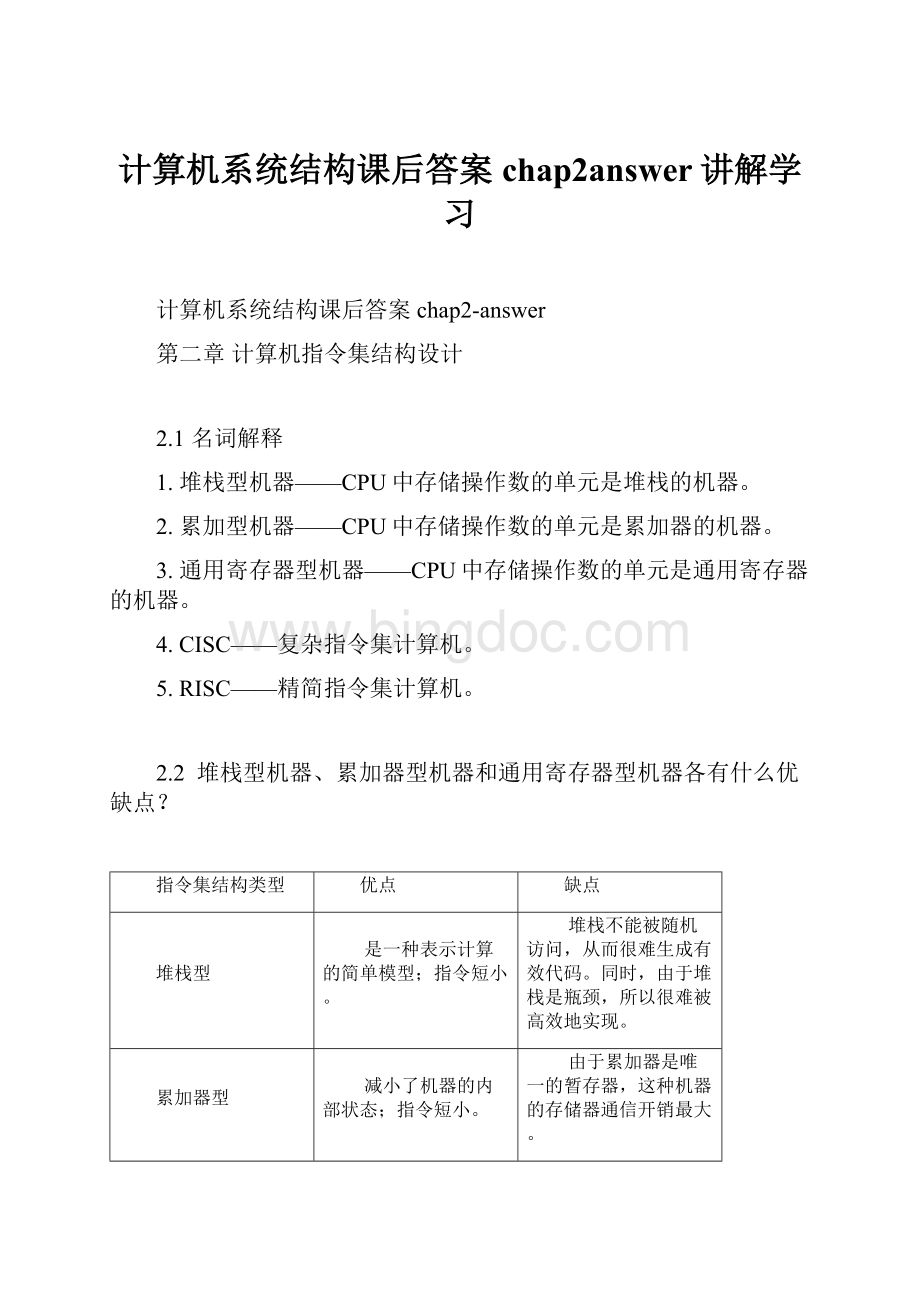

2.2堆栈型机器、累加器型机器和通用寄存器型机器各有什么优缺点?

指令集结构类型

优点

缺点

堆栈型

是一种表示计算的简单模型;指令短小。

堆栈不能被随机访问,从而很难生成有效代码。

同时,由于堆栈是瓶颈,所以很难被高效地实现。

累加器型

减小了机器的内部状态;指令短小。

由于累加器是唯一的暂存器,这种机器的存储器通信开销最大。

寄存器型

是代码生成最一般的模型。

所有操作数均需命名,且显式表示,因而指令比较长。

2.3常见的三种通用寄存器型机器的优缺点各有哪些?

指令集结构类型

优点

缺点

寄存器-寄存器型(0,3)

简单,指令字长固定,是一种简单的代码生成模型,各种指令的执行时钟周期数相近。

和指令中含有对存储器操作数访问的结构相比,指令条数多,因而其目标代码较大。

寄存器-存储器型(1,2)

可以直接对存储器操作数进行访问,容易对指令进行编码,且其目标代码较小。

指令中的操作数类型不同。

在一条指令中同时对一个寄存器操作数和存储器操作数进行编码,将限制指令所能够表示的寄存器个数。

由于指令的操作数可以存储在不同类型的存储器单元,所以每条指令的执行时钟周期数也不尽相同。

存储器-存储器型(3,3)

是一种最紧密的编码方式,无需“浪费”寄存器保存变量。

指令字长多种多样。

每条指令的执行时钟周期数也大不一样,对存储器的频繁访问将导致存储器访问瓶颈问题。

2.4指令集结构设计所涉及的内容有哪些?

(1)指令集功能设计:

主要有RISC和CISC两种技术发展方向;

(2)寻址方式的设计:

设置寻址方式可以通过对基准程序进行测试统计,察看各种寻址方式的使用频度,根据适用频度设置相应必要的寻址方式;

(3)操作数表示和操作数类型:

主要的操作数类型和操作数表示的选择有,浮点数据类型(可以采用IEEE754标准)、整型数据类型(8位、16位、32位的表示方法)、字符型(8位)、十进制数据类型(压缩十进制和非压缩十进制数据表示)等等。

(4)寻址方式的表示:

可以将寻址方式编码与操作码中,也可将寻址方式作为一个单独的域来表示。

(5)指令集格式的设计:

有固定长度编码方式、可变长编码方式和混合编码方式三种选择。

2.5简述CISC计算机结构指令集功能设计的主要目标。

从当前的计算机技术观点来看,CISC

结构有什么缺点?

CISC结构追求的目标是强化指令功能,减少程序的指令条数,以达到提高性能的目的。

从目前的计算机技术观点来看,CISC结构存在以下几个缺点:

(1)在CISC结构的指令系统中,各种指令的使用频率相差悬殊。

(2)CISC结构的指令系统的复杂性带来了计算机体系结构的复杂性,这不仅增加了研制时间和成本,而且还容易造成设计错误。

(3)CISC结构的指令系统的复杂性给VLSI设计带来了很大负担,不利于单片集成。

(4)CISC结构的指令系统中,许多复杂指令需要很复杂的操作,因而运行速度慢。

(5)在结构的指令系统中,由于各条指令的功能不均衡性,不利于采用先进的计算机体系结构技术(如流水技术)来提高系统的性能。

2.6简述RISC结构的设计原则。

(1)选取使用频率最高的指令,并补充一些最有用的指令;

(2)每条指令的功能应尽可能简单,并在一个机器周期内完成;

(3)所有指令长度均相同;

(4)只有Load和Store操作指令才访问存储器,其它指令操作均在寄存器之间进行

(5)以简单有效的方式支持高级语言。

2.7简述操作数的类型及其相应的表示方法。

操作数的类型主要有:

整数(定点)、浮点、十进制、字符、字符串、向量、堆栈等。

操作数类型有两种表示方法:

(1)操作数的类型由操作码的编码指定,这也是最常见的一种方法;

(2)数据可以附上由硬件解释的标记,由这些标记指定操作数的类型,从而选择适当的运算。

2.8表示寻址方式的主要方法有哪些?

简述这些方法的优缺点。

表示寻址方式有两种常用的方法:

(1)将寻址方式编于操作码中,由操作码在描述指令的同时也描述了相应的寻址方式。

这种方式译码快,但操作码和寻址方式的结合不仅增加了指令的条数,导致

了指令的多样性,而且增加了CPU对指令译码的难度。

(2)为每个操作数设置一个地址描述符,由该地址描述符表示相应操作数的寻址方式。

这种方式译码较慢,但操作码和寻址独立,易于指令扩展。

2.9通常有哪几种指令格式?

简述其适用范围。

(1)变长编码格式。

如果体系结构设计者感兴趣的是程序的目标代码大小,而不是性能,就可以采用变长编码格式。

(2)固定长度编码格式。

如果感兴趣的是性能,而不是程序的目标代码大小,则可以选择固定长度编码格式。

(3)混合型编码格式。

需要兼顾降低目标代码长度和降低译码复杂度时,可以采用混合型编码格式。

2.10为了对编译器设计提供支持,在进行指令集设计时,应考虑哪些问题?

(1)规整性。

(2)提供基本指令,而非解决方案。

(3)“简化方案的折中取舍标准”。

(4)“对于在编译时已经知道的量,提供将其变为常数的指令”。

2.11试就指令格式、寻址方式和每条指令的周期数(CPI)等方面比较RISC和CISC处理机的指令系统结构。

比较内容

CISC

RISC

指令格式

变长编码

定长编码

寻址方式

各种都有

只有load/store指令可以访存

CPI

远远大于1

为1

2.12现有如下C语言源代码:

for(I=0;i<=100,i++)

{A[i]=B[i]+C;}

其中,A和B是两个32位整数的数组,C和i均是32位整数。

假设所有数据的值及其地址均保存在存储器中,A和B的起始地址分别是0和5000。

C和i的地址分别是1500和2000。

在循环的两次迭代之间不将任何数据保存在寄存器中。

(1)请写出该C语言源程序的DLX实现代码。

(2)该程序段共执行了多少条指令。

(3)程序对存储器中的数据访问了多少次?

(4)DLX代码的大小是多少?

解:

(1)ADDIR1,R0,#1;初始化i

SW2000(R0),R1;存储i

loop:

LWR1,2000(R0);得到i的值

MULTR2,R1,#4;R2=B的字偏移

ADDIR3,R2,#5000;对R2加上基址

LWR4,0(R3);LDB[i]的值

LWR5,1500(R0);LDC的值

ADDR6,R4,R5;B[i]+C

LWR1,2000(R0);得到i的值

MULTR2,R1,#4;R2=A的字偏移

ADDIR7,R2,#0;对R2加上基址

SW0(R7),R6;A[i]<—B[i]+C

LWR1,2000(R0);得到i的值

ADDIR1,R1,#1;增加i

SW2000(R0),R1;存储i

LWR1,2000(R0);得到i的值

ADDIR8,R1,#-101;计数器是否为101

BNEZR8,loop;不是101,重复

(2)总共执行的指令数是设置(setup)指令数加上循环中重复的指令条数:

执行的指令=2+(16×101)=1618

为了计算数据访问的次数,可以用循环次数乘以每次循环数据访问次数再加上设置代码的次数:

(3)数据访问次数=1+(8×10)×101=809

代码大小就是程序中汇编指令数乘以4(DLX中每条指令占4字节):

(4)代码大小=4×18=72

2.13参考2.12题,现在假设将i的值和数组变量的地址在程序运行过程中,只要有可能就一直保存在寄存器中。

(1)请写出该C语言源程序的DLX实现代码。

(2)该程序断共执行了多少条指令。

(3)程序对存储器中的数据访问了多少次?

(4)DLX代码的大小是多少?

解:

本题对上题再次讨论,只不过是在对机器代码进行基本的优化后。

特别的,寄存器中的值可以重用,并且循环变量的代码应该提到循环之外。

注意到循环下标变量i的值仅在最后一次循环中存储,而且和以前一样,变量的地址小于16位,可以用立即数指令load地址。

对C代码进行优化后的一个可能DLX代码如下:

ADDIR1,R0,#1;初始化i

ADDIR3,R0,#0;A的基址

ADDIR4,R0,#5000;B的基址

LWR5,1500(R0);LDC的值

loop:

MULTR2,R1,#4;计算字偏移

ADDR6,R2,R4;计算B[i]地址

LWR7,0(R6);LDB[i]的值

ADDR8,R7,R5;B[i]+C

ADDR9,R2,R3;计算A[i]的地址

SW0(R9),R8;A[i]<-B[i]+C

ADDIR1,R1,#1;增加i

ADDIR10,R1,#-101;计数器是否为101

BNEZR10,loop;不是101,重复

out_of_loop:

SW2000(R0),R1;存储最后的i值

(2)总共执行的指令数是设置指令(setup)加上循环次数和循环指令数的乘积再加上清除指令数(cleanup):

执行指令数=4+(9×101)+1=914

(3)计算数据访问的次数可以用每次循环数据访问次数乘以循环次数再加上设置代码中的数据访问:

数据访问次数=1+(2×101)+1=204

(4)代码大小是程序中汇编指令数乘以4(DLX中每条指令占4字节):

代码大小=(4×14)=56

2.14读写存储器的频率、访问指令和沪剧的频率是设计存储器系统的重要依据之一。

参考表2.16中的整型平均指标,求:

(1)所有对数据的存储器访问所占的百分比;

(2)所有数据访问中读操作所占的百分比;

(3)所有存储器访问中读操作所占的百分比。

解:

(1)所有对数据的存储器访问所占的比例为:

26%;

(2)所有数据访问中读操作所占的比例为:

74%;

(3)所有存储器访问中读操作所占的比例为:

93%。

2.15对表2.16中的所有类型指令,通过测量其CPI,得到如下结果:

指令

时钟周期

所有的ALU指令

1

Load/Store指令

1.4

成功的条件分支指令

2.0

失败的条件分支指令

1.5

跳转指令

1.2

假设60%的条件分支指令转移成功,同时将上题表中其它一些类别的指令(没有被包含在上述类别中的指令)看作是ALU指令,请根据gcc和espresso基准程序计算上述各种类型指令出现的平均频率,以及这两个基准程序的有效(等效)CPI。

解:

上述指令所占的百分比如下表所示:

指令

时钟周期

百分比

所有ALU

1

52%

Load/Store指令

1.4

31.6%

成功的条件分支指令

2.0

9.8%

失败的条件分支指令

1.5

5.2%

跳转指令

1.2

2.7%

其等效CPI为:

1×52%+1.4×31.6%+2.0×9.8%+1.5×5.2%+1.2×2.7%=1.23