数字电路常用芯片应用设计概述.docx

《数字电路常用芯片应用设计概述.docx》由会员分享,可在线阅读,更多相关《数字电路常用芯片应用设计概述.docx(32页珍藏版)》请在冰点文库上搜索。

数字电路常用芯片应用设计概述

74ls138

摘要:

74LS138为3-8线译码器,共有54/74S138和54/74LS138两种线路结构型式,其中LS是指采用低功耗肖特基电路.

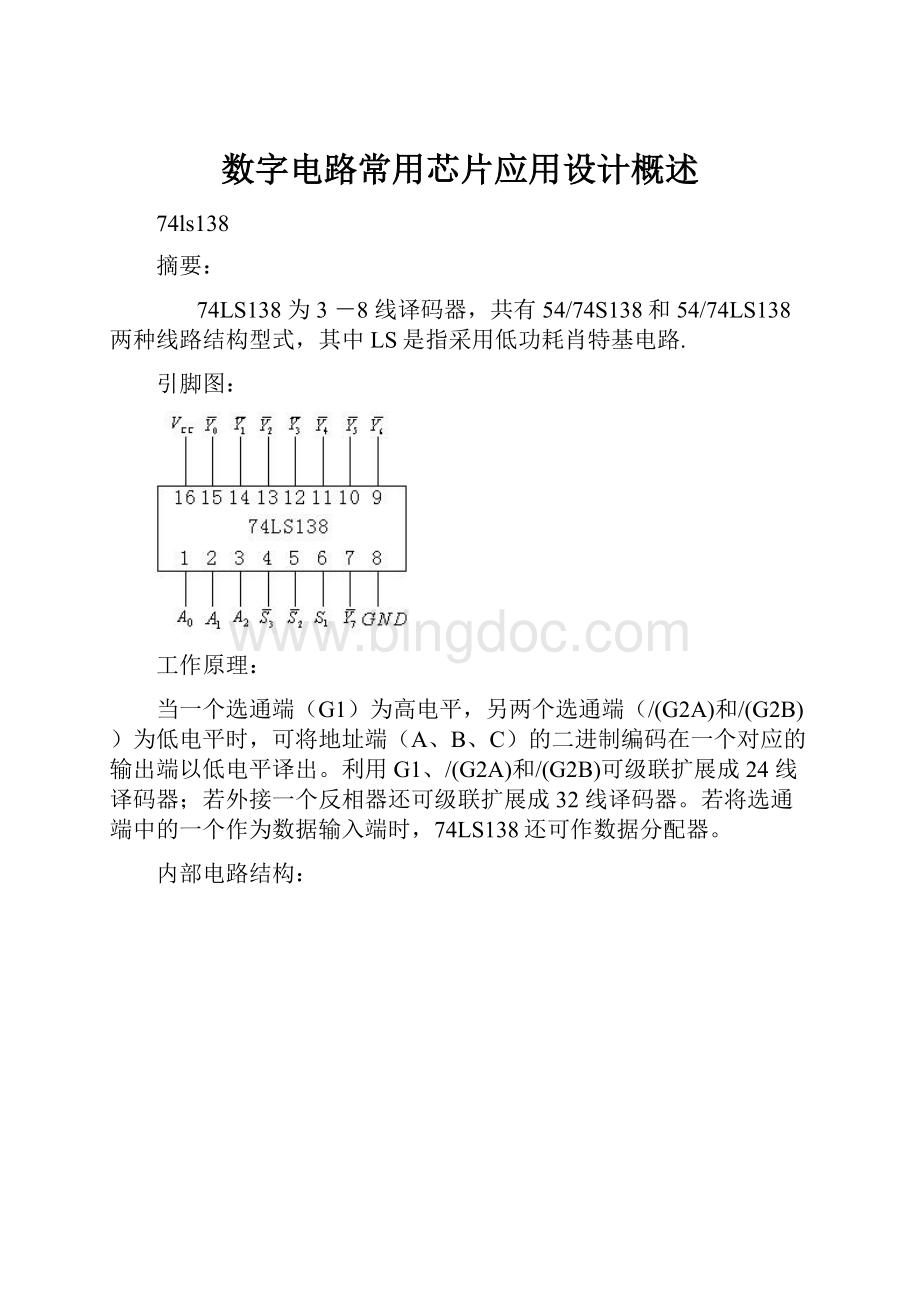

引脚图:

工作原理:

当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24线译码器;若外接一个反相器还可级联扩展成32线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器。

内部电路结构:

功能表真值表:

简单应用:

74ls139:

74LS139功能:

54/74LS139为2线-4线译码器,也可作数据分配器。

其主要电特性的典型值如下:

型号54LS139/74LS139传递延迟时间22ns功耗34mW

当选通端(G1)为高电平,可将地址端(A、B)的二进制编码在一个对应的输出端以低电平译出。

若将选通端(G1)作为数据输入端时,139还可作数据分配器。

74ls139引脚图:

引出端符号:

A、B:

译码地址输入端

G1、G2:

选通端(低电平有效)

Y0~Y3:

译码输出端(低电平有效

74LS139内部逻辑图:

74LS139真值表:

74ls164:

164为8位移位寄存器,其主要电特性的典型值如下:

54/74164 185mW 54/74LS16480mW当清除端(CLEAR)为低电平时,输出端(QA-QH)均为低电平。

串行数据输入端(A,B)可控制数据。

当A、B任意一个为低电平,则禁止新数据输入,在时钟端(CLOCK)脉冲上升沿作用下Q0为低电平。

当A、B有一个为高电平,则另一个就允许输入数据,并在CLOCK上升沿作用下决定Q0的状态。

引脚功能:

CLOCK:

时钟输入端CLEAR:

同步清除输入端(低电平有效)A,B:

串行数据输入端QA-QH:

输出端

(图174LS164封装图)

(图2 74LS164内部逻辑图)

极限值电源电压7V输入电压………5.5V

工作环境温度

54164…………-55~125℃

74164…………-0~70℃

储存温度…… -65℃~150℃

(图3真值表)

H-高电平L-低电平X-任意电平↑-低到高电平跳变

QA0,QB0,QH0-规定的稳态条件建立前的电平

QAn,QGn-时钟最近的↑前的电平

(图4时序图)

应用实例:

如图所示的电原理图,利用74LS164串行输入并行输出芯片作一个简单的电子钟,要求四个数码管显示时钟;其中LED1显示小时的十位,LED2显示小时的个位,LED3显示分钟的十位,LED4显示分钟的个位。

解:

采用单片机的串行口输出字形码,用74LS164和74LS139作为扩展芯片。

74LS164的功能是将80C51串行通信口输出的串行数据译码并在其并口线上输出,从而驱动LED数码管。

74LS139是一个双2-4线译码器,它将单片机输出的地址信号译码后动态驱动相应的LED。

因74LS139电流驱动能力较小,故用末级驱动三极管9013作为地址驱动。

将4只LED的字段位都连在一起,它们的公共端则由74LS139分时选通,这样任何一个时刻,都只有一位LED在点亮,也即动态扫描显示方式,其优点使用串行口进行LED通信程序编写相当简单,用户只需将需显示的数据直接送串口发送缓冲器,等待串行发送完毕标志位即可。

串行动态LED扫描电路

参考程序:

org0100h

movscon,#00h

main:

movr3,#00h

loop:

movr4,#0e8h

delay:

acalldisplay

dinzr4,delay

incr3

cjner3,#oah,loop

ajmpmain

display:

clrp3.2

clrp3.3

acalldisp

acalldelay1

setbp3.3

acalldisp

acalldelay1

setbp3.3

clrp3.2

acalldisp

acalldelay1

setbp3.2

setbp3.3

acalldisp

acalldelay1

ret

disp:

mova,r3

movdptr,#table

movca,@a+dptr

movbuff,a

wait:

jnbti,wait

clrti

ret

delay1:

movr6,#10h

loop1:

movr7,#38h

loop2:

djnzr7,loop2

djnzr6,loop1

ret

table:

db0c0h,0f9h,oa4h,0b0h,99h

db92h,82h,0f8h,80h,90h

end

74ls373:

简要说明:

74LS373是八D锁存器(3S,锁存允许输入有回环特性),常应用在地址锁存及输出口的扩展中。

SN74LS373,SN74LS374常用的8d锁存器,常用作地址锁存和i/o输出.可以用74hc373代换.74LS373是低功耗肖特基TTL8D锁存器,74H373是高速CMOS器件,功能与74LS373相同,两者可以互换。

74LS373内有8个相同的D型(三态同相)锁存器,由两个控制端(11脚G或EN;1脚OUT、CONT、OE)控制。

当OE接地时,若G为高电平,74LS373接收由PPU输出的地址信号;如果G为低电平,则将地址信号锁存。

工作原理:

74LS373的输出端O0~O7可直接与总线相连。

当三态允许控制端OE为低电平时,O0~O7为正常逻辑状态,可用来驱动负载或总线。

当OE为高电平时,O0~O7呈高阻态,即不驱动总线,也不为总线的负载,但锁存器内部的逻辑操作不受影响。

当锁存允许端LE为高电平时,O随数据D而变。

当LE为低电平时,O被锁存在已建立的数据电平。

74LS373引脚(管脚)图:

74LS373内部逻辑图:

74LS373真值表:

利用74LS373设计的一个超实用型抢答器:

利用74LS373设计的抢答器电路它由一片8D锁存器74LS373。

8只组别按键开关S1-S8,8组别抢答有效的状态显示发光二极管L1-L8,一个复位按键FW等组成。

该8路竞赛抢答器,每组受控于一个抢答按键开关,高电平表示抢答有效。

设置主持人控制键FW用于控制整个系统清0和抢答有效开始控制的启动。

每按下一次复位键FW时,使8D锁存器的控制端G为高电平,若组别按键开关S1~S8中任何一个都没按下,即对应8D锁存器的输入端D均为低电平,则此时8个输出端均为低电平,对应的发光二极管均不点亮,表示抢答者正在准备抢答状态。

按下复位键FW时,8D锁存器的控制端G为高电平,若组别按键开关S1-S8中存在一个或几个处于按下状态,即与之对应的8D锁存器的输入端D为高电平,此时与之对应的8D锁存器的输出端立即为高电平,对应的发光二极管被点亮,表示抢答者违规了。

只有每按下一次复位键FW,并在复位键FW抬起后,抢答才是有效的。

系统具有第一抢答信号鉴别和锁存功能。

在主持人将系统复位并使抢答有效开始后,第一抢答者按下抢答按钮。

对应的输入引脚接高电位1,8D锁存器的对应输出端立即为高电平1。

二极管VD1-VD8组成了或门电路。

使三极管VT1基极得到高电位而饱和导通使锁存器的G为低电平,将8D锁存器的输入信号锁存在了输出端,输入端的信号变化将不在影响输出端。

对应点亮的发光二极管指示出第一抢答者的组别。

在显示有效的组别的同时,也可同时采用蜂鸣器警示。

设计特点:

8D锁存器74LS373的允许端G的控制信号不是周期固定的脉冲信号,而是将取自锁存器输出端的信号处理后得到的,保证电路结构最简洁、处理时间最快捷,同时减少了脉冲源存在可能带来的干扰,使电路性能更可靠。

74ls151:

简要说明:

8选1数据选择器(有选通输入端,互补输出)

151为互补输出的8选1数据选择器,共有54/74151、54/74S151、74LS151三种线路结构形式,其主要电特性的典型值如下:

数据选择端(ABC)按二进制译码,以从8个数据(D0-D7)中选取1个所需的数据。

只有在选通端STROBE为低电平时才可选择数据。

151有互补输出端(Y、W),Y输出原码,W输出反码。

管脚图:

引出端符号:

A、B、C 选择输入端

D0-D7 数据输入端

STROBE 选通输入端(低电平有效)

W 反码数据输出端

Y 数据输出端

功能表:

逻辑图:

极限值:

电源电压 ------------------------------------------7V

输入电压

54/74151、54/74S151---------------------------------5.5V

54/74LS151 ------------------------------------7V

CD4532:

图为CD4532编码芯片引脚仿真分布图(GND为第8脚,VCC为16脚省略未画出)

EI引脚为高电平的时候,D0~D7输入相应的电平信号时Q0~Q2可以输出不同的二进制数据,同时EO输出低电平,GS输出高电平,D0~D7与Q0~Q2的关系如下:

D0为高电平Q2Q1Q0输出000

D1为高电平Q2Q1Q0输出001

D2为高电平Q2Q1Q0输出010

D3为高电平Q2Q1Q0输出011

D4为高电平Q2Q1Q0输出100

D5为高电平Q2Q1Q0输出101

D6为高电平Q2Q1Q0输出110

D7为高电平Q2Q1Q0输出111。

以下电路可以印证这种状态,在D6按键按下输入高电平时,GSEOQ2Q1Q0分别输出10110。

图为测试CD4532引脚的状态

我们都非常熟悉7LS138这个芯片把3个引脚的输出状态扩展为8个引脚输出的状态。

使用CD4532你就可以将8个输入引脚的状态转化为3个引脚的输入状态。

在单片机项目开发过程中,如果单片机引脚作为接收外界信号不够用时,实用CD4532是非常实用的。

555:

555时基电路的特点:

555集成电路开始是作定时器应用的,所以叫做555定时器或555时基电路。

但后来经过开发,它除了作定时延时控制外,还可用于调光、调温、调压、调速等多种控制及计量检测。

此外,还可以组成脉冲振荡、单稳、双稳和脉冲调制电路,用于交流信号源、电源变换、频率变换、脉冲调制等。

由于它工作可靠、使用方便、价格低廉,目前被广泛用于各种电子产品中,555集成电路内部有几十个元器件,有分压器、比较器、基本R-S触发器、放电管以及缓冲器等,电路比较复杂,是模拟电路和数字电路的混合体.

图为555集成电路内部结构图:

555集成电路是8脚封装,双列直插型,如图所示:

555时基集成电路各引脚功能描述:

脚①是公共地端为负极;

脚②为低触发端TR,低于1/3电源电压以下时即导通;

脚③是输出端V,电流可达2000mA;

脚④是强制复位端MR,不用可与电源正极相连或悬空;

脚⑤是用来调节比较器的基准电压,简称控制端VC,不用时可悬空,或通过0.01μF电容器接地;

脚⑥为高触发端TH,也称阈值端,高于2/3电源电压发上时即截止;

脚⑦是放电端DIS;⑧是电源正极VC。

555时基集成电路的主要参数为(以NE555为例):

电源电压4.5~16V。

输出驱动电流为200毫安。

作定时器使用时,定时精度为1%。

作振荡使用时,输出的脉冲的最高频率可达500千赫。

使用时,驱动电流若大于上述电流时,在脚③输出端加装扩展电流的电路,如加一三极管放大。

555集成电路封装图:

我们也可以把555电路等效成一个带放电开关的R-S触发器,如图1)所示,这个特殊的触发器有两个输入端:

阈值端(TH)可看成是置零端R,要求高电平,触发端(TR)可看成是置位端S,要求低电平,有一个输出端Vo,Vo可等效成触发器的Q端,放电端(DIS)可看成是由内部放电开关控制的一个接点,由触发器的Q端控制:

Q=1时DIS端接地,Q=0时DIS端悬空。

另外还有复位端MR,控制电压端Vc,电源端VDD和

地端GND。

这个特殊的触发器有两个特点:

(1)两个输入端的触发电平要求一高一低,置零端R即阈值端(TH)要求高电平,而置位端s即触发端(TR)则要求低电乎;

(2)两个输入端的触发电平使输出发生翻转的阈值电压值也不同,当Vc端不接控制电压时,对TH(R)端来讲,>2/3VDD是高电平1,<2/3VDD是低电平0:

而对TR(S)端来讲,>1/3VDD是高电平1,<1/3VDD是低电平0。

如果在控制端(Vc)上控制电压Vc时,这时上触发电平就变成Vc值,下触发电平就变成1/2Vc值,可见改变控制端的控制电压值就可以改变上下触发电平值。

它的功能表见图2)所示。

用555定时器组成施密特触发器

(1)当ui=0时,由于比较器C1=1、C2=0,触发器置1,即Q=1、,uo1=uo=1。

ui升高时,在未到达2VCC/3以前,uo1=uo=1的状态不会改变。

(1)当ui=0时,由于比较器C1=1、C2=0,触发器置1,即Q=1、,uo1=uo=1。

ui升高时,在未到达2VCC/3以前,uo1=uo=1的状态不会改变。

(2)ui升高到2VCC/3时,比较器C1输出为0、C2输出为1,触发器置0,即Q=0、,uo1=uo=0。

此后,ui上升到VCC,然后再降低,但在未到达VCC/3以前,uo1=uo=0的状态不会改变。

(1)当ui=0时,由于比较器C1=1、C2=0,触发器置1,即Q=1、,uo1=uo=1。

ui升高时,在未到达2VCC/3以前,uo1=uo=1的状态不会改变。

(2)ui升高到2VCC/3时,比较器C1输出为0、C2输出为1,触发器置0,即Q=0、,uo1=uo=0。

此后,ui上升到VCC,然后再降低,但在未到达VCC/3以前,uo1=uo=0的状态不会改变。

(3)ui下降到2VCC/3时,比较器C1输出为1、C2输出为0,触发器置1,即Q=1、,uo1=uo=1。

此后,ui继续下降到0,但uo1=uo=1的状态不会改变

555集成电路有双极型和CMOS型两种。

CMOS型的优点是功耗低、电源电压低、输入阻抗高,但输出功率较小,输出驱动电流只有几毫安。

双极型的优点是输出功率大,驱动电流达200毫安,其他指标则不如CMOS型的。

555的应用电路很多,只要改变555集成电路的外部附加电路,就可以构成几百种应用电路,大体上可分为555单稳、555双稳及555无稳(即振荡器)三类。

555单稳电路:

单稳电路有一个稳态和一个暂稳态,是利用电容的充放电形成暂稳态的,因此它的输入端都带有定时电阻和定时电容,常见的555单稳电路有两种:

1)人工启动型

将555电路的6、2脚并接起来接在RC定时电路上,在定时电容CT,两端接按钮开关SB,就成为人工启动型555单稳电路,用等效触发器替代555,下面分析它的工作原理:

稳态:

接上电源后,电容CT很快充电到VDD,触发器输入R=1,S=1,输出Vo=0,这是它的稳态。

暂稳态:

按下开关SB,CT上电荷很快放到零,相当于触发器输入R=0,S=0,输出立即翻转成Vo=l,暂稳态开始。

开关放开后,电源又向CT充电,经过时间TD后,CT上电压上升到>2/3VDD时,输出又翻转成Vo=O,暂稳态结束。

TD就是单稳电路的定时时间或延时时间,它和定时电阻RT和定时电容CT的值有关:

TD=1.1RTCT。

2)脉冲启动型

将555电路的6、7脚并接起来接在定时电容CT上,用2脚作输入就成为脉冲启动型单稳电路,电路的2脚平时接高电平,当输入接低电平或输入负脉冲时才启动电路,下面分析它的工作原理:

稳态:

接上电源后,R=1,S=1,输出Vo=0,DIS端接地,CT上的电压为0即R=0,输出仍保持Vo=0,这是它的稳态。

暂稳态:

输入负脉冲后,输入S=0,输出立即翻转成Vo=1,DIS端开路,电源通过RT向CT充电,暂稳态开始。

经过时间TD后,CT上电压上升到>2/3VDD时,输入又成为R=1,S=1,这时负脉冲已经消失,输出又翻转成Vo=0,暂稳态结束。

这时内部放电开关接通,DIS端接地,CT上电荷很快放到零,为下一次定时控制作准备。

电路的定时时间TD=1.1RTCT。

这两种单稳电路常用作定时延时控制。

555双稳电路

常见的555双稳电路有两种:

1)R-S触发器型双稳

将555电路的6、2脚作为两个控制输入端,7端不用,就成为一个R-S触发器。

注意两个输入端的触发电平和阈值电压不同,有时可能只有一个控制端,这时另外一个控制端要设法接死,根据电路要求可以把R端接到电源端,也可以把S接地,用R端作输入。

有两个输入端的双稳电路常用作电机调速、电源上下限告警等用途。

有一个输入端的双稳电路作为单端比较器用于各种检测电路。

2)施密特触发器型双稳

将555电路的6、2脚并接起来接成只有一个输入端的触发器,这个触发器输出电压和输入电压的关系是一个长方形的回线形,当输入V1=0时输出Vo=1,当输入电压从0上升到>2/3VDD后,Vo翻转成0,当输入电压从最高值下降到<1/3VDD后,Vo又翻转成1。

由于它的输入有两个不同的阈值电压,所以,这种电路常用于电子开关,各种控制电路、波形的变换和整形。

4555无稳电路(振荡器)

由555定时器构成的多谐振荡器。

接通电源后,电源VDD通过R1和R2对电容C充电,当Uc<1/3VDD时,振荡器输出Vo=1,放电管截止。

当Uc充电到≥2/3VDD后,振荡器输出Vo翻转成0,此时放电管导通,使放电端(DIS)接地,电容C通过R2对地放电,使Uc下降。

当Uc下降到≤1/3VDD后,振荡器输出Vo又翻转成1,此时放电管又截止,使放电端(DIS)不接地,电源VDD通过R1和R2又对电容C充电,又使Uc从1/3VDD上升到2/3VDD,触发器又发生翻转,如此周而复始,从而在输出端Vo得到连续变化的振荡脉冲波形。

脉冲宽度TL≈0.7R2C,由电容C放电时间决定;TH=0.7(R1+R2)C,由电容C充电时间决定,脉冲周期T≈TH+TL。

上面仅讨论了由555定时器构成的几种典型应用实例。

实际上,由于555定时器灵敏度高,功能灵活,因而在电子电路中获得广泛应用。

由555+4017构成的流水灯电路:

1.555用来定时,用它产生某种方波,相当于有的时钟信号

2.4017是个十进制计数器,按照时钟信号从10个口依次输出

CLK时钟信号。

E,低为计数使能。

MR,高为复位。

Q0-Q9是十进制输出。

CO,carry-out是进位输出。

ADC0809:

概述:

ADC0809是采样分辨率为8位的、以逐次逼近原理进行模—数转换的器件。

其内部有一个8通道多路开关,它可以根据地址码锁存译码后的信号,只选通8路模拟输入信号中的一个进行A/D转换。

1.主要特性

1)8路输入通道,8位A/D转换器,即分辨率为8位。

2)具有转换起停控制端。

3)转换时间为100μs(时钟为640kHz时),130μs(时钟为500kHz时)

4)单个+5V电源供电

5)模拟输入电压范围0~+5V,不需零点和满刻度校准。

6)工作温度范围为-40~+85摄氏度

7)低功耗,约15mW。

2.内部结构

ADC0809是CMOS单片型逐次逼近式A/D转换器,内部结构如图13.22所示,它由8路模拟开关、地址锁存与译码器、比较器、8位开关树型A/D转换器、逐次逼近

3.外部特性(引脚功能)

ADC0809芯片有28条引脚,采用双列直插式封装,如图13.23所示。

下面说明各引脚功能。

IN0~IN7:

8路模拟量输入端。

2-1~2-8:

8位数字量输出端。

ADDA、ADDB、ADDC:

3位地址输入线,用于选通8路模拟输入中的一路

ALE:

地址锁存允许信号,输入,高电平有效。

START:

A/D转换启动脉冲输入端,输入一个正脉冲(至少100ns宽)使其启动(脉冲上升沿使0809复位,下降沿启动A/D转换)。

EOC:

A/D转换结束信号,输出,当A/D转换结束时,此端输出一个高电平(转换期间一直为低电平)。

OE:

数据输出允许信号,输入,高电平有效。

当A/D转换结束时,此端输入一个高电平,才能打开输出三态门,输出数字量。

CLK:

时钟脉冲输入端。

要求时钟频率不高于640KHZ。

REF(+)、REF(-):

基准电压。

Vcc:

电源,单一+5V。

GND:

地。

ADC0809的工作过程:

首先输入3位地址,并使ALE=1,将地址存入地址锁存器中。

此地址经译码选通8路模拟输入之一到比较器。

START上升沿将逐次逼近寄存器复位。

下降沿启动A/D转换,之后EOC输出信号变低,指示转换正在进行。

直到A/D转换完成,EOC变为高电平,指示A/D转换结束,结果数据已存入锁存器,这个信号可用作中断申请。

当OE输入高电平时,输出三态门打开,转换结果的数字量输出到数据总线上。

转换数据的传送A/D转换后得到的数据应及时传送给单片机进行处理。

数据传送的关键问题是如何确认A/D转换的完成,因为只有确认完成后,才能进行传送。

为此可采用下述三种方式。

(1)定时传送方式

对于一种A/D转换其来说,转换时间作为一项技术指标是已知的和固定的。

例如ADC0809转换时间为128μs,相当于6MHz的MCS-51单片机共64个机器周期。

可据此设计一个延时子程序,A/D转换启动后即调用此子程序,延迟时间一到,转换肯定已经完成了,接着就可进行数据传送。

(2)查询方式

A/D转换芯片由表明转换完成的状态信号,例如ADC0809的EOC端。

因此可以用查询方式,测试EOC的状态,即可却只转换是否完成,并接着进行数据传送。

(3)中断方式

把表明转换完成的状态信号(EOC)作为中断请求信号,以中断方式进行数据传送。

不管使用上述那种方式,只要一旦确定转换完成,即可通过指令进行数据传送。

首先送出口地址并以信号有效时,OE信号即有效,把转换数据送上数据总线,供单片机接受。

应用实例:

ADC0809做的数字电压表:

参考程序