数字电子钟设计.docx

《数字电子钟设计.docx》由会员分享,可在线阅读,更多相关《数字电子钟设计.docx(7页珍藏版)》请在冰点文库上搜索。

数字电子钟设计

24时制数字电子钟设计

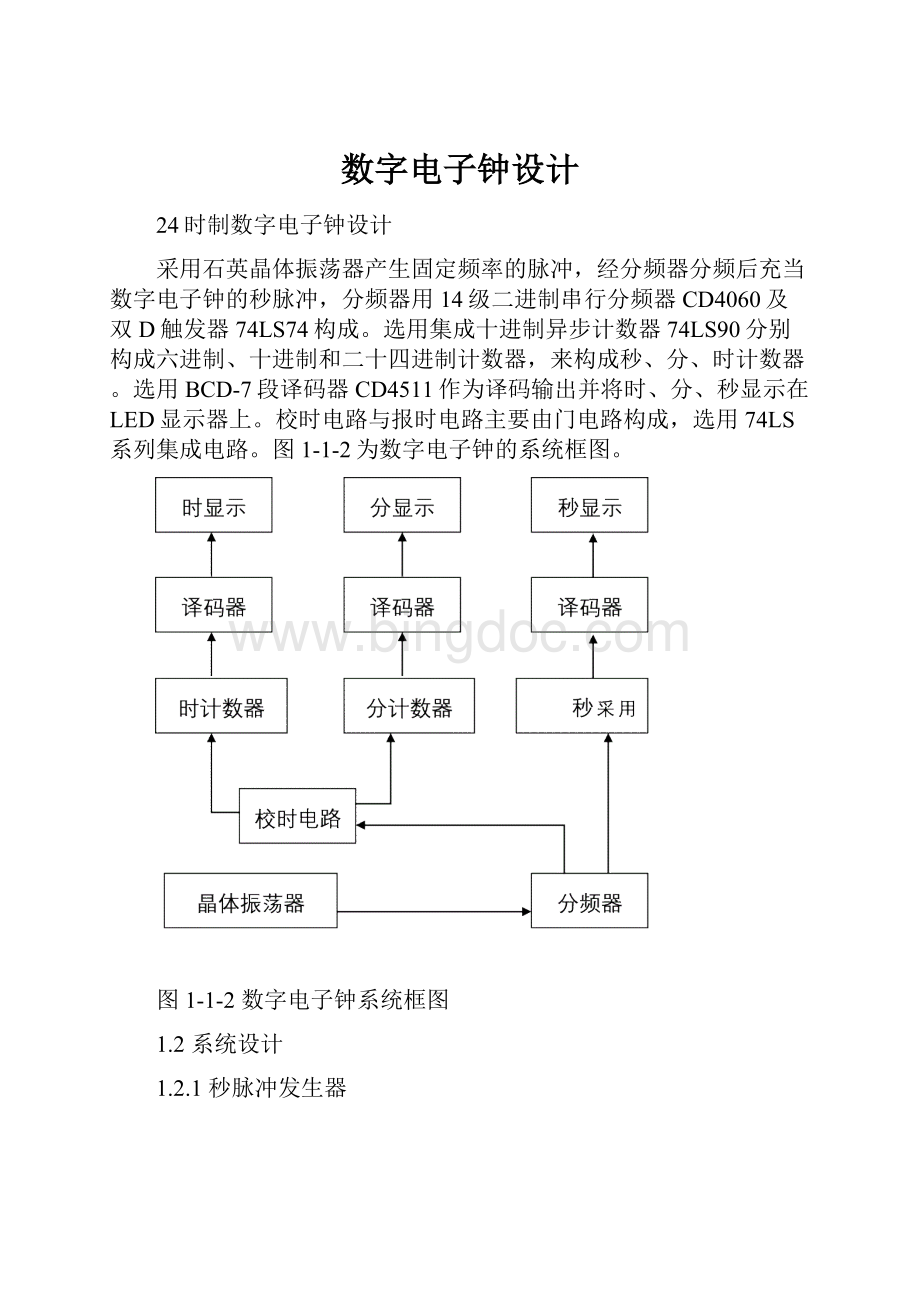

采用石英晶体振荡器产生固定频率的脉冲,经分频器分频后充当数字电子钟的秒脉冲,分频器用14级二进制串行分频器CD4060及双D触发器74LS74构成。

选用集成十进制异步计数器74LS90分别构成六进制、十进制和二十四进制计数器,来构成秒、分、时计数器。

选用BCD-7段译码器CD4511作为译码输出并将时、分、秒显示在LED显示器上。

校时电路与报时电路主要由门电路构成,选用74LS系列集成电路。

图1-1-2为数字电子钟的系统框图。

图1-1-2数字电子钟系统框图

1.2系统设计

1.2.1秒脉冲发生器

1Hz

图1-2-1-1秒脉冲发生器电路

秒脉冲发生器是数字电子钟的核心部分,它的精度和稳定度决定了数字电子钟的质量。

选用高精度和高稳定度的石英晶体振荡器发出脉冲,经过分频获得1Hz的秒脉冲。

该设计选用标称频率为32768Hz的石英晶振,通过15次二分频后获得1Hz的脉冲输出。

电路图如图1-2-1-1所示,74LS74的5脚输出1Hz秒脉冲。

集成芯片CD4060是14级二进制串行分频器,其引脚图和内部结构图分别如图1-2-1-2和图1-2-1-3所示。

双D触发器74LS74的引脚图如图1-2-1-4所示。

图1-2-1-2CD4060引脚图图1-2-1-474LS74引脚图

图1-2-1-3CD4060内部结构图

1.2.2秒、分、时计数器

利用6片集成十进制异步计数器74LS90分别构成2个六十进制和1个二十四进制计数器,充当秒、分、时计数器。

由于74LS90本身带有置0和置9功能,因而不需外加门电路即可实现清0功能。

74LS90的引脚图和功能表如图1-2-2-1和表1-2-2所示。

当Q0和CLK1相连时,其功能为8421BCD码十进制计数器。

当MR1和MR2全为高电平时,计数器置0;当MS1和MS2全为高电平时,计数器置9。

因此秒个位和分个位计数器直接将74LS90的12脚与1脚相连构成,而秒十位和分十位由74LS90构成六进制计数器,即将其9、8脚分别接2、3脚。

时计数器为二十四进制计数器,可将时个位芯片的8脚接时个位和时十位芯片的2脚,将时十位芯片的9脚接时个位和时十位芯片的3脚构成。

进位时,由于74LS90的时钟脉冲是下降沿触发的,可将低位计数器的输出最高位与高位计数器的时钟脉冲相连,当低位计数器的输出最高位由高电平变为低电平时触发高位计数器计数,实现进位。

秒、分、时计数器分别如图1-2-2-2、图1-2-2-3、图1-2-2-4所示。

图1-2-2-174LS90引脚图

表1-2-274LS90功能表

接译码器接译码器

接秒脉冲

图1-2-2-2秒计数器

接译码器接译码器

接秒十位芯片8脚

图1-2-2-3分计数器

接译码器接译码器

接分十位芯片8脚

图1-2-2-4时计数器

1.2.3译码显示电路gfGNDab

.

edGNDch

图1-2-3-1CD4511引脚图图1-2-3-2LG5011引脚图

译码是把给定的代码进行翻译,将时、分、秒计数器输出的四位二进制代码翻译为相应的十进制数,并通过LED显示器显示。

在此,我们采用BCD-7段译码器CD4511,数字显示用共阴极半导体数码管LG5011,其引脚图分别如图1-2-3-1、图1-2-3-2所示,译码器CD4511的功能表如表1-2-3所示。

限流电阻采用470Ω电阻,图1-2-3-3为CD4511与数码管组成的秒译码显示电路,分译码显示电路、时译码显示电路与其相同。

图1-2-3-3秒译码显示电路

表1-2-3CD4511功能表

1.2.4校时电路

校时电路分秒校时、分校时和时校时电路,如图1-2-4-1所示。

开关J3、J4、J5分别为秒校时、分校时和时校时开关,J1为校时按键。

当秒、分、时校时开关拨到校时档时,每按一下校时开关,相应数字增加1。

为了增加开关的稳定性,用异或门组成了防抖开关,使用了集成芯片74LS00,引脚图如图1-2-4-2所示。

图1-2-4-274LS00引脚图

图1-2-4-1校时电路

1.2.5系统电路

将秒脉冲发生电路、秒计数器、分计数器、时计数器、译码显示电路和校时电路分别进行仿真,并组成数字电子钟系统电路图,如图1-2-5所示。

图1-2-5数字电子钟系统电路图

2制作与调试

2.1主要仪器和仪表

制作过程中主要用到的仪器为示波器和函数发生器,仪表为万用表。

示波器用于显示秒脉冲发生电路的输出和计数器的输出,但是由于该示波器只有CH1和CH2两个通道,在观察计数器输出时需分多次观察。

函数发生器提供1Hz的脉冲波用于检测秒、分、时计数器电路的性能。

万用表用于测试数码管的引脚分布,测电阻值、电容值,测试部分引脚电压等。

2.2制作与调试过程中的故障及排除

开始我们使用的是面包板,且直接连接了系统电路后进行调试,结果失败了。

检查确定连线无误后,我们对各单元电路进行检查,还是失败了。

后来,我们发现面包板的许多管脚没有连通,且导线有断开现象,于是改焊电路板。

焊电路板时,我们对单元电路进行逐个焊接并调试。

调试秒计数器电路时,发现在连线无误且秒脉冲发生电路正常工作的情况下计数器仍然无法正常工作,经检查发现芯片损坏。

由于焊了芯片插座,更换芯片方便快捷。

重新更换芯片后,电路正常工作。

其他单元电路的制作与调试过程较顺利,整个数字电子钟系统也正常工作。

2.3电路性能测试

秒脉冲发生电路能输出较稳定的1Hz脉冲,秒计数电路与分计数电路均能较好地实现六十进制计数,时计数电路实现二十四进制计数,译码显示电路也正常工作。

接通电源后数字电子钟自动显示时间,将秒校开关拨到校时档时,每按校时按键一下,秒个位加1,而此时分和时仍正常工作,不受影响。

分校时和时校时与此相同,电路可实现独立校时,分校正时不影响时和秒的正常计数。

总体来说,整个数字电子钟电路性能较良好。

结束语

通过这次实验设计,我充分体会到数字电子钟是极为方便的,经过这次设计,我体会到了设计电路的重要性,也体会到了设计电路的实用性。

通过这次设计,我进一步熟悉了仿真软件的使用,从此以后我能更加熟悉地设计电路。