《ARM嵌入式系统初级教程基于CortexM0》GPIO寄存器.docx

《《ARM嵌入式系统初级教程基于CortexM0》GPIO寄存器.docx》由会员分享,可在线阅读,更多相关《《ARM嵌入式系统初级教程基于CortexM0》GPIO寄存器.docx(19页珍藏版)》请在冰点文库上搜索。

《ARM嵌入式系统初级教程基于CortexM0》GPIO寄存器

《ARM嵌入式系统初级教程(基于Cortex-M0)》第一章GPIO

1.1GPIO

本节以LPC1100系列Cortex-M0微控制器为例介绍了ARM微控制器的GPIO功能模块,包括如下内容:

●GPIO的基本功能和扩展功能以及相关的基本概念、原理、结构;

●GPIO功能的相关寄存器及其功能,以及寄存器的操作示例;

●GPIO基本操作的部分重要知识点。

1.1.1GPIO简介

GPIO(GeneralpurposeInput/Output,通用输入/输出),顾名思义,它是一种用于完成(数字量)输入/输出的常规功能设备,广泛使用于从单片机到ARM微控制器的各种微控制器。

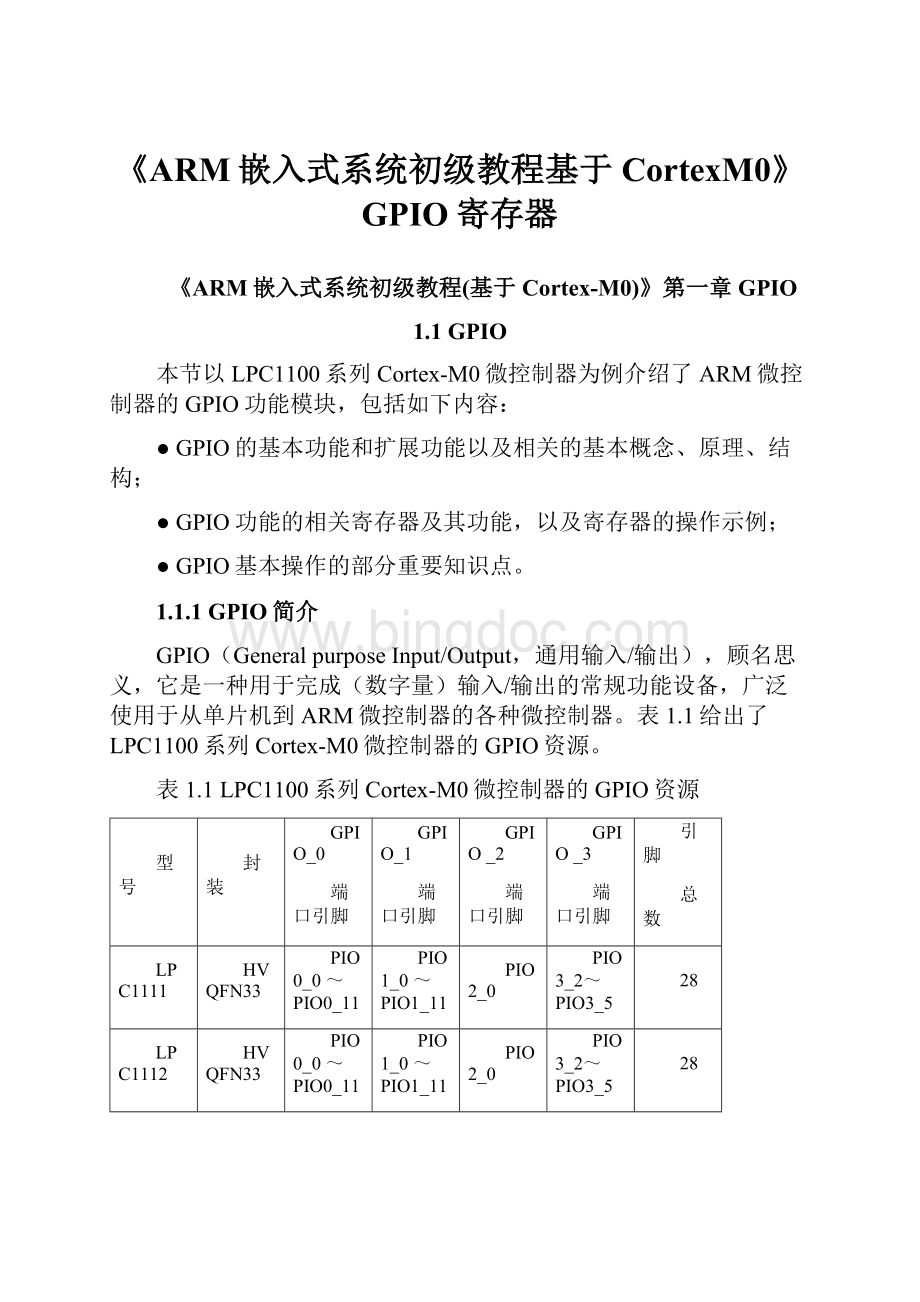

表1.1给出了LPC1100系列Cortex-M0微控制器的GPIO资源。

表1.1LPC1100系列Cortex-M0微控制器的GPIO资源

型号

封装

GPIO_0

端口引脚

GPIO_1

端口引脚

GPIO _2

端口引脚

GPIO _3

端口引脚

引脚

总数

LPC1111

HVQFN33

PIO0_0~PIO0_11

PIO1_0~PIO1_11

PIO2_0

PIO3_2~PIO3_5

28

LPC1112

HVQFN33

PIO0_0~PIO0_11

PIO1_0~PIO1_11

PIO2_0

PIO3_2~PIO3_5

28

LPC1113

HVQFN33

PIO0_0~PIO0_11

PIO1_0~PIO1_11

PIO2_0

PIO3_2~PIO3_5

28

LQFP48

PIO0_0~PIO0_11

PIO1_0~PIO1_11

PIO2_0~PIO2_11

PIO3_0~PIO3_5

42

LPC1114

HVQFN33

PIO0_0~PIO0_11

PIO1_0~PIO1_11

PIO2_0

PIO3_2~PIO3_5

28

PLCC44

PIO0_0~PIO0_11

PIO1_0~PIO1_11

PIO2_0~PIO2_11

PIO3_4~PIO3_5

38

LQFP48

PIO0_0~PIO0_11

PIO1_0~PIO1_11

PIO2_0~PIO2_11

PIO3_0~PIO3_5

42

LPC11C12

LQFP48

PIO0_0~PIO0_11

PIO1_0~PIO1_11

PIO2_0~PIO2_11

(无PIO2_4和PIO2_5)

PIO3_0~PIO3_5

40

LPC11C14

LQFP48

PIO0_0~PIO0_11

PIO1_0~PIO1_11

PIO2_0~PIO2_11

(无PIO2_4和PIO2_5)

PIO3_0~PIO3_5

40

1.1.2寄存器汇总

LPC1100系列Cortex-M0微控制器的GPIO相关寄存器见表1.2。

表1.2寄存器汇总

寄存器名称

功能

GPIO输入输出方向配置

GPIO引脚方向配置寄存器

(GPIO0DIR~GPIO3DIR)

控制GPIO引脚的方向

GPIO数据寄存器

GPIO数据寄存器(GPIO0DATA~PIO3DATA)

用于GPIO数据的读取和输出

GPIO中断的触发方式编程

GPIO中断监测寄存器

(GPIO0IS~GPIO3IS)

控制GPIO中断是边沿触发还是电平触发

GPIO双边沿监测寄存器

(GPIO0IBE~GPIO3IBE)

控制GPIO中断是否在上升沿和下降沿时都触发

GPIO中断事件寄存器

(GPIO0IEV~GPIO3IEV)

控制GPIO中断是低电平/下降沿触发还是高电平/上升沿触发

GPIO中断请求的状态查询

GPIO原始中断状态寄存器

(GPIO0RIS~GPIO3RIS)

提供所有GPIO引脚上的中断请求状态

GPIO屏蔽中断状态寄存器

(GPIO0MIS~GPIO3MIS)

仅提供未被屏蔽GPIO中断的引脚上的中断请求状态

GPIO中断的屏蔽

GPIO中断屏蔽寄存器

(GPIO0IE~GPIO3IE)

可设定屏蔽GPIO中断的GPIO引脚

GPIO边沿中断请求的清除

GPIO中断清除寄存器

(GPIO0IC~GPIO3IC)

可清除指定引脚的边沿中断请求

★请读者注意,在读写GPIO相关寄存器内的引脚功能位时,须确认该位对应的引脚是否存在。

例如,LPC1111的端口2只有一根引脚PIO2_0,那么读者在访问LPC1111内端口2对应的引脚方向寄存器GPIO2DIR时,只能访问GPIO2DIR的位0,访问其它位都是无效的,因为其它位没有对应的可配置引脚(GPIO2DIR寄存器的位功能描述见图1.1)。

1.1.3输入/输出功能

1.简介

图1.1是ARM微控制器GPIO中和输入/输出功能相关部分的功能框图。

图1.1GPIO输入/输出

由图1.1可知,ARM微控制器通过输入/输出数据寄存器存储GPIO引脚上的数据;通过输入/输出接口电路,令输出的电平信号驱动外界设备并使输入的电平信号能够被ARM微控制器准确识别和处理。

从单片机到ARM微控制器,在输入/输出的功能上,GPIO的基本结构和工作原理变化不大,下面对相关寄存器及其操作进行介绍。

2.GPIO引脚的方向配置

(1)简介

LPC1100系列Cortex-M0微控制器的GPIO引脚在使用前须配置方向以确定是输入引脚还是输出引脚,这一点和标准80C51单片机不同。

通过GPIO方向寄存器,用户可配置GPIO引脚(PIOx)的输入/输出方向,详见图1.2。

图1.2GPIO方向选择寄存器功能示意图

寄存器的操作示例见程序清单1.1。

程序清单1.1GPIO0DIR操作示例

GPIO0DIR|=1<<11;//令PIO0_11引脚为输出方向

注:

GPIOnDIR寄存器的方向设定位的复位值为0x00,这意味着默认情况下,GPIO引脚为输入。

(2)输入切换为输出时的引脚电平变化

当引脚由输入切换为输出时,引脚电平会怎样变化呢?

其实,输出引脚上的电平仍是由切换前的输入引脚电平状态决定:

●若输入引脚在切换方向前为高电平;那么切换后,输出引脚就为高电平;

●若输入引脚在切换方向前为低电平;那么切换后,输出引脚就为低电平。

那么,若输入引脚悬空,那么在转换为输出时引脚的电平是什么呢?

由于引脚悬空且为输入状态,此时引脚上的电平状态无法确定;这就意味着,当该引脚转为输出时,会输出一个无法预测的电平,这可能会导致电路误动作或造成其它的危害。

因此,用户在使用GPIO输入引脚时,须注意不让它悬空。

3.GPIO数据读取和输出

(1)简介

GPIO数据寄存器被用于GPIO数据的输入和输出,其位功能描述详见图1.3。

图1.3GPIO数据寄存器功能示意

以GPIO0DATA为例,操作示例详见程序清单1.2。

程序清单1.2GPIO0DATA操作示例

/*

*演示通过读写GPIO0DATA来完成GPIO输入输出的操作,这里没有在GPIO0DATA里对引脚进行

*屏蔽处理,用户可通过GPIO0DATA控制PIO0_0~PIO0_11的全部引脚

*/

GPIO0DATA|=1<<11;//令PIO0_11引脚输出高电平

temp=GPIO1DATA;//读取PIO1_0~PIO1_11输入引脚上的数据

(2)GPIO引脚屏蔽操作

在LPC1100系列Cortex-M0微控制器中,GPIOnDATA寄存器地址的位13~位2,不是用于寻址GPIOnDATA寄存器的,而是用于指定GPIOnDATA寄存器对应端口的GPIO引脚的屏蔽设置。

如表1.3所示,可以看到每一个GPIOnDATA寄存器都有多个地址,这些地址都是对应同一个GPIOnDATA寄存器,但这些地址的位13~位2的值是不同的,因而对应的引脚屏蔽设置也不同。

这里首先对GPIOnDATA寄存器位13~位2的功能作说明:

●位13~位2中为1的地址位对应的GPIO引脚可通过GPIOnDATA寄存器读写;

●位13~位2中为0的地址位对应的GPIO引脚不可通过GPIOnDATA寄存器读写,也就是被屏蔽。

下面举例进一步说明,当按地址0x00005088访问GPIO0DATA寄存器时,地址位7和3的值为1,那么此时引脚的屏蔽情况如何呢?

读者阅读图1.4可得知:

●GPIO0DATA的地址位13至地址位2,分别对应引脚PIO0_11~引脚PIO0_0;

●地址位[13:

2]中为0的位所对应引脚和GPIOnDATA寄存器断开了连接;

●地址位7和地址位3对应的PIO0_5和PIO0_1引脚受GPIOnDATA寄存器的控制。

图1.4屏蔽GPIO引脚

(3)GPIOnDATA寄存器的地址

如表1.3所示,随着屏蔽的引脚不同,每个GPIODATA寄存器会有许多不同地址。

当GPIOnDATA寄存器地址的位13~位2都为1时,GPIODATA寄存器可控制所有对应GPIO引脚,此时的GPIOnDATA寄存器地址见表1.3中“不屏蔽GPIO引脚时的地址”这一列。

表1.3寄存器的地址

寄存器名

寄存器地址

不屏蔽GPIO引脚时的地址

GPIO0DATA

0x50000000~0x50003FFC

0x50003FFC

GPIO1DATA

0x50010000~0x50013FFC

0x50013FFC

GPIO2DATA

0x50020000~0x50023FFC

0x50023FFC

GPIO3DATA

0x50030000~0x50033FFC

0x50033FFC

(4)通过GPIO数据寄存器读取引脚状态

除了可读取GPIO输入引脚的电平状态外,GPIO数据寄存器可以反映GPIO输出引脚的电平状态;甚至,当引脚工作在其它数字功能时,GPIO数据寄存器也可以反映出引脚上的电平状态。

这为读取引脚状态提供了一个简单快捷的方法。

(5)写GPIO数据寄存器对引脚状态的影响

对输入引脚状态的影响

可能用户有时会不小心将本应写到输出引脚的数据写到输入引脚对应的数据位,那么这是否会导致该输入引脚出现错误状态呢?

LPC1100系列Cortex-M0微控制器可以避免这种误操作带来的危害,其GPIO数据寄存器的数值变化不会影响GPIO输入引脚的电平状态。

对其它数字功能引脚状态的影响

当引脚被配置为其它数字功能例如UART、I2C时,对GPIO数据寄存器无论进行何种操作,引脚状态都不受影响。

1.1.4扩展特性

1.简介

相对于单片机,ARM微控制器凭借丰富资源和先进架构,令其GPIO的功能得到了扩展。

下文对一些常见的扩展特性进行介绍:

●高速GPIO模式;

●支持GPIO中断。

LPC1100系列Cortex-M0微控制器的GPIO支持上述扩展特性。

2.高速GPIO

在高速数据采集系统、控制高速IC或与其通信、模拟高速数据通信接口等应用场合中,常常要求微控制器具备高速GPIO。

例如,在视频监控的某些应用中,摄像机摄像端的专用信号处理芯片会将采集到的视频信号转换成能为ARM微控制器识别并处理的视频数据,然后输出到ARM微控制器的GPIO接口。

这些视频数据流量大且速度非常快,因而对与其接口的GPIO的输入/输出速度提出了很高要求。

LPC1100系列Cortex-M0微控制器的GPIO即为高速GPIO,详见图1.5。

图1.5LPC1100系列Cortex-M0微控制器内的GPIO

根据图1.5,我们可以将Cortex-M0内核访问高速GPIO和访问其它片内外设的对比详见表1.4。

表1.4Cortex-M0内核对高速GPIO和其它片内外设的访问对比

访问对象

访问路径

总线使用冲突

访问速度

高速GPIO

直接访问

除了片内存储器外,无其它功能设备与高速GPIO争夺AHB总线,发生总线使用冲突的情况较少

快

其它功能设备

经过AHB总线、总线桥访问

许多功能设备都须占用APB总线,十分容易发生总线使用冲突

慢

实际测试中,在内核时钟为50MHz的情况下,LPC1100系列Cortex-M0微控制器的高速GPIO输入/输出速度可达23MHz左右。

和其它具有普通GPIO模式和高速GPIO模式的ARM微控制器不同,LPC1100系列Cortex-M0微控制器只有一种GPIO模式,即高速GPIO。

用户使用LPC1100系列Cortex-M0微控制器的高速GPIO特性无须再另外编程选择。

3.GPIO中断

(1)简介

LPC1100系列Cortex-M0微控制器的每根GPIO引脚都可作为一个边沿触发或电平触发的外部中断源:

●设定为边沿触发方式时,可设定为上升沿触发、下降沿触发、双边沿触发;

●设定位电平触发方式时,可设定为高电平触发、低电平触发。

注:

何谓上升沿触发、何谓电平触发呢?

下面来介绍与GPIO中断使用密切相关的基础知识。

图1.6基础概念

(2)基础概念

和GPIO中断的使用密切相关的一些基础概念详见图1.6。

GPIO中断

GPIO中断实际上就是在GPIO引脚的基础上添加了外部中断功能。

当用户将GPIO引脚设置为输入时,该GPIO引脚就可以作为一个外部中断源了。

GPIO中断请求状态

GPIO中断请求包括有效和无效两个状态,这两个状态的含义如下:

●有效。

这意味着,该GPIO引脚上已经产生了一个中断请求,等待ARM微控制器响应;

●无效。

这意味着,该GPIO引脚上没有中断请求,ARM微控制器无须响应来自该GPIO引脚的中断。

用户可以通过GPIO中断请求状态寄存器来查询每一个GPIO引脚的中断请求状态。

GPIO中断屏蔽

用户可以屏蔽任意一个GPIO引脚上的中断。

此时,无论该GPIO引脚上的中断请求状态如何,该GPIO引脚上的中断请求都不会得到ARM微控制器的响应。

LPC1100系列Cortex-M0微控制器提供了GPIO中断屏蔽寄存器来供用户对每一个GPIO中断的屏蔽与否进行控制。

GPIO中断清除

如果已经产生的GPIO中断请求没有及时得到处理;那么,可能在下一次使能GPIO中断时,该“遗留”中断请求意外地被ARM微控制器响应了;所以,用户需要注意清除GPIO引脚上未被处理的中断请求。

用户可以通过相关寄存器完成GPIO中断清除操作,详情见GPIO中断的“相关寄存器”小节。

GPIO中断触发方式

GPIO中断触发方式是指触发GPIO中断的信号类型,例如是电平信号抑或边沿信号?

是高电平信号抑或低电平信号?

当指定类型的信号出现在GPIO引脚时,GPIO内部就会向ARM微控制器提交GPIO中断请求。

详细信息请见表1.5。

表1.5GPIO中断触发方式

GPIO中断触发信号

描述

图示

低电平

当GPIO引脚上有低电平信号时,产生GPIO中断请求

高电平

当GPIO引脚上有高电平信号时,产生GPIO中断请求

上升沿

当GPIO引脚有一个上升沿信号时,产生GPIO中断请求

下降沿

当GPIO引脚有一个下降沿信号时,产生GPIO中断请求

双边沿

当GPIO引脚有一个上升沿或下降沿信号时,都会产生GPIO中断请求

电平触发和边沿触发是不同的。

如表1.6所示,清晰地说明了低电平触发和下降沿触发的不同点。

表1.6低电平触发与下降沿触发对比

GPIO中断

触发方式

GPIO引脚电平从高翻转至低

后,该引脚是否产生GPIO中断

低电平保持期间是否产生中断请求

低电平触发

产生

低电平保持期间,GPIO中断请求将一直有效,微控制器可能会不断地响应中断

下降沿触发

产生

低电平保持期间,无GPIO中断请求产生,微控制器可以在完成一次中断响应后处理其它工作

(6)相关寄存器

GPIO中断监测寄存器

GPIO中断监测寄存器用于配置引脚的中断触发类型,寄存器的位功能描述详见图1.7。

图1.7GPIO中断监测寄存器

GPIO中断双边沿触发寄存器

GPIO中断双边沿触发寄存器的功能是用于进一步设定引脚的中断触发方式,详见图1.8。

图1.8GPIO中断双边沿触发寄存器

GIPO中断事件寄存器

GPIO中断事件寄存器的功能是用于设定引脚中断触发方式的极性。

详见图1.9。

图1.9GPIO中断事件寄存器位功能描述

GPIO中断屏蔽寄存器

如果GPIOnIE寄存器中的位设为高,对应的引脚就会触发各自的中断;清除该位就会禁止对应引脚的中断触发。

寄存器位功能示意详见图1.10。

图1.10GPIO中断屏蔽寄存器位功能示意

★读者特别需要注意,使能GPIO中断前需要清除中断请求,下面举例来说明。

某位工程师在调试LPC1114的外部中断时遇到一个问题:

他将LPC1114的PIO0_9设为上升沿触发的GPIO中断,之后就向PIO0_9不断输入方波。

但是,他在方波上升沿输出到PIO0_9前,会将LPC1114的中断关闭;等方波的上升沿过去一段时间后,再打开中断。

他认为,理论上,打开中断时并无上升沿信号输出到PIO0_9,所以应该不会触发PIO0_9的GPIO中断,但实际情况却是当中断一打开,PIO0_9就发生了GPIO中断。

最后,他发现,如果他在打开中断前,在GPIO0IC中清除了PIO0_9的GPIO中断请求,他说的“故障”现象就不会再发生了。

事实上,在使能GPIO中断前和处理完中断后,都需要清除中断请求;否则就会对一个已处理过的中断请求重复响应。

GPIO原始中断状态寄存器

GPIOnRIS寄存器的位反映了对应引脚上的原始中断状态。

位读出为0时表示对应的输入引脚还未启动中断。

该寄存器为只读,具体详见图1.11。

图1.11GPIOnRIS寄存器位功能描述

GPIO屏蔽中断状态寄存器

GPIOnMIS寄存器中的位读为高反映了输入线的状态触发中断。

GPIOMIS是屏蔽后的中断状态。

该寄存器为只读。

寄存器的位功能描述详见图1.12。

图1.12GPIO屏蔽中断状态寄存器示意图

GPIO原始中断状态寄存器和GPIO屏蔽中断状态寄存器有什么区别呢?

GPIO原始中断状态寄存器可以反映所有GPIO引脚的中断状态,无论该GPIO引脚的中断请求是否受到了屏蔽,所以人们称呼它是反映了原始的GPIO中断状态。

GPIO屏蔽中断状态寄存器则只反映出没有被屏蔽的GPIO中断的状态。

GPIO中断清除寄存器

GPIO中断清除寄存器可用于清除引脚的GPIO中断请求,这个寄存器是只写的。

寄存器的位功能描述详见图1.13。

图1.13GPIO中断清除寄存器位功能示意

在LPC1100系列Cortex-M0微控制器中,在GPIOnIC里完成清除操作后,NVIC模块还需要2个工作时钟来完成清除相应GPIO中断请求的操作;因此,用户在GPIOnIC里完成清除操作后还需要等待一段时间才能退出中断服务程序。

考虑到这一点,建议用户在中断服务程序里首先完成中断请求清除操作,然后再执行其它处理,这样就可以自然而然地满足了延时要求。

★此外,读者需要特别注意。

在GPIO清除寄存器的位功能描述里可以看到,该寄存器仅用于清除GPIO边沿中断请求,但不能清除电平中断请求。

这是因为,在电平触发中断的模式下,只要电平有效,就会一直触发中断请求(见表1.6);只有撤除触发中断的电平,电平中断请求才会被撤销。

(7)寄存器操作示例

GPIO中断相关寄存器的操作示例见程序清单1.3。

程序清单1.3GPIO中断相关寄存器操作示例

GPIO0DIR=~(0x01<<11);//设置PIO0_11为输入①

GPIO0IS=~(0x01<<11);//设置PIO0_11为边沿触发

GPIO0IEV=0x01<<11;//设置PIO0_11为上升沿触发

GPIO0IC|=0x01<<11;//清除边沿中断②

GPIO0IE|=0x01<<11;//使能PIO0_11的GPIO中断

while((GPIO0RIS&(0x01<<11))==0){//不断查询PIO0_11GPIO中断是否发生

}

……//中断发生,进行后续处理

注:

程序标注①处,GPIO引脚必须设为输入引脚,才可能产生GPIO中断。

程序标注②处,使能GPIO中断前,须先清除先前产生的GPIO中断请求。

1.1.5小结

最后,将本节所涉及的重要知识点小结详见表1.7。

表1.7重要知识点小结

LPC1100系列Cortex-M0微控制器GPIO小结

高速GPIO

1

高速GPIO和内存位于同一系统总线,CPU会以最高优先级访问高速GPIO,这令高速GPIO获得了非常高的输入/输出速度

输入/

输出功能

1

使用输入/输出功能时,须选择引脚方向

2

用户可通过GPIO数据寄存器的访问地址设定须屏蔽的GPIO引脚

3

和其它的ARM微控制器和单片机不同,LPC1100系列Cortex-M0微控制器的一个GPIO数据寄存器可以有多个地址,每一个地址都对应一种GPIO引脚屏蔽设置。

读者需要特别注意这一点

4

所有数字功能引脚上的电平状态都可通过GPIO数据寄存器读取

5

当GPIO引脚由输入切换到输出时,输出引脚将延续之前输入引脚上的电平状态

I/O口功能

模式配置

1

可配置I/O口功能模式为上拉电阻、下拉电阻、不接上拉和下拉的悬空模式、中继模式

2

可使能带滞后功能的输入缓冲以滤除输入数字信号中的干扰

3

注意使用中继模式以避免输入引脚悬空给系统带来的隐患

GPIO中断

1

每一根GPIO输入引脚都可以设定为GPIO中断输入脚

2

GPIO中断可选择高、低电平触发或上升沿、下降沿触发或上升沿下降沿都触发

3

注意理解电平触发和边沿触发的区别。

电平触发模式下,只要电平有效,中断请求就会始终有效

4

表1.5中给出了各种能够触发GPIO中断请求的触发信号信息

5

使能中断前需要注意清除中断请求。

其中边沿触发的GPIO中断请求可通过写相关寄存器清除;电平触发的GPIO中断请求只能通过撤除触发中断的电平信号实现

6

LPC1100系列Cortex-M0微控制器要求“清除中断请求”和“退出中断服务程序”这两个操作之间至少有2个工作时钟以上的延时