DDS正弦信号发生器设计报告.docx

《DDS正弦信号发生器设计报告.docx》由会员分享,可在线阅读,更多相关《DDS正弦信号发生器设计报告.docx(10页珍藏版)》请在冰点文库上搜索。

DDS正弦信号发生器设计报告

基于DDS的正弦信号发生器

设计报告

院系:

自动化工程学院电子学系

专业:

电子信息科学与技术

班级:

2009级2班

姓名:

何伍健

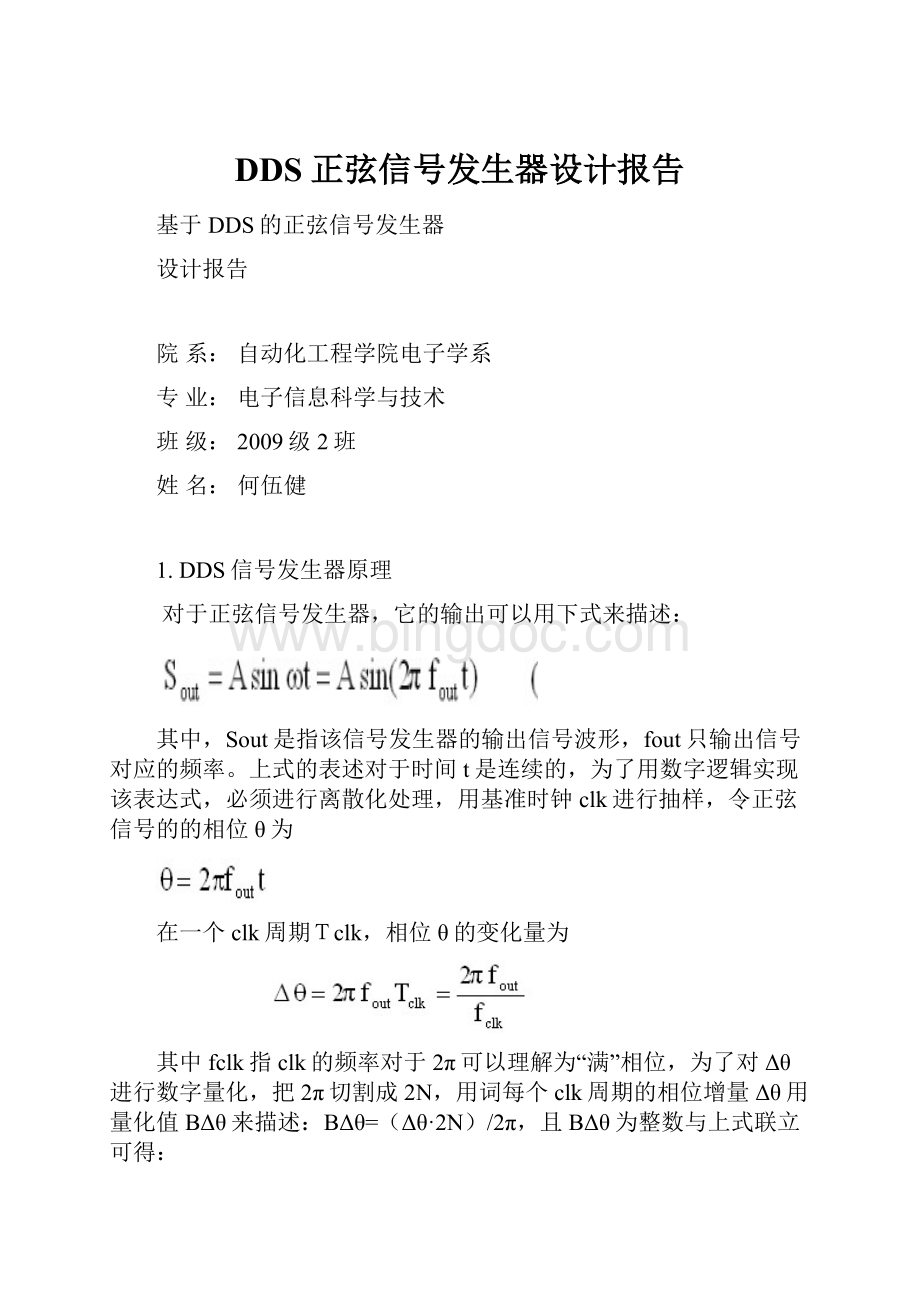

1.DDS信号发生器原理

对于正弦信号发生器,它的输出可以用下式来描述:

其中,Sout是指该信号发生器的输出信号波形,fout只输出信号对应的频率。

上式的表述对于时间t是连续的,为了用数字逻辑实现该表达式,必须进行离散化处理,用基准时钟clk进行抽样,令正弦信号的的相位θ为

在一个clk周期Tclk,相位θ的变化量为

其中fclk指clk的频率对于2π可以理解为“满”相位,为了对Δθ进行数字量化,把2π切割成2N,用词每个clk周期的相位增量Δθ用量化值BΔθ来描述:

BΔθ=(Δθ·2N)/2π,且BΔθ为整数与上式联立可得:

显然,信号发生器可以描述

其中θk-1指前一个clk周期的相位值,同样得出

由以上推倒可以得出,只要对相位的量化值进行简单的累加运算,就可以得到正弦信号的当前相位值,而用于累加的香味增量量化值BΔθ决定了信号的输出频率fout并呈现简单的线性关系。

直接数字合成器DDS就是根据以上原理而设计的数控频率合成器,下图为其基本DDS结构,主要有相位累加器、相位调制器、正弦ROM查找表构成图中的相位累加器、相位调制器、正弦ROM查找表是DDS结构中的数字部分,

图1

2.基于DDS的正弦信号发生器设计实现

根据设计原理框图分别设计出加法器、寄存器、正弦波ROM。

2.1.1.32位加法器ADDER32设计

在原理图文件文件下在空白处双击,单击“MegaWizardPlug-InManager”选择第一项

图2

选择器件为cyclone,语言方式为VerilogHDL。

在算数项Arithmetic中选择计数器LPM_ADD_SUB.存于所建工程文件夹下命名为ADDER32.

单击NEXT,进入以后对话框后选择32位加法器工作模式选择有一位加法进位输出,选择有符号加法方式,选择2级流水线工作模式,此时该加法器变为有时序电路的模块,最后至finish按钮,编辑完成。

如图3所示

图3

2.1.2.32位寄存器DFF32设计

寄存器DFF32由LMP_FF宏模块担任,生成方法同ADDER32相同,设置位数为32位,且为时序控制模块。

最终生成后如图4所示

图4

DFF32与ADDER32构成一个32位累加器其高十位A[31..22]为波形数据ROM的地址

2.1.3.正弦波ROM设计

1.首先通过mif文件来产生正弦波

图5

存盘并命名为sin_rom.mif

2.LPM_ROM的订制:

按ADDER32的产生方法来产生LMP_ROM,在宏模块选择中选“MemoryComplier”中“ROM:

1-PORT”项

图6

依次设定地址线与数据线的位宽均为十位,最后产生LMP_ROM,如下图所示:

v

图7

2.2DDS信号发生器原理图

图8

原理图共分为三大部分:

相位累加器,相位调制器,正弦ROM查找表。

1.相位累加器

相位累加器是DDS的核心,完成相位累加的过程其输入可以称为频率字输入在输入时增加一个寄存器可以使频率字改变时不会干扰相位累加器的正常工作。

相位累加器如图9所示

图9

2.相位调制器

相位调制器接受相位累加器的相位输出,加上一个相位偏移值,可用于信号的相位调制。

加一个寄存器可用于信号的同步保持。

如图10所示

图10

3.正弦ROM查找表

正弦ROM的输入是相位调制器的输出,即ROM的地址值,输出送往DAC转化为模拟信号。

如图11所示

图11

正弦ROM的mif部分数据如图12所示

图12

2.3仿真结果及分析

当相位输入字不变保持00时,改变频率字输入可得如下结果

图13

结果分析:

当频率字增加时电路中ROM的数据输出的速度也将提高

当频率输入字不变,改变相位字输入改变时可得如图14结果

图14

结果分析:

当相位字改变时DAC的波形也随之改变,当相位字增大时波形的相位为增大

当频率字和相位字均改变时,波形如图15所示

图15

2.4硬件调试结果及分析

调试、仿真成功后进行硬件调试阶段,在“Assignment”菜单下选择“Device”项进行器件选择Cyclone中的EP1C12Q240C8器件,在“Assignment”菜单下选择”pins”项,进行管脚锁定。

键1(PIO0)——B17——233

键2(PIO1)——B16——234

键3(PIO2)——B15——235

键4(PIO3)——B14——236

键5(PIO4)——F17——237

键6(PIO5)——F16——238

键7(PIO6)——F15——239

键8(PIO7)——F14——240

Clock0——clk——28

(PIO24)——DAC12——21

(PIO25)——DAC13——41

(PIO26)——DAC14——128

(PIO27)——DAC15——132

(PIO28)——DAC16——133

(PIO29)——DAC17——134

(PIO30)——DAC18——135

(PIO31)——DAC19——136

管脚锁定后再次进行编译,成功后选择“tools”菜单下“programmer”项进行下载。

用示波器进行波形观察。

键1至键4用来控制频率字的输入,键5至键8控制相位字的输入,clock0选择12MHz,。

按动键1至键4调节频率子输入,键5至键8调节相位字输入

当改变频率字时波形变化如图16所示

图16

当改变相位字时波形如图17所示

图17

当同时改变频率字与相位字时,波形如图18所示

图18

硬件调试结果分析:

该调试的结果满足了实验的要求,验证了DDS信号发生器的功能,即能够调节频率与相位。

实验心得与体会:

通过本次实验,复习并熟练了QuartusⅡ的基本功能和操作,掌握了VerilogHDL语言的设计输入,编译,仿真和调试等过程。

实验过程中由于对仪器的使用,特别是硬件实验箱的不熟练,导致在下载调试上浪费了大量时间,精力,锁定引脚后没有再次保存编译,实验模式选择不对等,这些都是在实验中暴露出来的问题,也是今后需要改进提高的地方。

深刻领悟到了只有熟练掌握QuartusⅡ的基本功能和操作,理论联系实际,硬件结合软件,条理,细心并且,才能提高自己的设计开发能力。

参考文献:

《EDA技术实用教程——VerilogHDL版》潘松黄继业潘明编著