低成本双路正弦波发生器.docx

《低成本双路正弦波发生器.docx》由会员分享,可在线阅读,更多相关《低成本双路正弦波发生器.docx(32页珍藏版)》请在冰点文库上搜索。

低成本双路正弦波发生器

低成本双路正弦波发生器(D题)

摘要

本作品基于DDS工作原理,利用CPLD编程实现NCO功能,进而实现题目中要求产生正弦波,每路信号的频率、幅度及两路信号的相位差均可程控设置。

以P89V51RD2芯片为本设计的控制核心,通过单片机与CPLD的连接实现对波形的频率、幅度及相位差的程控可调,并且可实现取消微处理器单元,控制逻辑单元也能实现独立设置特定参数信号功能。

参数设定与相关信息通过液晶屏显示。

关键字:

DDS原理,微处理器,可编程逻辑,CPLD

任务:

设计、制作一个低成本双路正弦波发生器,每路信号的频率、幅度及两路信号的相位差均可程控设置。

除工作电源外,正弦波发生器由微处理器单元(含键盘显示)、控制逻辑单元和模拟电路单元三部分组成。

要求控制逻辑单元不使用任何存储器资源,模拟电路单元不使用集成DAC且无可调阻容件。

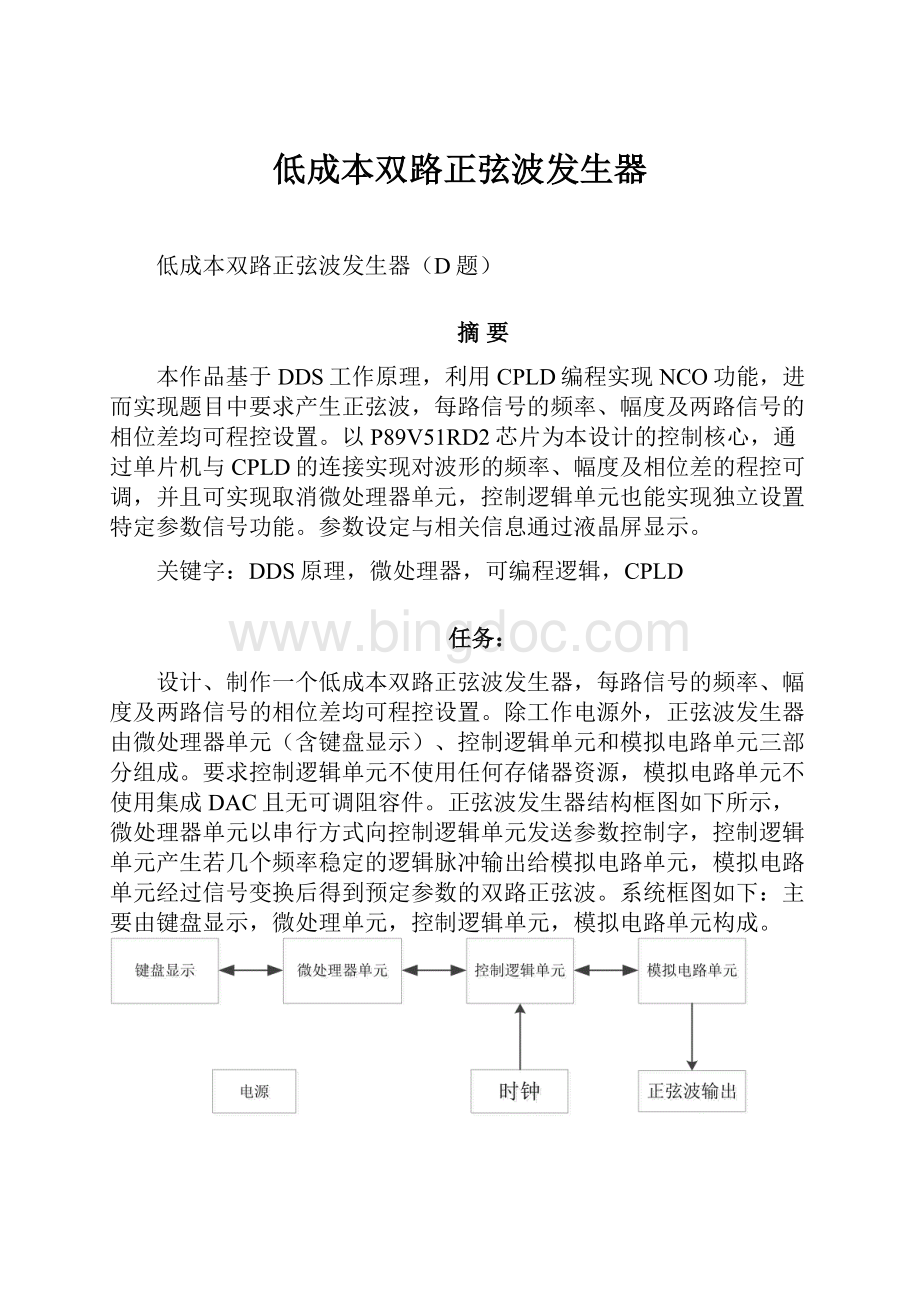

正弦波发生器结构框图如下所示,微处理器单元以串行方式向控制逻辑单元发送参数控制字,控制逻辑单元产生若几个频率稳定的逻辑脉冲输出给模拟电路单元,模拟电路单元经过信号变换后得到预定参数的双路正弦波。

系统框图如下:

主要由键盘显示,微处理单元,控制逻辑单元,模拟电路单元构成。

本任务中推荐采用的信号变换原理有:

PWM信号经低通滤波后可变换为直流电压,窄带范围内的方波经低通滤波后可变换为相应频率的正弦波,两路不同频率的正弦波经差频与低通滤波后可变换为另一低频正弦波。

要求

基本要求

(1)两路正弦波的频率范围1Hz—1kHz,步进值不大于1Hz,频率准确度不低于%;

(2)两路正弦波输出最大幅度不低于3V,幅度设置,设置分辨率不低于12bit;

(3)正弦波信号在整个频率设置范围内,波形失真度不大于2%;

(4)两路信号的相位差可以在0—359度内可调,设置分辨力不大于1度;

(5)所有参数均可程控设置;

(6)微处理器单元与控制逻辑单元信号连线应不超过3条。

发挥部分

(1)控制逻辑单元输出给模拟电路单元的信号线应不超过5条;

(2)当两路信号频率为1到10间的倍频关系时能同步,示波器观测两路波形稳定;

(3)设定的输出信号电压值在整个频段内,变换量小于5%;

(4)两路正弦信号幅度设置为零时,输出噪声小于5mV;

(5)取消微处理器单元,控制逻辑单元也能实现独立设置特定参数信号的输出;

(6)其他,主要考核硬件成本、技术指标提升和工艺水平。

一、方案论证与比较

键盘显示比较与选择

方案一:

选用独立键盘按键和数码管显示,独立键盘的特点是程序编制简单,但是每个按键占用一条I/0口,当按键较多时,I/O口的利用率不高,适用于所需按键较少的场合。

采用数码管显示时一般采用动态显示,需要用I/O口发送段选与位选数据,若同时用独立键盘,则会造成I/O口的数量不够的问题,又因动态显示利用人眼余晖来实现八位数的动态显示,而且还具有可靠性不高,易烧毁的问题。

方案二:

该方案选用4*4矩阵式键盘和12864液晶。

采用矩阵式键盘可大大提高了I/O口的利用率,而采用液晶显示则可以通过控制单元对液晶提供各种控制命令,如:

清屏、字符闪烁、光标闪烁、显示移位等多种功能,显示内容丰富,并且具有微功耗、体积小,超薄轻巧的特点。

综上所述,由于本设计要用到16个按键,经过两种方案的比较,最终采用4*4矩阵式键盘和液晶屏显示的组合完成键盘显示单元。

微处理器比较与选择

方案一:

选用MSP430系列单片机,拥有强大的处理能力?

MSP430?

系列单片机是一个?

16?

位的单片机,采用了精简指令集(?

RISC?

)结构,具有丰富的寻址方式(7?

种源操作数寻址、?

4?

种目的操作数寻址)、简洁的?

27?

条内核指令以及大量的模拟指令;大量的寄存器以及片内数据存储器都可参加多种运算;还有高效的查表处理指令;有较高的处理速度,在?

8MHz?

晶体驱动下指令周期为?

125ns?

。

这些特点保证了可编制出高效率的源程序。

方案二:

选用P89V51RD2单片机,P89V51RD2单片机的典型特性是它的X2方式选项。

利用该特性可使应用程序以传统的80C51时钟频率(每个机器周期包含12个时钟)或X2方式(每个机器周期包含6个时钟)的时钟频率运行,选择X2方式可在相同时钟频率下获得2倍的吞吐量。

从该特性获益的另一种方法是将时钟频率减半而保持特性不变,这样可以极大地降低电磁干扰(EMI)。

Flash程序存储器支持并行和串行在系统编程(ISP)。

并行编程方式提供了高速的分组编程(页编程)方式,可节省编程成本和上市时间。

综上所述:

根据两个方案不同的特点,综合比较选用方案二中的P89V51RD2单片机作为微处理器单元。

控制逻辑单元选择与比较

方案一:

逻辑控制单元选用CPLD,CPLD属于范围,是一种用户根据各自需要而自行构造逻辑功能的,它具有编程灵活、集成度高、设计开发周期短、适用范围宽、开发工具先进、设计制造成本低、对设计者的硬件经验要求低、标准产品无需测试、保密性强、价格大众化等特点。

方案二:

FPGA它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

CPLD和FPGA的主要区别是他们的系统结构。

CPLD是一个有点限制性的结构。

这个结构由一个或者多个可编辑的结果之和的逻辑组列和一些相对少量的锁定的寄存器。

这样的结果是缺乏编辑灵活性,但是却有可以预计的延迟时间和逻辑单元对连接单元高比率的优点。

而FPGA却是有很多的连接单元,这样虽然让它可以更加灵活的编辑,但是结构却复杂的多。

CPLD和FPGA另外一个区别是大多数的FPGA含有高层次的内置模块(比如和乘法器)和内置的记忆体。

因此一个有关的重别是很多新的FPGA支持完全的或者部分的系统内重新配置。

允许他们的设计随着系统升级或者动态重新配置而改变。

一些FPGA可以让设备的一部分重新编辑而其他部分继续正常运行

综上所述:

方案一结合了方案二的优点而且也节约了实验成本,所以选择方案一来完成控制逻辑单元。

模拟单元中放大器的方案比较:

方案一:

TL084,双列14脚封装,高阻输入结型场效应输入,电压反馈性运算放大器,工作电压等于正负18V静态电流等于,输入偏置电流等于30pA,转换速率等于16V/μs功耗等于680mW,增益带宽等于3MHz,输入失调电压等于2~5mV。

方案二:

TL082是一个双运算放大器,通过小电压信号的变化控制大电压信号。

方案三:

LM324具有电源电压范围宽,静态功耗小,可单电源使用价格低廉等优点。

综上所述:

方案二继承了其他方案的许多的特点,也满足实验要求,因此选择方案二最合适。

电源方案比较:

方案一:

使用自己设计的线性电源,设计时比较麻烦达到预期的目的很是不易,而且产生供电不稳定。

方案二:

使用AC/DC模块。

此模块有良好的隔离、保护作用。

而且也能进行电压变换,也有很强的降低噪生的功能,但是成本较高。

综上所述,为了达到实验目的且考虑节约实验成本和实验资源有限,则选用实验室内的微机电源,虽

然需要持续充电但是仍然能达到实验效果。

二、系统方案描述与论证:

总体设计:

系统工作流程为:

用P89V51RD2单片机作为微处理器,通过键盘输入需要输出的双相信号参数(频率、幅值、相位差、占空比),将相应参数通过液晶屏显示,同时数据输入到CPLD中,CPLD完成了NCO及其他所需功能,根据设计要求生成相应的频率与相位可调的数据,通过比较器与占空比控制字进行比较,产生频率、相位及占空比可调的脉冲信号f(t)。

通过比较器进产生一路占空比可调的矩形波,然后通过低通滤波器生成直流常量用于调节幅值,并通过电子开关改变脉冲信号f(t)的幅值,若想输出正弦波形,则再通过滤波器与运放即可得到。

由单片机P89V51RD2控制输出所需的波形参数,改变CPLD中的相关数据,波形信号可方便、快捷、精确输出。

此方案符合设计题目要求,具有易操作,稳定性强等优点。

方案系统框图如图1-3所示。

图1-3方案系统框图

单元电路设计:

CPLD部分:

12位移位寄存器的SCK、SOI端口和13位译码器的LOAD端口接到单片机上,寄存器的高4位做译码器的地址,低8位做锁存器输出的数据,6位锁存器的输出作为NCO内24位锁存器的信号端,当DLTA[23,0]信号输入到NCO内部时,开始进行循环相加,每计数到2^24时则输出最高位进入下一位进行计数,而下一位则为每2^12来记一次数直到最高位输出,此信号为

FRQA。

Fsys为连接CPLD内部的晶振,此信号连接在14位计数器上,由SET[5,0]来控制信号的脉冲,根据公式Fout=40M/2^12得到Fout的频率为,此频率为基频。

FBASE≈10KHZ。

通过锁存器输出的信号一部分进入了NCO系统内部,另一部分则进入了鉴频器,VA[13,0]和Fout[13,0]进行鉴频比较,从而实现调节占空比即可调节幅度的作用,即输出信号PWMA,同理另一路输出PWMB则也是如此。

FX[11,0]为第二路NCO内部的输出与预置的正弦波的相位差PH[11,0]进行相加进行混频,从而得到信号FRQB。

将PWMA、PWMB、FBASE、FRQA、FRQB五个信号接入到模拟电路中去。

模拟部分:

将矩形波输入到一个低通滤波器中,分别得到正弦波和余弦波,通过开关,将得到基频信号,再一次经过两个低通滤波器,得到频率不同的正弦和余弦信号,而信号再次通过开关得到混频,经过积分电路和低通滤波器,得到想要的正弦波。

其流程图如下:

图1

由于电源产生的电压为-12V--+12V大于电路中所用的电压,因此需要改进。

将电流通过由R1和R2并联的电阻经过电压跟随器得到+5V的电压,在经过一阶放大和反向电压跟随器得到-5V的电压。

图2

将得到的电源接和幅值为5的PWMA信号接到芯片4053上,在VA0输出幅度为的信号。

这是一个占空比可调的信号,经过三阶滤波得到占空比为50%的DCA+,经过跟随得到占空比为25%的DCA-,再次使用多路开关得到幅度可调的方波信号。

此过程为第一级。

将第一级的信号经过三阶低通滤波器进行两次滤波得到相对稳定的正弦波,经过跟随放大得到SA+和SA-两种信号,该信号由频率为基频信号控制,再次经过控制开关得到方波信号。

此过程为第二级。

将第二级得到的信号送入第三级,仍然经过两次三阶低通滤波得到正弦波,而这一级由差频控制其信号。

根据和差化积公式可得,sinA*sinB=-1/2(cos(A+B)-cos(A-B))得到由方波和正弦波的混频,而经过低通滤波器和积分电路,最终得到想要的相位差可调的正弦波。

其两路的频率分别为10~11KHZ和~。

理论计算和分析:

我们的频率设计:

采用36bitNCO,40MHz有源晶振,准确度等于晶振准确度,频率设置采用24bit长,频率上限约为,因滤波器幅频特性限定,选。

根据公式:

40M/2^36=Fx/Δf得到Fxmin=40M/2^36=≈,频率分辨率高于1mHz,实际测量时可以验证我们的幅度设计:

设置PWM脉宽为14bit可调,模拟部分采用正负12V电源,设定最大输出为5V,根据公式:

5/2^14=Vx/Δv

得到Vxmin=5/2^14=≈,保证了有效分辨率优于12bit,且分辨率为1mV,实际测量时可以验证我们的相位设计:

根据控制逻辑单元相位偏移采用12bit,根据公式:

Φx/ΔΦ=360/2^12

得到Φxmin=360/2^12≈o,相位分辨率优于度,实际测量时可以验证。

三、软件设计:

主控制芯片为P89V51RD实现,由于处理器速度较快,所以采用c语言编程方便简单.软件流程图如下:

四、系统测试:

测试所用仪器:

数字多用表34401A,示波器TDS1012,失真度仪GAD2019

幅频特性测试

频率

通道1峰-峰值(V)

通道2峰-峰值(V)

50

100

150

200

300

350

400

450

500

550

600

650

700

750

800

850

900

950

1000

经过测试得到两路正弦波的频率范围1Hz—1KHz,步进值不大于1Hz,频率的准确度不低于%,两路正弦波输出最大幅度不低于3V,分辨率不低于12bit,设定的输出信号电压值在整个频段内,变换量小于5%

相位测试:

两路信号的相位差可在0—359度内可调,设置分辨力可达到度

零点测试:

F=50Hz

AC(mV)

DC(mV)

通道一

通道二

经过测试,两路正弦信号幅度设置为零时,输出噪声未达到5mV.

通过测试使得相位,幅度,频率,零点的指标都得到了提升,2个4053单个成本为,2个082单个成本为,8个免费OPA2227,晶振成本为5,CPLD成本为20

结论

结论:

由于系统架构设计合理,功能电路实现较好,系统性能优良、稳定,较好地达到了题目要求的各项指标。

(1)两路正弦波的频率范围1Hz—,步进值,频率准确度%;

(3)两路正弦波输出最大幅度5V,幅度设置,设置分辨力;

(3)正弦波信号在整个频率设置范围内,波形失真度小于2%;

(4)两路信号的相位差可以在0—359度内可调,设置分辨力度;

(5)所有参数均可程控设置;

(6)微处理器单元与控制逻辑单元信号连线3条。

(7)控制逻辑单元输出给模拟电路单元的信号线5条;

(8)当两路信号频率为1到10间的倍频关系时同步,示波器观测两路波形稳定;

(9)输出信号电压值在整个频段内变换量小于5%;

(10)两路正弦信号幅度设置为零时输出噪声小于5mV;

(11)取消微处理器单元,控制逻辑单元也能实现独立设置特定参数信号的输出;

参考文献

《信号与系统》,ALAN着,西安:

西安交通大学出版社,1997年;

《数字图像处理学》,元秋奇着,北京:

电子工业出版社,2000年;

《模拟电子线路基础》,吴运昌着,广州:

华南理工大学出版社,2004年;

《数字电子技术基础》,阎石着,北京:

高等教育出版社,1997年;

《数据结构与算法》,张晓丽等着,北京:

机械工业出版社,2002年;

《单片机原理及应用》,李建忠着,西安:

西安电子科技大学,2002年;

附录

附录1程序设计

#include<>

;

txt_disp(str_chpf1,0x90);

k=i++;

flag_d=0;

}

elseif(a=='c')

{

if(i!

=0)

{

strcpy(str_chpf1,str_chpf);break;

}

else

{

lcd_gra_clr();lcd_txt_clr();return;

}

}

elseif(a=='e')

{

while(str_chpf1[10]=='.'||str_chpf1[10]=='0'&&flag_d==0)

{

fanchuan(str_chpf1);

if(str_chpf1[10]=='.')

{

fanchuan(str_chpf1);

break;

}

}

if(flag_d)

k=i;

if(i==0&&flag_anjian)

break;

m=jisuan(n1,k);

if(m>1200)/*频率大于1200提示出错*/

{

ET0=1;

TR0=1;

EA=1;

N=80;

strcpy(str_td,str_errf);

a='n';

break;

}

EA=1;TR0=1;ET0=1;str_td[14]=0xa1;str_td[15]=0xcc;N=20;/

f[flag_s]=m;

{

ch_f[0]=suanfa_f(f[0]);

ch_f[1]=suanfa_f(f[1]);

comd1=f[0]/f[1];

comd2=f[1]/f[0];

if(comd1>1)

{

comi1=comd1;

if((comd1-comi1)==0)

ch_f[0]=comi1*ch_f[1];

}

if(comd2>1)

{

comi2=comd2;

if((comd2-comi2)==0)

ch_f[1]=comi2*ch_f[0];

}

}

sendvalue();

/******************************************************************************************

(将频率送给当前操作的通道伪代码)

送频率函数(chf[flag_s])

{

通道=flag_s;

频率值=ch_f[flag_s];

}

******************************************************************************************/

strcpy(str_chpf2,str_chpf1);

break;

}

}break;

case1:

while(i<9)

{txt_disp(str_td,0x80);

Key_scan(&a);

if(a=='u'||a=='d')

{

if(a=='d')

flag_ForVorP[flag_s]=(flag_ForVorP[flag_s]+1)%3;

else

flag_ForVorP[flag_s]=(flag_ForVorP[flag_s]+2)%3;

n1[0]=n1[1]=n1[2]=n1[3]=n1[4]=n1[5]=n1[6]=n1[7]=0;

strcpy(str_chpf1,str_chpf2);

strcpy(str_chpv1,str_chpv2);

strcpy(str_chp1,str_chp2);

txt_disp(str_td,0x80);

txt_disp(str_chpf1,0x90);

txt_disp(str_chpv1,0x88);

txt_disp(str_chp1,0x98);

i=0;

break;

}

elseif(a=='m')

{

return;

}

elseif(a>=0&&a<=9&&i<8)

{

flag_anjian=0;

if(i==0)

{

strcpy(str_chpv1,str_chpv);

switch(flag_ForVorP[flag_s])

{

case0:

str_chpf1[1]=0x1a;str_chpv1[1]='';str_chp1[1]='';break;

case1:

str_chpf1[1]='';str_chpv1[1]=0x1a;str_chp1[1]='';break;

case2:

str_chpf1[1]='';str_chpv1[1]='';str_chp1[1]=0x1a;break;

}

str_chpv1[10]='';

}

if(i==0&&a==0)

{str_chpv1[10]='0';txt_disp(str_chpv1,0x88);continue;}

if(!

flag_d&&i-k>3)

{

continue;

}

elseif(i!

=0)

chuanwei(str_chpv1);

str_chpv1[10]=a+48;

n1[i++]=a;

txt_disp(str_chpv1,0x88);

}

elseif(a=='b'&&flag_d)

{

if(i==0)

{

strcpy(str_chpv1,str_chpv);

switch(flag_ForVorP[flag_s])

{

case0:

str_chpf1[1]=0x1a;str_chpv1[1]='';str_chp1[1]='';break;

case1:

str_chpf1[1]='';str_chpv1[1]=0x1a;str_chp1[1]='';break;

case2:

str_chpf1[1]='';str_chpv1[1]='';str_chp1[1]=0x1a;break;

}

str_chpv1[10]='0';i++;

}

chuanwei(str_chpv1);

str_chpv1[10]='.';

txt_disp(str_chpv1,0x88);

k=i++;

flag_d=0;

}

elseif(a=='c')

{

if(i!

=0)

{

strcpy(str_chpv1,str_chpv);break;

}

else

{

lcd_gra_clr();lcd_txt_clr();return;

}

}

elseif(a=='e')

{

while(str_chpv1[10]=='.'||str_chpv1[10]=='0'&&flag_d==0)

{

fanchuan(str_chpv1);

if(str_chpv1[10]=='.')

{

fanchuan(str_chpv1);

break;

}

}

if(flag_d)

k=i;

if(i==0&&flag_anjian)

break;

m=jisuan(n1,k);

if(m>5)/*幅度大于5V提示错误*/

{

ET0=1;

TR0=1;

EA=1;

N=80;

strcpy(str_td,str_errv);

a='n';

break;

}

EA=1;TR0=1;ET0=1;str_td[14]=0xa1;str_td[15]=0xcc;N=20;

switch(flag_s)

{

case0:

ch_v[0]=suanfa_v0(m);break;

case1:

ch_v[1]=suanfa_