计算机系统结构教程课后解答文档格式.docx

《计算机系统结构教程课后解答文档格式.docx》由会员分享,可在线阅读,更多相关《计算机系统结构教程课后解答文档格式.docx(27页珍藏版)》请在冰点文库上搜索。

改进前:

CPI=5×

30%+1.25×

(1-30%)=2.375

设除FPSQR外其余指令的平均CPI为X

则2.375=20×

4%+(1-4%)X,解出X=1.640625

方案1:

CPI1=3×

4%+1.640625×

(1-4%)=1.695

方案2:

CPI2=3×

(1-30%)=1.775

2.11

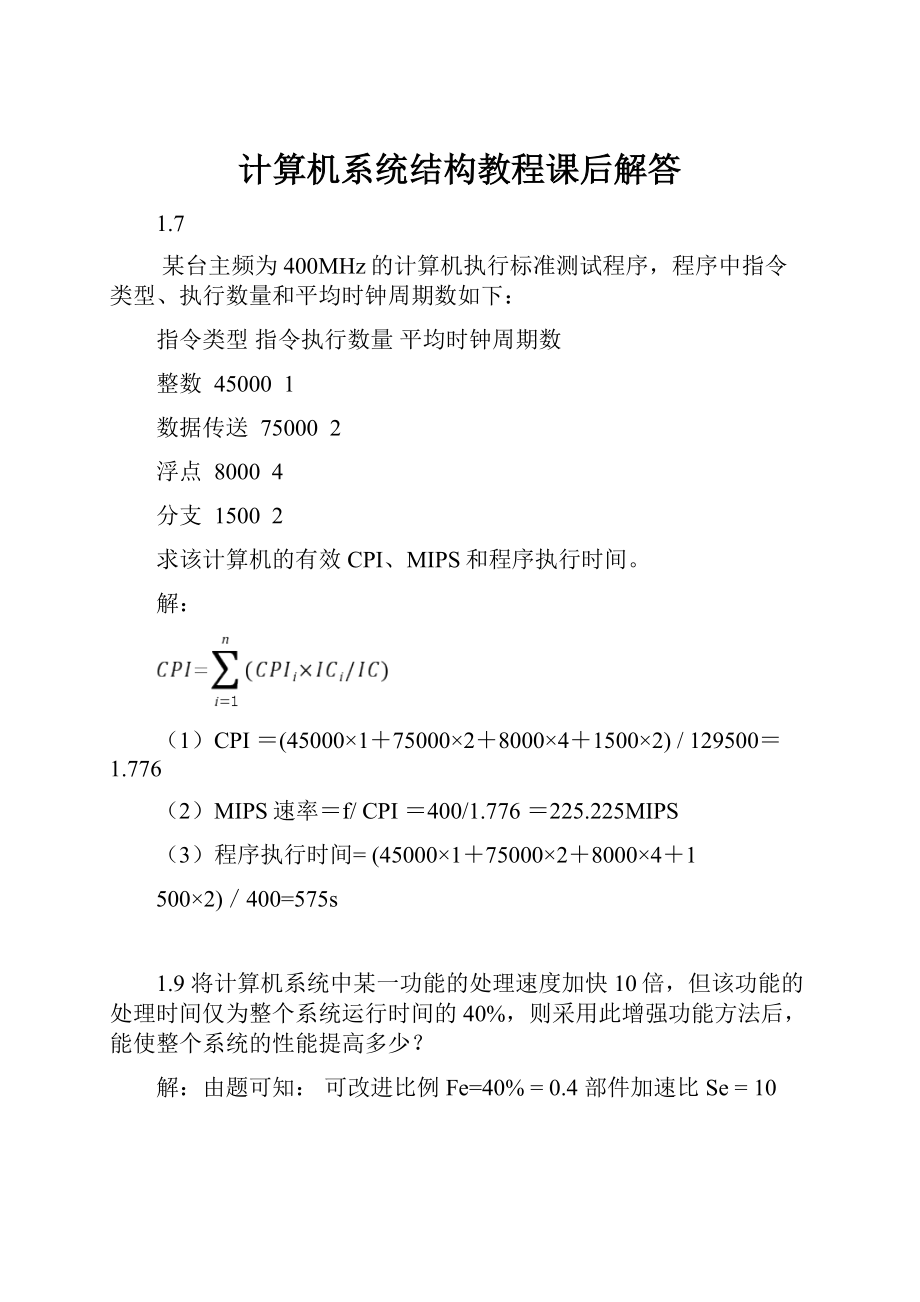

指令

频度pi

操作码使用哈夫曼编码

操作码长度li

ADD

0.43

0

1

CLA

0.22

10

2

SUB

0.13

110

3

JMP

0.07

11100

5

JOM

0.06

11101

5

STO

0.05

11110

CIL

0.02

111110

6

SHR

0.01

1111110

7

STP

1111111

L=

=0.43x1+0.22x2+0.13x3+0.07x5+0.06x5+0.05x5+0.02x6+0.01x7+0.01x7

=2.42

2.12.

二地址指令的结构是(4位操作码OP),(6位地址码A1),(6位地址码A2)。

一地址指令的结构是(10位操作码OP),(6位地址码A)。

二地址指令,最多共16条二地址指令。

每少一条二地址指令,则多26条一地址指令,

所以一地址指令最多有(16-A)*26条

3.5在一台单流水线多操作部件的处理机上执行下面的程序,每条指令的取指令、指令译码需要一个时钟周期,MOVE、ADD和MUL操作分别需要2个、3个和4个时钟周期,每个操作都在第一个时钟周期从通用寄存器中读操作数,在最后一个时钟周期把运算结果写到通用寄存器中。

k:

MOVER1,R0;

R1←(R0)

k+1:

MULR0,R2,R1;

R0←(R2)×

(R1)

k+2:

ADDR0,R2,R3;

R0←(R2)+(R3)

画出指令执行过程的流水线时空图,并计算完成这3条指令共需要多少个时钟周期?

在程序实际执行过程中,二种数据相关会引起流水线停顿。

一是“先写后读”相关,k指令对R1的写在程序执行开始后的第四个时钟;

k+1指令对R1的读对指令本身是第三个时钟,但k+1指令比k指令晚一个时钟进入流水线,则在程序执行开始后的第四个时钟要读R1。

不能在同一时钟周期内读写同一寄存器,因此k+1指令应推迟一个时钟进入流水线,产生了流水线停顿。

二是“写—写”相关,k+1指令对R0的写对指令本身是第六个时钟,而要求该指令进入流水线应在程序执行开始后的第三个时钟,所以对R0的写是在程序执行开始后的第八个时钟。

k+2指令对R0的写对指令本身是第五个时钟,而k+2指令比k+1指令晚一个时钟进入流水线,则在程序执行开始后的第四个时钟,所以对R0的写是在程序执行开始后的第八个时钟。

不能在同一时钟周期内写写同一寄存器,因此k+2指令应推迟一个时钟进入流水线,产生了流水线停顿。

另外,可分析“先读后写”相关不会产生流水线的停顿。

该指令流水线由六个功能段取指、译码、取数、运一、运二和存数等组成,则程序指令执行过程的流水线时空图如下图所示。

若3条指令顺序流动,共需要9个时钟周期。

空间

存数K存数K+1存数K+2存数

运二K+1运二

运一K+1运一K+2运一

取数K取数K+1取数K+2取数

译码K译码K+1译码K+2译码

取指K取指K+1取指K+2取指时间

0123456789

3.6有一指令流水线如下所示

(1)求连续输入10条指令,该流水线的实际吞吐率和效率;

(2)该流水线的“瓶颈”在哪一段?

请采取两种不同的措施消除此“瓶颈”。

对于你所给出的两种新的流水线,连续输入10条指令时,其实际吞吐率和效率各是多少?

(1)

(2)瓶颈在3、4段。

⏹变成八级流水线(细分)

⏹重复设置部件

3.7有一个流水线由4段组成,其中每当流经第3段时,总要在该段循环一次,然后才能流到第4段。

如果每段经过一次所需要的时间都是

,问:

(1)当在流水线的输入端连续地每

时间输入任务时,该流水线会发生什么情况?

(2)此流水线的最大吞吐率为多少?

如果每

输入一个任务,连续处理10个任务时的实际吞吐率和效率是多少?

(3)当每段时间不变时,如何提高该流水线的吞吐率?

仍连续处理10个任务时,其吞吐率提高多少?

(1)会发生流水线阻塞情况。

第1个任务

S1

S2

S3

S4

第2个任务

stall

第3个任务

第4个任务

(2)

(3)重复设置部件

吞吐率提高倍数=

=1.64

3.8有一条静态多功能流水线由5段组成,加法用1、3、4、5段,乘法用1、2、5段,第3段的时间为2△t,其余各段的时间均为△t,而且流水线的输出可以直接返回输入端或暂存于相应的流水寄存器中。

现要在该流水线上计算,画出其时空图,并计算其吞吐率、加速比和效率。

首先,应选择适合于流水线工作的算法。

对于本题,应先计算A1+B1、A2+B2、A3+B3和A4+B4;

再计算(A1+B1)×

(A2+B2)和(A3+B3)×

(A4+B4);

然后求总的结果。

其次,画出完成该计算的时空图,如图所示,图中阴影部分表示该段在工作。

由图可见,它在18个△t时间中,给出了7个结果。

所以吞吐率为:

如果不用流水线,由于一次求积需3△t,一次求和需5△t,则产生上述7个结果共需(4×

5+3×

3)△t=29△t。

所以加速比为:

该流水线的效率可由阴影区的面积和5个段总时空区的面积的比值求得:

3.8有一条动态多功能流水线由5段组成,加法用1、3、4、5段,乘法用1、2、5段,第2段的时间为2△t,其余各段时间均为△t,而且流水线的输出可以直接返回输入端或暂存于相应的流水寄存器中。

若在该流水线上计算:

试计算其吞吐率、加速比和效率。

解

如果不用流水线,由于一次求积需4△t,一次求和需4△t,则产生上述7个结果共需(4×

4+3×

4)△t=28△t。

4.5在CRAY-1机器上,按照链接方式执行下述4条向量指令(括号中给出了相应功能部件的执行时间),如果向量寄存器和功能部件之间的数据传送需要1拍,试求此链接流水线的通过时间是多少拍?

如果向量长度为64,则需多少拍才能得到全部结果?

V0←存储器(从存储器中取数:

7拍)

V2←V0+V1(向量加:

3拍)

V3←V2<

A3(按(A3)左移:

4拍)

V5←V3∧V4(向量逻辑乘:

2拍)

通过时间就是每条向量指令的第一个操作数执行完毕需要的时间,也就是各功能流水线由空到满的时间,在流水线充满之后,向量中后继操作数继续以流水方式执行,直到整组向量执行完毕。

T通过=(1+7+1)+(1+3+1)+(1+4+1)+(1+2+1)=24(拍)

T总共=T通过+(64-1)=24+63=87拍

4.6T通过=(1+7+1)+(1+3+1)+(1+5+1)+(1+2+1)+(1+7+1)=34(拍)

T总共=T通过+(64-1)=63+34=97拍

4.7某机有16个向量寄存器,其中V0~V5中分别放有向量A、B、C、D、E、F,向量长度均为8,向量各元素均为浮点数;

处理部件采用二个单功能流水线,加法功能部件时间为2拍,乘法功能部件时间为3拍。

用类似Cray

1的链接技术,先计算(A+B)*C,在流水线不停流的情况下,接着计算(D+E)*F。

解答:

(1)

(A+B)*C

可用以下2条指令完成:

V0←A+B

V1←V0*C

流水线流过时间为(1+2+1)

+

(1+3+1)

=

9拍

(2)

实际吞吐率为

=26.7MFLOPS

4.8

分段开采

LVV1,Rb;

取向量B

MULTVSV2,V1,Fs;

向量和标量相乘

SVRa,V2;

存向量

三条指令三个编队

T200=4x(15+Tstart)+200x3

=660+(4xTstart)

Tstart=12+7+12=31

T200=660+4x31=784

4.9

CrayY-MP/8的峰值性能为:

R∞=(1+1)×

8/(6x10-3)=16=2667MFLOPS

5.8.假设有一条长流水线,仅仅对条件转移指令使用分支目标缓冲。

假设分支预测错误的开销为4个时钟周期,缓冲不命中的开销为3个时钟周期。

假设:

命中率为90%,预测精度为90%,分支频率为15%,没有分支的基本CPI为1。

①求程序执行的CPI。

②相对于采用固定的2个时钟周期延迟的分支处理,哪种方法程序执行速度更快?

(1)程序执行的CPI=没有分支的基本CPI

(1)+分支带来的额外开销

分支带来的额外开销是指在分支指令中,缓冲命中但预测错误带来的开销与缓冲没有命中带来的开销之和。

分支带来的额外开销=15%*(90%命中×

10%预测错误×

4+10%不命中×

3)=0.099

所以,程序执行的CPI=1+0.099=1.099

(2)采用固定的2个时钟周期延迟的分支处理CPI=1+15%×

2=1.3

由

(1)

(2)可知分支目标缓冲方法执行速度快。

5.9.假设分支目标缓冲的命中率为90%,程序中无条件转移指令的比例为5%,没有无条件转移指令的程序CPI值为1。

假设分支目标缓冲中包含分支目标指令,允许无条件转移指令进入分支目标缓冲,则程序的CPI值为多少?

假设原来的CPI=1.1

参考答案:

解:

设每条无条件转移指令的延迟为x,则有:

1+5%×

x=1.1

x=2

当分支目标缓冲命中时,无条件转移指令的延迟为0。

所以程序的CPI=1+2×

5%×

(1-90%)=1.01

7.8.假设对指令Cache的访问占全部访问的75%;

而对数据Cache的访问占全部访问的25%。

Cache的命中时间为1个时钟周期,不命中开销为50个时钟周期,在混合Cache中一次load或store操作访问Cache的命中时间都要增加一个时钟周期,32KB的指令Cache的不命中率为0.15%,32KB的数据Cache的不命中率为3.77%,64KB的混合Cache的不命中率为0.95%。

又假设采用写直达策略,且有一个写缓冲器,并且忽略写缓冲器引起的等待。

试问指令Cache和数据Cache容量均为32KB的分离Cache和容量为64KB的混合Cache相比,哪种Cache的不命中率更低?

两种情况下平均访存时间各是多少?

(1)根据题意,约75%的访存为取指令,25%的访存为数据。

因此,分离Cache的总体不命中率为:

(75%×

0.15%)+(25%×

3.77%)=1.055%;

容量为64KB的混合Cache的不命中率略低一些,只有0.95%。

(2)平均访存时间公式可以分为指令访问和数据访问两部分:

平均访存时间=指令所占的百分比×

(读命中时间+读不命中率×

不命中开销)+数据所占的百分比×

(数据命中时间+数据不命中率×

不命中开销)

所以,两种结构的平均访存时间分别为:

分离Cache的平均访存时间=75%×

(1+0.15%×

50)+

25%×

(1+3.77%×

50)

=(75%×

1.075)+(25%×

2.885)=1.5275

因为混合Cache读数据的都要增加1个时钟周期

所以混合Cache的平均访存时间=75%×

(1+0.95%×

(1+1+0.95%×

1.475)+(25%×

2.475)=1.725

因此,尽管分离Cache的实际不命中率比混合Cache的高,但其平均访存时间反而较低。

分离Cache提供了两个端口,消除了结构相关。

7.9假设在3000次访存中,第一级Cache不命中110次,第二级Cache不命中55次。

试问:

在这种情况下,该Cache系统的局部不命中率和全局不命中率各是多少?

局部不命中率=该级Cache的不命中次数/到达该级Cache的访存次数。

局部不命中率L1=110/3000=0.0367,不命中率L2=55/110=0.50。

全局不命中率L1=不命中率L1=0.0367,

全局不命中率L2=不命中率L1×

不命中率L2=0.0367×

0.50=0.0184。

7.10给定以下的假设,试计算直接映象Cache和两路组相联Cache的平均访问时间以及CPU的性能。

由计算结果能得出什么结论?

(1)理想Cache情况下的CPI为2.0,时钟周期为2ns,平均每条指令访存1.2次;

(2)两者Cache容量均为64KB,块大小都是32字节;

(3)组相联Cache中的多路选择器使CPU的时钟周期增加了10%;

(4)这两种Cache的不命中开销都是80ns;

(5)命中时间为1个时钟周期;

(6)64KB直接映象Cache的不命中率为1.4%,64KB两路组相联Cache的不命中率为1.0%。

平均访问时间=命中时间+不命中率×

不命中开销

平均访问时间1-路=2.0+1.4%*80=3.12ns

平均访问时间2-路=2.0*(1+10%)+1.0%*80=3.0ns

两路组相联的平均访问时间比较低

CPUtime=(CPU执行+存储等待周期)*时钟周期

CPUtime=IC(CPI执行+总不命中次数/指令总数*不命中开销)*时钟周期

=IC((CPI执行*时钟周期)+(每条指令的访存次数*不命中率*不命中开销*时钟周期))

CPUtime1-way=IC(2.0*2+1.2*0.014*80)=5.344IC

CPUtime2-way=IC(2.2*2+1.2*0.01*80)=5.36IC

相对性能比:

5.36/5.344=1.003

直接映象cache的访问速度比两路组相联cache要快1.04倍,而两路组相联Cache的平均性能比直接映象cache要高1.003倍。

因此这里选择两路组相联

7.14假设一台计算机具有以下特性:

(1)95%的访存在Cache中命中;

(2)块大小为两个字,且不命中时整个块被调入;

(3)CPU发出访存请求的速率为109字/s;

(4)25%的访存为写访问;

(5)存储器的最大流量为109字/s(包括读和写);

(6)主存每次只能读或写一个字;

(7)在任何时候,Cache中有30%的块被修改过;

(8)写不命中时,Cache采用按写分配法。

现欲给该计算机增添一台外设,为此首先想知道主存的频带已用了多少。

试对于以下两种情况计算主存频带的平均使用比例。

(1)写直达Cache;

(2)写回法Cache。

采用按写分配

(1)写直达cache访问命中,有两种情况:

读命中,不访问主存;

写命中,更新cache和主存,访问主存一次。

访问不命中,有两种情况:

读不命中,将主存中的块调入cache中,访问主存两次;

写不命中,将要写的块调入cache,访问主存两次,再将修改的数据写入cache和主存,访问主存一次,共三次。

上述分析如下表所示。

访问命中

访问类型

频率

访存次数

Y

读

95%*75%=71.3%

写

95%*25%=23.8%

1

N

5%*75%=3.8%

2

5%*25%=1.3%

一次访存请求最后真正的平均访存次数=(71.3%*0)+(23.8%*1)+(3.8%*2)+(1.3%*3)=0.35

已用带宽=35.0%

(2)写回法cache访问命中,有两种情况:

写命中,不访问主存。

采用写回法,只有当修改的cache块被换出时,才写入主存;

访问不命中,有一个块将被换出,这也有两种情况:

如果被替换的块没有修改过,将主存中的块调入cache块中,访问主存两次;

如果被替换的块修改过,则首先将修改的块写入主存,需要访问主存两次;

然后将主存中的块调入cache块中,需要访问主存两次,共四次访问主存。

块为脏

95%*70%=66.5%

95%*30%=28.5%

5%*70%=3.5%

5%*30%=1.5%

4

所以:

一次访存请求最后真正的平均访存次数=

66.5%*0+28.5%*0+3.5%*2+1.5%*4=0.13

已用带宽=13%

9.2

(1)由Cube3(X3X2X1X0)=X3X2X1X0

Cube3(0110)=1110即处理器14连接到处理器6

令Cube3(X3X2X1X0)=0110,得X3X2X1X0=1110

所以处理器14和6双向互连

(2)由

=(0101)即处理器5连接到处理器6

令

=(0110)得X3X2X1X0=0011

所以处理器5和6连,3和5连

(3)由

=(0110)即处理器6连接到处理器6

所以处理器6和6双向互连

(4)由

=(1010)即处理器10连接到处理器6

=(0110)得X3X2X1X0=1010

所以处理器6和10双向互连

9.9

(a)由Cube2(X4X3X2X1X0)=X3X3X2X1X0

Cube2(12)=Cube2(01100)=01000即处理器8连接到处理器12

(b)由

即处理器16连接到处理器

(C)由

即处理器4连接到处理器28

(d)

即处理器9连接到处理器8

(e)

即处理器7连接到处理器28

(2)2n个节点的直径为2n-1,从5号到7号,最短经过6步

00101001000100001001100101001100111

(3)循环移数网络的节点度d=2n-1,直径为n/2

网络直径是3,节点度是9,与2号最远的是13,15,21,23号处理器

9.11

8

9

A

B

C

D

E

F

4组4元

2组8元

1组16元

0000-1011

Cube0+Cube1+Cube3

10.6.一台32个处理器的计算机,对远程存储器访问时间为400ns。

除了通信以外,假设计算中的访问均命中局部存储器。

当发出一个远程请求时,本处理器挂起。

处理器时钟时间为1GHz,如果指令基本的IPC为2(设所有访存均命中Cache),求在没有远程访问的状态下与有0.2%的指令需要远程访问的状态下,前者比后者快多少?

解:

没有远程访问时,机器的CPI为1/基本IPC=1/2=0.5

有0.2%远程访问的机器的实际CPI为

CPI=基本CPI+远程访问率×

远程访问开销

=0.5+0.2%×

远程访问开销为:

远程访问时间/时钟周期时间=400ns/1ns=400个时钟周期

∴CPI=0.5+0.2%×

400=1.3

因此在没有远程访问的情况下的计算机速度是有0.2%远程访问的计算机速度的1.3/0.5=2.6倍。