EDA汇总Verilog HDL编程Word文档下载推荐.docx

《EDA汇总Verilog HDL编程Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《EDA汇总Verilog HDL编程Word文档下载推荐.docx(16页珍藏版)》请在冰点文库上搜索。

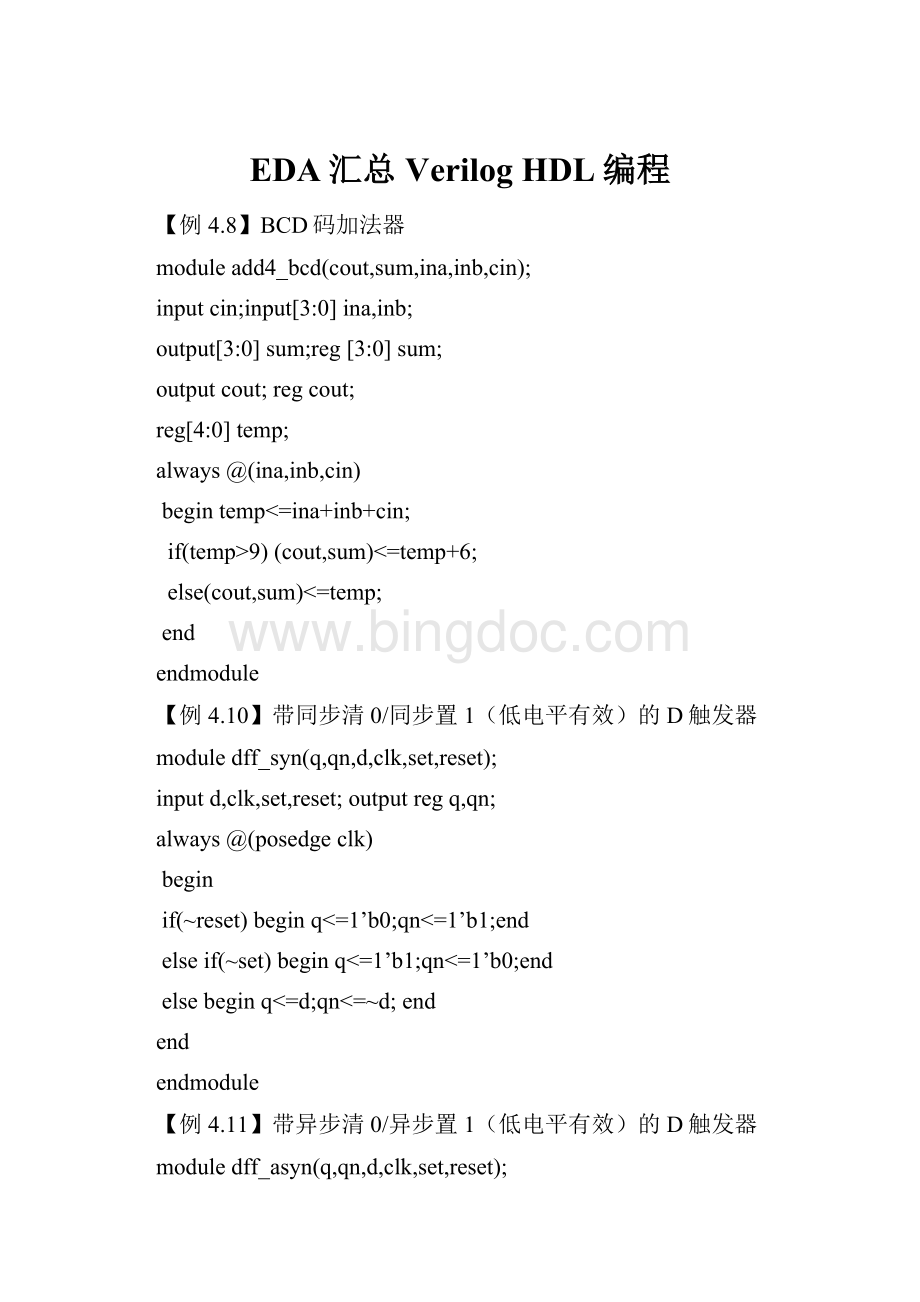

moduledff_asyn(q,qn,d,clk,set,reset);

always@(posedgeclkornegedgesetornegedgereset)

【例4.13】4位计数器的仿真代码

`timescale1ns/1ns

`include“count4.v”

modulecoun4_tp;

regclk,reset;

wire[3:

0]out;

parameterDELY=100;

count4mycount(out,reset,clk);

always#(DELY/2)clk=~clk;

initial

beginclk=0;

reset=0;

#DELYreset=1;

#DELYreset=0;

#(DELY*20)$finish;

initial$monitor($time,,”clk=%dreset=%dout=%d,clk,reset,out);

【例4.14】带同步复位的4位模10BCD码计数器

modulecount10(cout,qout,reset,clk);

inputreset,clk;

outputreg[3:

0]qout;

if(reset)qout<

=0;

elseif(qout<

9)qout<

=qout+1;

elseqout<

assigncout=(qout==9)?

1:

0;

【例6.1】用case语句描述的4选1数据选择器

modulemux4_1(out,in0,in1,in2,in3,se1);

inputin0,in1,in2,in3;

input[1:

0]se1;

outputregout;

always@(in0orin1orin2orin3orse1)

case(se1)

2’b00:

out=in0;

2’b01:

out=in1;

2’b10:

out=in2;

2’b11:

out=in3;

default:

out=2’box;

endcase

【例6.2】同步置数、同步清零的计数器

modulecount(out,data,load,reset,clk);

inputload,clk,reset;

input[7:

0]data;

outputreg[7:

if(!

reset)out<

=8’h00;

elseif(load)out=data;

elseout<

=out+1;

【例6.4】用initial过程语句对测试变量赋值

’timescale1ns/1ns

moduletest;

rega,b.c;

initialbegina=0;

b=1;

c=0;

#50a=1;

b=0;

#50a=0;

c1;

#50b=1;

#50b=0;

#50$finish;

【例6.5】用begin-end串行块产生信号波形

’timescale10ns/1ns

modulewave1;

parameterCYCLE=10;

regwave;

beginwave=0;

#(CYCLE/2)wave=1;

#(CYCLE/2)wave=0;

#(CYCLE/2)$stop;

initial$monitor($time,,,”wave=%b”,wave);

【例6.15】模为60的8421BCD码加法计数器

modulecount60(qout,cout,data,load,reset,clk);

outputcout;

if(reset)qout<

elseif(load)qout<

=data;

elsebegin

if(qout[3:

0]==9)

beginqout[3:

0]<

if(qout[7:

4]==5)qout[7:

4]<

elseqout[7:

=qout[7:

4]+1;

end

elseqout[3:

=qout[3:

0]+1;

assigncout=(qout==8’d59)?

【例6.17】BCD码——7段数码管译码器

moduledecode4_7(a,b,c,d,e,f,g,D3,D2,D1,D0);

inputD3,D2,D1,D0;

outputrega,b,c,d,e,f,g;

always@(*)

case({D3,D2,D1,D0})

4’d0:

{a,b,c,d,e,f,g}=7’b1111110;

4’d1:

{a,b,c,d,e,f,g}=7’b0110000;

4’d2:

{a,b,c,d,e,f,g}=7’b1101101;

4’d3:

{a,b,c,d,e,f,g}=7’b1111001;

4’d4:

{a,b,c,d,e,f,g}=7’b0110011;

4’d5:

{a,b,c,d,e,f,g}=7’b1011011;

4’d6:

{a,b,c,d,e,f,g}=7’b1011111;

4’d7:

{a,b,c,d,e,f,g}=7’b1110000;

4’d8:

{a,b,c,d,e,f,g}=7’b1111111;

4’d9:

{a,b,c,d,e,f,g}=7’b1111011;

default:

endcase

【例6.18】用case语句描述的下降沿触发的JK触发器

modulejk_ff(clk,j,k,q);

inputclk,j,k;

outputregq;

always@(negedgeclk)

case({j,k})

2’b00:

q<

=q;

2’b01:

2’b10:

2’b11:

=~q;

endcase

例6.36用ifelse描述的模12分频器

modulefdivi12(teset,clkin,clkout,qout);

inputreset,clkin:

outputregclkout;

outputreg[4:

always@(posedgeclkin)

if(!

reset)

begin

clkout<

qout<

=0;

end

elesbegin

if(qout==5)

qout<

clkout<

=~clkout:

例6.37模12分频器

reset)qout<

11)qout<

+qout+1;

reset)clkout<

elseif(qout==11)clkout<

=1;

elseclkout<

例6.38.模12分频器

assignclkout=(qout==11)?

:

0;

例7.2用case语句描述的4选1mux

modulemux4_1b(out,in1,in2,in3,in4,s0,s1);

inputin1,in2,in3,in4,s0,s1;

outputregout;

case({s0,s1})

2'

b00:

out=in1;

b01:

out=in2;

b10:

out=in3;

b11:

out=in4;

out=2'

bx;

例8.1用状态机设计模5计数器

modulefam(clk,clr,z,qout);

inputclk,clr;

outputregz;

outputreg[2:

always@(posedgeclkorposedgeclr)

beginif(clr)qout<

elsecase(qout)

3'

b000:

=3'

b001;

b001:

b010;

b010:

b011;

b011:

b100;

b100:

b000;

always@(qout)

begincase(qout)

z=1'

b1;

b0;

例8.2用状态机设计模5计数器(单过程描述)。

modulefsm1(clk,clr,z,qout);

beginqout<

例8.3"

101"

序列检测器的描述(cs,ns,ol各用一个过程描述)

modulefsm1_set101(clk,clr,x,z);

inputclk,clr,x;

reg[10]state,next_state;

parameters0=2'

b00,s1=2'

b01,s2=2'

b11,s3=2'

b10;

/*状态编码,采用格雷编码方式*/

always@(posedgeclkorposedgeclr)

beginif(clr)state<

=s0;

elsestate<

=next_state;

always@(stateorx)

begin

case(state)

s0:

beginif(x)next_state<

=s1;

elsenext_state<

s1:

=s2;

s2:

=s3;

next_state<

endcase

always@(state)

begincase(state)

s3=:

z=1'

endmodule

例8.4采用两个过程对"

序列检测器进行描述(cs+ns,ol双过程描述)

modulefsm2_set101(clk,clr,x,z);

reg[10]state;

b01,s1=2'

=state;

beginif(x)state<

elsestate<

state<

s3:

endmodule

例8.5"

序列检测器(CS,NS+OL双过程描述)。

modulefsm3_seq101(clk,clr,x,z);

reg[1:

0]state,next_state;

parameterS0=2'

b00,S1=2'

b01,S2=2'

b11,S3=2'

=S0;

always@(stateorx)

S0:

beginif(x)beginnext_state<

=S1;

elsebeginnext_state<

S1:

=S2;

S2:

=S3;

S3:

beginnext_state<

例8.6"

序列检测器(CS+NS+OL单过程描述)。

modulefsm4_seq101(clk,clr,x,z);

0]state;

elsecase(state)

beginif(x)beginstate<

elsebeginstate<

beginstate<

例8.7"

1111"

序列检测器的Verilog描述(单过程描述CS+NS+OL)

modulefsm_seq1111(x,z,clk,reset);

inputx,clk,reset;

outputregz;

parameters0='

d0,s1='

d1,s2='

d2,s3='

d3,s4='

d4;

beginif(reset)beginstate<

z<

elsecasex(state)

beginif(x==0)beginstate<

z<

elsebeginstate<

s3:

=s4;

s4:

例8.10用有限状态机设计除法电路

moduledivision(a,b,clk,result,yu);

0]a,b;

0]result,yu;

inputclk;

reg[1:

reg[3:

0]m,n;

s0:

beginif(a>

=b)beginn<

=a-b;

m<

=4'

b0001;

elsebeginm<

b0000;

n<

=a;

state<

s1:

beginif(n>

=b)beginm<

=m+1;

n<

=n-b;

s2:

beginresult<

=m;

yu<

=n;

default: