8X8LED点阵数字显示驱动电路设计.docx

《8X8LED点阵数字显示驱动电路设计.docx》由会员分享,可在线阅读,更多相关《8X8LED点阵数字显示驱动电路设计.docx(36页珍藏版)》请在冰点文库上搜索。

8X8LED点阵数字显示驱动电路设计

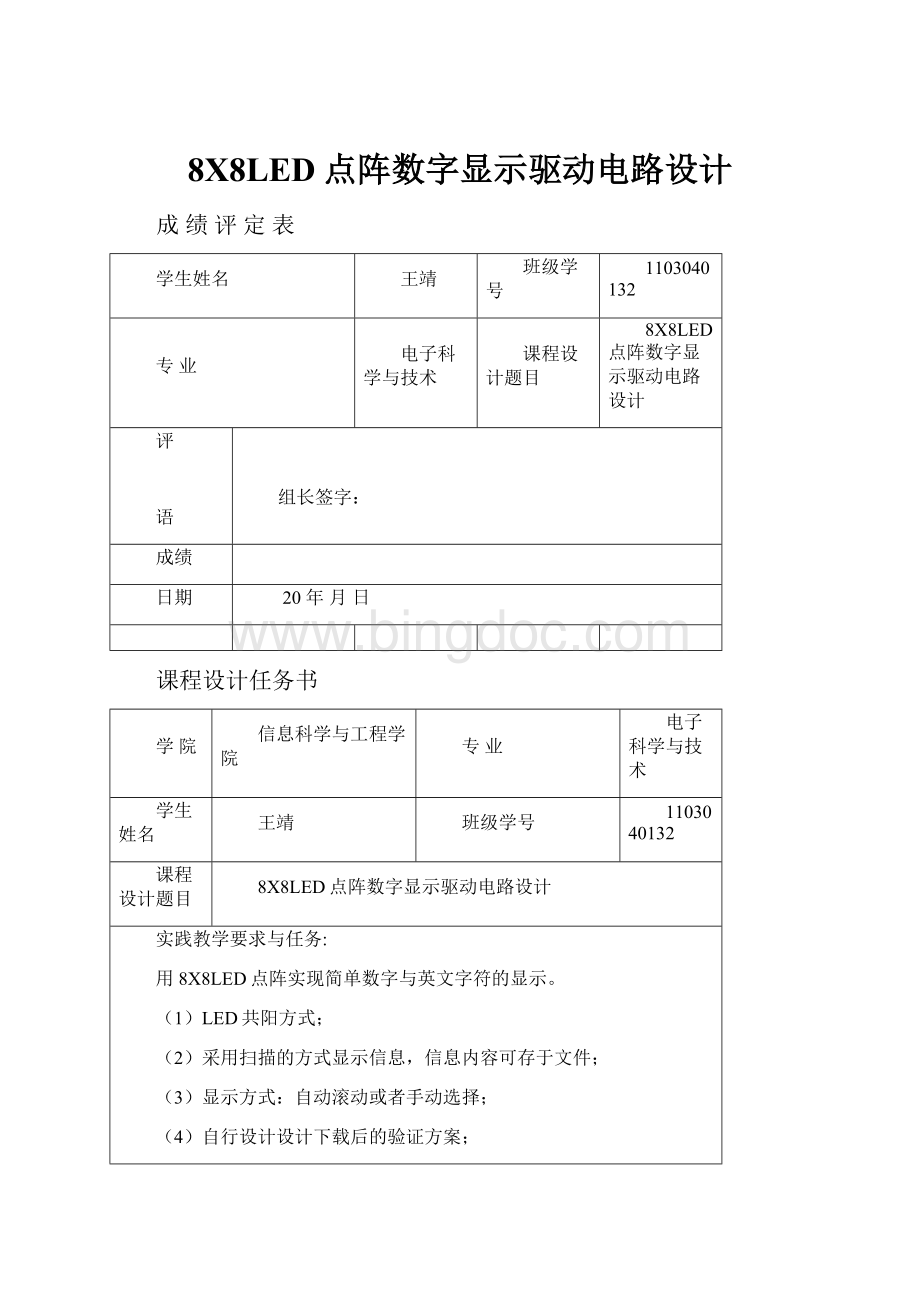

成绩评定表

学生姓名

王靖

班级学号

1103040132

专业

电子科学与技术

课程设计题目

8X8LED点阵数字显示驱动电路设计

评

语

组长签字:

成绩

日期

20年月日

课程设计任务书

学院

信息科学与工程学院

专业

电子科学与技术

学生姓名

王靖

班级学号

1103040132

课程设计题目

8X8LED点阵数字显示驱动电路设计

实践教学要求与任务:

用8X8LED点阵实现简单数字与英文字符的显示。

(1)LED共阳方式;

(2)采用扫描的方式显示信息,信息内容可存于文件;

(3)显示方式:

自动滚动或者手动选择;

(4)自行设计设计下载后的验证方案;

(5)完成全部流程:

设计文档、模块设计、代码输入、功能仿真、约束与综合、布局布线、下载验证等。

工作计划与进度安排:

本设计持续两周,其中最后一天为答辩时间。

第1-2天:

讲解题目,准备参考资料,检查、调试实验软硬件,进入设计环境,开始设计方案和验证方案的准备;

第3-5天:

完成设计与验证方案,经指导老师验收后进入模块电路设计(验收设计文档);

第6-7天:

完成模块电路设计,进行代码输入,并完成代码的仿真(验收代码与仿真结果);

第8-9天:

约束设计、实现、下载验证(验收验证实现);

第10天:

修正设计、整理设计资料,验收合格后进行答辩。

指导教师:

201年月日

专业负责人:

201年月日

学院教学副院长:

201年月日

摘要

8X8LED点阵数字显示驱动电路就是简单地将要显示的信息进行编码后,输出相应的显示和扫描信号连接到点阵上显示。

本文详细介绍了如何用FPGA在8X8LED点阵显示方案设计的过程,并在此基础上将整体电路分为ROM、数据编码、选择显示、扫描产生等主要功能块。

整体过程采用VerilogHDL语言对电路进行功能模块的逻辑设计,然后在Modelsim上进行功能仿真,接着在QuartusII进行逻辑综合与管脚锁定,最后适配下载到Altare公司的CycloneII芯片的EP2C5T144C8上进行验证。

在此过程中,顺利的建立了激励文件和测试平台,功能和时序的仿真,完成了对点阵显示的验证,从而保证了所设计电路的可行性和准确性。

关键词VerilogHDL;FPGA;仿真;综合;验证

引言

FPGA是以硬件描述语言(Verilog或VHDL)所完成的电路设计,可以经过简单的综合与布局,快速的烧录至FPGA上进行测试,是现代IC设计验证的技术主流。

这些可编辑元件可以被用来实现一些基本的逻辑门电路(比如AND、OR、XOR、NOT)或者更复杂一些的组合功能比如解码器或数学方程式。

在大多数的FPGA里面,这些可编辑的元件里也包含记忆元件例如触发器(Flip-flop)或者其他更加完整的记忆块。

系统设计师可以根据需要通过可编辑的连接把FPGA内部的逻辑块连接起来,就好像一个电路试验板被放在了一个芯片里。

一个出厂后的成品FPGA的逻辑块和连接可以按照设计者而改变,所以FPGA可以完成所需要的逻辑功能。

本设计就是通过对8X8点阵驱动电路的设计,来更熟悉地对FPGA进行学习和掌握。

本设计方案是在CycloneII芯片的EP2C5T144C8上实现验证,CycloneII芯片是Altera公司的2004年推出的新款FPGA器件,其成本比上一代产品Cyclone器件低了30%,逻辑容量大了三倍多。

本设计的综合工具QuartusII是Altera公司的综合性PLD/FPGA开发软件,支持原理图、VHDL、VerilogHDL以及AHDL等多种设计输入形式。

本设计的仿真工具是Mentor公司的Modelsim10.1a,这是业界最优秀的HDL语言仿真软件,它能提供友好的仿真环境,是业界唯一的单内核支持VHDL和Verilog混合仿真的仿真器。

基本流程是这样的:

首先根据设计任务要求进行方案的设计,包括8X8点阵显示原理的熟悉、电路接口的确定、功能框图与模块的划分、验证方案等,然后就是用VerilogHDL对设计电路进行描述、建立测试平台和激励、在仿真工具上进行仿真和矫正,接着在综合工具上进行时序约束、管脚锁定,最后下载到芯片上实现和验证。

1总体电路结构设计

1.18X8点阵显示原理

本设计所使用的为一个共阳极8X8单色LED点阵,型号为1588AB-5,点阵的外部引脚的图如图1-1,内部结构等效电路图如图1-3,共由64个发光二极管组成,且每个发光二极管是放置在行线和列线的交叉点上,同一行的LED阳极连接在一起,同一列的阴极连在一起,仅当阳极和阴极的电压被加上,使LED为正偏时,LED才发亮,即当对应的某一行置1电平,某一列置0电平,则相应的二极管就亮;如要将第一个点点亮,则7脚接高电平A脚接低电平,则第一个点就亮了;如果要将第一行点亮,则第7脚要接高电平,而(A、B、C、D、E、F、G、H)这些引脚接低电平,那么第一行就会点亮;如要将第一列点亮,则第A脚接低电平,而(7、6、5、4、3、2、1、0)接高电平,那么第一列就会点亮。

图1-18X8点阵外观及引脚图图1-20的显示图样

图1-38X8点阵LED等效电路图

LED的点亮方式可以按行顺序点亮(行扫描法),也可以按列顺序点亮(列扫描法),本电路设计采用行描方式。

行扫描方式的扫描顺序为从下到上,依次点亮,则顺序输出的扫描码为8’h80,8’h40,8’h20,8’h10,8’h08,8’h04,8’h02,8’h01。

如果想要显示“0”如图1-2,则只需从上到下各行的显示码分别为8’he8,8’hdb,8’h99,8’h88,8’h91,8’h99,8’hdb,8’he7,即可显示出“0”字样。

对于扫描信号的频率,因为人的肉眼所能分辨的最大频率一般为25Hz左右,大于这个频率,肉眼所看到的点阵是连续点亮,所有本设计使用的工作时钟为1KHZ是绰绰有余的。

1.2关键功能电路设计

本电路设计的主要难在于对数据信息的显示编码,即数据编码功能块的设计。

任务要求显示0-9的数字和大小写的英文字符,共62个显示图样,则首先必须对这62个要显示的数据进行字模提取,就是要提取各个图样的显示码。

表1.1各个字符(数字)对应的ASCLL码和显示码表

数字和字母

ASCLL码(十六进制)

显示码(十六进制)

0

30

8’he7,8’hdb,8’h99,8’h89,8’h91,8’h99,8’hdb,8’he7

1

31

8’he7,8’hc7,8’he7,8’he7,8’he7,8’he7,8’he7,8’hc3

2

32

8’he7,8’hdb,8’h99,8’h99,8’hf3,8’he7,8’hcf,8’h81

3

33

8’hc3,8’h99,8’h99,8’hf3,8’hf3,8’h99,8’h99,8’hc3

4

34

8’hfb,8’hf3,8’he3,8’hd3,8’hb3,8’h81,8’hf3,8’hf3

5

35

8’h81,8’h9f,8’h9f,8’h83,8’hf9,8’h99,8’h99,8’hc3

6

36

8’hf7,8’hef,8’hdf,8’h83,8’h99,8’h99,8’hdb,8’he7

7

37

8’h81,8’hf9,8’hf9,8’hf3,8’he7,8’he7,8’he7,8’he7

8

38

8’hc3,8’h99,8’h99,8’hc3,8’h99,8’h99,8’h99,8’hc3

9

39

8’he7,8’hdb,8’h99,8’h99,8’hc1,8’hfb,8’hf7,8’hef

A

41

8’he7,8’hc3,8’hdb,8’h99,8’h81,8’h3c,8’h3c,8’h3c

B

42

8’h03,8’h39,8’h39,8’h03,8’h39,8’h39,8’h39,8’h03

C

43

8’hc1,8’h9e,8’h3f,8’h3f,8’h3f,8’h3f,8’h9e,8’hc1

D

44

8’h03,8’h39,8’h3c,8’h3c,8’h3c,8’h3c,8’h39,8’h03

E

45

8’h00,8’h3f,8’h3f,8’h01,8’h3f,8’h3f,8’h3f,8’h00

F

46

8’h00,8’h3f,8’h3f,8’h01,8’h3f,8’h3f,8’h3f,8’h3f

G

47

8’hc3,8’h99,8’h3c,8’h3f,8’h30,8’h3c,8’h99,8’hc3

H

48

8’h3c,8’h3c,8’h3c,8’h00,8’h3c,8’h3c,8’h3c,8’h3c

I

49

8’hc3,8’he7,8’he7,8’he7,8’he7,8’he7,8’he7,8’hc3

J

4a

8’hc0,8’hf9,8’hf9,8’hf9,8’hf9,8’h39,8’h33,8’h87

K

4b

8’h39,8’h33,8’h27,8’h0f,8’h27,8’h33,8’h39,8’h3c

L

4c

8’h3f,8’h3f,8’h3f,8’h3f,8’h3f,8’hx,8’h3e,8’h00

续表1.1各个字符(数字)对应的ASCLL码和显示码表

M

4d

8’h7e,8’h3c,8’h18,8’h24,8’h3c,8’h3c,8’h3c,8’h3c

N

4e

8’h7c,8’h3c,8’h1c,8’h2c,8’h34,8’h37,8’h3c,8’h3e

O

4f

8’hc3,8’h99,8’h3c,8’h3c,8’h3c,8’h3c,8’h99,8’hc3

P

50

8’h01,8’h3c,8’h3c,8’h01,8’h3f,8’h3f,8’h3f,8’h3f

Q

51

8’hc3,8’h99,8’h3c,8’h3c,8’h34,8’h38,8’h99,8’hc2

R

52

8’h01,8’h3c,8’h3c,8’h01,8’h0f,8’h27,8’h33,8’h38

S

53

8’hc1,8’h9c,8’h3f,8’h8f,8’hf1,8’hfc,8’h39,8’h83

T

54

8’h00,8’he7,8’he7,8’he7,8’he7,8’he7,8’he7,8’he7

U

55

8’h3c,8’h3c,8’h3c,8’h3c,8’h3c,8’h3c,8’h3c,8’h81

V

56

8’h3c,8’h3c,8’h3c,8’h99,8’h99,8’hdb,8’hc3,8’he7

W

57

8’h3c,8’h24,8’h24,8’h24,8’h24,8’h24,8’h24,8’h99

X

58

8’h3c,8’h18,8’hdb,8’he7,8’he7,8’hdb,8’h18,8’h3c

Y

59

8’h3c,8’h3c,8’h99,8’hc3,8’he7,8’he7,8’he7,8’he7

Z

5a

8’h00,8’hf9,8’hf3,8’he7,8’hcf,8’h9f,8’h3f,8’h00

a

61

8’hff,8’hff,8’hc7,8’hb7,8’hb7,8’hcb,8’hff,8’hff

b

62

8’hbf,8’hbf,8’ha3,8’h9d,8’h9d,8’ha3,8’hff,8’hff

c

63

8’hff,8’hff,8’hc7,8’h9f,8’h9f,8’hc7,8’hff,8’hff

d

64

8’hfd,8’hfd,8’hc5,8’hb9,8’hb9,8’hc5,8’hff,8’hff

e

65

8’hf8,8’hc7,8’hbb,8’h83,8’hbf,8’hc7,8’hff,8’hff

f

66

8’hf7,8’hef,8’hc7,8’hef,8’hef,8’hef,8’hff,8’hff

g

67

8’hff,8’hff,8’hc3,8’hbb,8’hbb,8’hc3,8’hfb,8’h8e

h

68

8’hdf,8’hdf,8’hc7,8’hdb,8’hdb,8’hdb,8’hff,8’hff

i

69

8’hef,8’hff,8’hcf,8’hef,8’hef,8’hc7,8’hff,8’hff

j

6a

8’hf7,8’he7,8’hf7,8’hf7,8’hf7,8’hf7,8’hd7,8’hef

k

6b

8’hdf,8’hdf,8’hd7,8’hcf,8’hd7,8’hdb,8’hff,8’hff

l

6c

8’hef,8’hef,8’hef,8’hef,8’hef,8’he7,8’hff,8’hff

m

6d

8’hff,8’hff,8’hc3,8’hd5,8’hd5,8’hd5,8’hff,8’hff

n

6e

8’hff,8’hff,8’h87,8’hdb,8’hdb,8’hdb,8’hff,8’hff

o

6f

8’hff,8’hff,8’he7,8’hdb,8’hdb,8’he7,8’hff,8’hff

p

70

8’hff,8’hff,8’h87,8’hdb,8’hc7,8’hdf,8’hdf,8’hdf

q

71

8’hff,8’hff,8’he1,8’hdb,8’he3,8’hfb,8’hfb,8’hf9

r

72

8’hff,8’hff,8’ha3,8’hdf,8’hdf,8’hdf,8’hff,8’hff

s

73

8’hff,8’he3,8’hdf,8’he7,8’hfb,8’hc7,8’hff,8’hff

t

74

8’hef,8’hef,8’hc7,8’hef,8’heb,8’hf7,8’hff,8’hff

u

75

8’hff,8’hff,8’hdb,8’hdb,8’hdb,8’he1,8’hff,8’hff

v

76

8’hff,8’hff,8’h99,8’hdb,8’hdb,8’he7,8’hff,8’hff

w

77

8’hff,8’hff,8’hab,8’hab,8’hab,8’hd7,8’hff,8’hff

x

78

8’hff,8’hff,8’hdb,8’he7,8’he7,8’hdb,8’hff,8’hff

y

79

8’hff,8’hff,8’hdb,8’hdb,8’hdb,8’he3,8’hf7,8’hcf

z

7a

8’hff,8’hff,8’hc3,8’hf7,8’hef,8’hc3,8’hff,8’hff

1.3电路接口

驱动电路根据信号功能将接口分为4部分,分别是时钟信号、复位信号、扫描信号、显示信号。

具体接口如下表1.2所示。

表1.2接口信号表

名称

IO属性

描述

备注

clk

In

输入时钟,1KHz频率

上升沿有效

rst

In

复位信号,给整个电路初值

低电平复位

sel[7:

0]

out

7bit的扫描信号,从左到右列扫描,赋有扫描码

高点平有效

dout[7:

0]

out

7bit的显示信号,与sel信号同步,当sel=8’h80时,把第一个扫描码赋给dout,当sel=8’h40时,把第二个扫描码赋给dout……以此类推

低电平点亮

1.4电路功能框图

依照任务要求和功能,将电路分为4个功能模块:

对ROM的操作和读出数据模块、对数据的编码模块、产生扫描信号的模块、根据控制信号选择显示输出模块。

电路的功能框图如下所示。

图1.1电路功能框图

图中输入信号只需时钟信号clk和复位信号rst,分别要接到有需要时钟和复位的模块,电路的输出为dout[7:

0]和sel[7:

0]接到8X8点阵上。

ROM模块包括一个1000进制计数器、一个64进制计数器、一个ROM,其中1000进制计数器是对工作频率为1KHz的时钟1000进行分频,产生cnt[9:

0]的输出给64进制计数器,64进制计数器当cnt=999时加1计数,产生地址信号add[5:

0]给ROM的地址端口,最后由ROM读取文件产生需要显示的信息给数据编码模块。

数据编码模块datacoding主要是对ROM模块提供数据信息进行显示编码,对照上面的表1.1的编码方式进行编码,产生do0[7:

0]、do1[7:

0]……、do7[7:

0]共64bit的编码输出给后面的选择显示模块。

扫描产生模块scanningout主要是通过时钟驱动产生需要的扫描信号s[7:

0],8’h80,8’h40,8’h20,8’h10,8’h08,8’h04,8’h02,8’h01循环输出。

选择显示模块selectshow还包括后面的8bitd触发器,根据扫描产生模块的s[7:

0]来选择编码产生的64bit显示码对dout[7:

0]赋值,如s=8’h80时,将do7[7:

0]赋给dout[7:

0],最后通过d触发器输出。

扫描信号s[7:

0]再输出前,也通过了8bitd触发器,因为显示码通过d触发器后时序延迟了一个工作周期,为了让扫描码与显示码同步,也必须加一个d触发器,产生最终的扫描信号sel[7:

0]输出。

1.5验证方案

设计验证主要有两部分内容:

一是对HDL代码进行仿真验证,二是下载到硬件芯片上实现功能的验证。

对于仿真部分的验证主要在于构造激励上,仿真时不需要ROM模块,所以激励文件不仅要对时钟和复位信号进行设定,还要对数据data[7:

0]信号进行设定。

本设计需要显示10个数字、26个大写字母和26个小写字母共62个字符,所以要分别把这62个字符对应的ASCLL码赋给data,当然也可能输入其他字符,本设计对于其他字符一律LED灯全亮。

对于硬件上的验证,本设计采用自动滚动显示方式,即只需要根据时钟和复位信号输入,硬件自己读出ROM模块里文件的数据,然后是点阵上点亮或熄灭对应的LED灯,显示出想要的图样。

2模块设计

本设计共有4个主要的功能模块,分别是ROM模块、数据编码模块、扫描产生模块和选择显示模块,这里对模块的详细功能和时序关系进行细致说明。

2.1ROM模块设计

ROM模块功能是要自动读出文件中要显示的信息送到后面的驱动电路中,则需要一个1000进制计数器、一个64进制计数器、一个ROM。

(1)因为整个电路的工作频率是1KHz,设计显示一个图样的持续时间为1s,则1000进制计数器的作用在于产生一个周期为1000个时钟周期的信号cnt[7:

0],给64进制计数器。

(2)64进制计数器功能在于自动产生地址add[5:

0]给ROM的地址端口,每当cnt=999时,add自己加1一次,从地址0开始一直读到地址63再返回地址0,从而实现自动从ROM读出数据。

(3)对于ROM的应用,QuartusII的宏单元中提供了ROM的使用,可供用户自由调用和设置,如图2-1就是在宏里面调界面,图2-2是对ROM进行设置,本设计只显示62个字符,随意ROM的容量就设置64(第一个位置给00,最后一个给其他字符的ASCLL码)。

图2-1ROM的调用图2-2ROM的设置

ROM模块的接口信号有时钟clk、复位rst、数据data[7:

0],具体如下表2.1所示。

表2.1ROM模块接口信号表

名称

IO属性

描述

备注

clk

in

输入时钟,频率1KHz

上升沿有效

rst

in

复位信号,给初值

低电平有效

data[7:

0]

out

从ROM中读出来的ASCLL码数据,要送到数据编码模块

ROM模块的RTL级电路如下图2.3所示。

图2.3ROM模块的RTL电路图

2.2数据编码模块设计

数据编码模块datacoding主要是对ROM模块提供数据(ASCLL码)信息进行显示编码,通过case语句,把data对照上面的表1.1的编码方式进行编码,分别赋给do0[7:

0]、do1[7:

0]……、do7[7:

0]共64bit的编码输出,如要显示图1.3字样,则do7=8’he8,do6=8’hdb,do5=8’h99,do4=8’h88,do3=8’h91,do2=8’h99,do1=8’hdb,do0=8’he7即可在点阵上显示出“0”。

复位时,分别给64bit的输出赋为1(即全灭),如果data不是数字和字母的ASCLL码,则输出全赋为0(即全亮)。

模块最后将do0、do1……do7输出给后面的选择显示模块。

数据编码模块datacoding的接口信号有时钟clk、复位rst、数据data、编码输出do0、do1……do7,具体如下表2.2所示。

表2.2数据编码模块接口信号表

名称

IO属性

描述

备注

clk

in

输入时钟,频率1KHz

上升沿有效

rst

in

复位信号,可以给输出初值

低电平有效

data[7:

0]

in

从ROM模块送来的ASCLL码数据,用于编码

do0[7:

0]

out

点阵显示第8行8个LED的显示码

do1[7:

0]

out

点阵显示第7行8个LED的显示码

…

…

do7[7:

0]

out

点阵显示第1行8个LED的显示码

数据编码流程图如下图2.4所示。

图2.4数据编码模块datacoding流程图

2.3扫描产生模块设计

扫描产生模块scanningout主要是通过时钟驱动产生需要的扫描信号s[7:

0],控制LED灯显示行位置,8’h80,8’h40,8’h20,8’h10,8’h08,8’h04,8’h02,8’h01循环输出,分别驱动第1行,第2行、……、第7行的LED灯,因为工作时钟频率是1KHz,所以s的扫描周期是8ms,大于人肉眼所能分辨的频率,所以在LED上显示是连续点亮的。

扫描产生模块的接口信号有时钟clk、复位rst、扫描码s[7:

0],具体如下表2.1所示。

表2.3扫描产生模块接口信号表

名称

IO属性

描述

备注

clk

in

输入时钟,频率1KHz

上升沿有效

rst

in

复位信号,给s[7:

0]初值8’h00

低电平有效

s[7:

0]

out

周期为8个时钟周期的扫描信号,用来驱动点阵

高电平驱动LED

扫描产生模块的工作波形图如图2-5。

图2-5扫描产生模块的工作波形图

2.4选择显示模块设计

选择显示模块selectshow功能是根据扫描产生模块的s[7:

0]来选择编码产生的64bit显示码对dout[7:

0]赋值,从而避免了显示时无法点亮正确的LED灯而出现显示混乱,即让显示码和扫描码同步,如s=8’h80时,将do7[7:

0]赋给dout[7:

0],s=8’h80即驱动第一行的8个LED灯,而dout[7:

0]=do7[7:

0]即用来点亮第一行8个LED灯。

考虑到组合电路输出的波形不够理想,dout[7:

0]使用8bit的d触发器输出的从而得到理想的波形,但是于此同时延迟了一个工作周期,造成与扫描码不同步,所以最后扫描码s[7:

0]也要接一个8bitd触发器输出sel[7:

0]使二者同步。

选择显示模块的接口信号有时钟clk、复位rst、扫描码s[7:

0]、