多周期MPIS指令集设计.docx

《多周期MPIS指令集设计.docx》由会员分享,可在线阅读,更多相关《多周期MPIS指令集设计.docx(91页珍藏版)》请在冰点文库上搜索。

多周期MPIS指令集设计

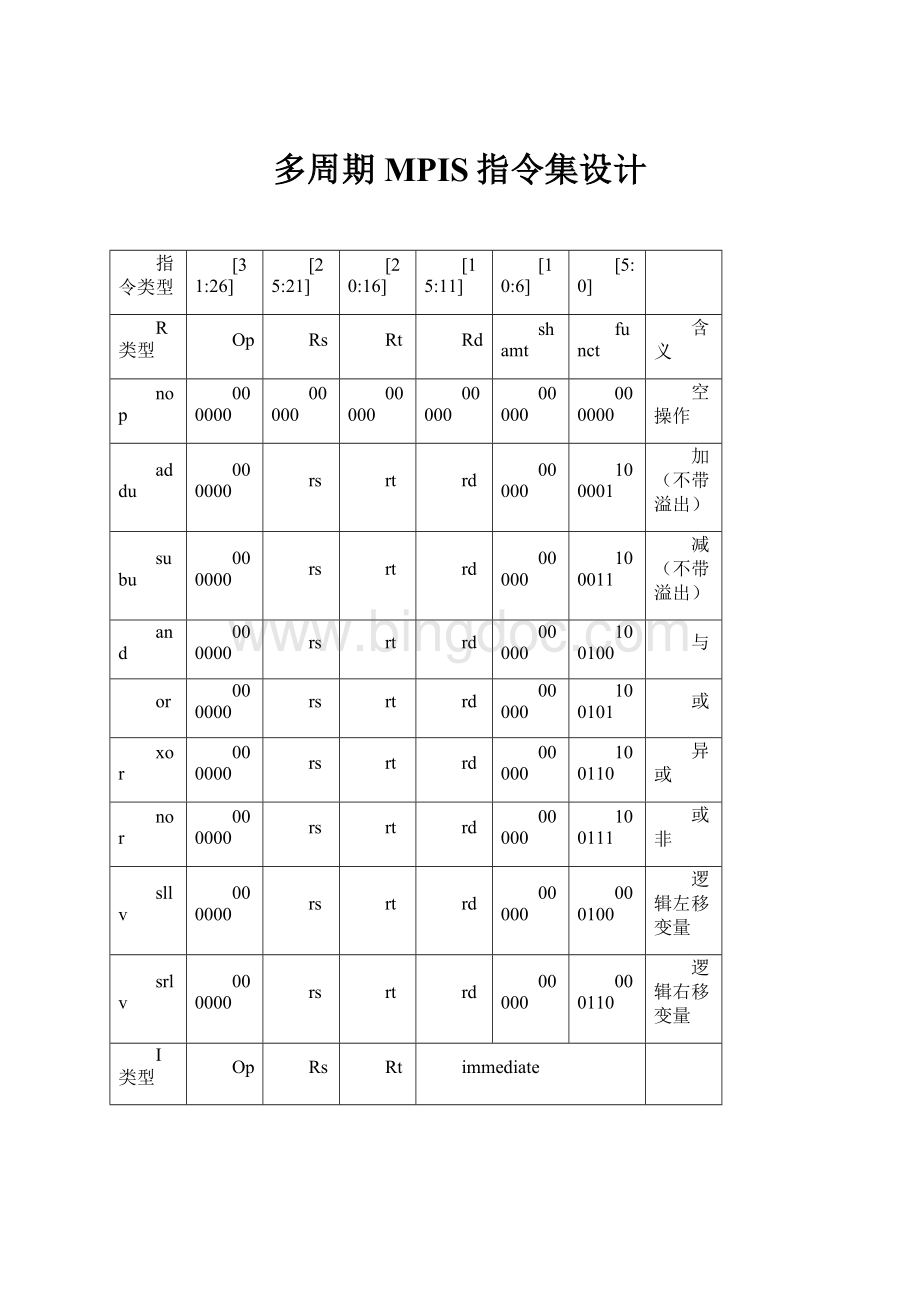

指令类型

[31:

26]

[25:

21]

[20:

16]

[15:

11]

[10:

6]

[5:

0]

R类型

Op

Rs

Rt

Rd

shamt

funct

含义

nop

000000

00000

00000

00000

00000

000000

空操作

addu

000000

rs

rt

rd

00000

100001

加(不带溢出)

subu

000000

rs

rt

rd

00000

100011

减(不带溢出)

and

000000

rs

rt

rd

00000

100100

与

or

000000

rs

rt

rd

00000

100101

或

xor

000000

rs

rt

rd

00000

100110

异或

nor

000000

rs

rt

rd

00000

100111

或非

sllv

000000

rs

rt

rd

00000

000100

逻辑左移变量

srlv

000000

rs

rt

rd

00000

000110

逻辑右移变量

I类型

Op

Rs

Rt

immediate

bltz

000001

rs

00000

Immediate

小于0转移

beq

000100

rs

rt

Immediate

相等转移

bne

000101

rs

rt

Immediate

不相等转移

addi

001000

rs

rt

Immediate

加立即数

andi

001100

rs

rt

Immediate

与立即数

ori

001101

rs

rt

Immediate

或立即数

lw

100011

rs

rt

Immediate

取字

sw

101011

rt

rt

Immediate

存字

J类型

Op

Address

j

000010

address

无条件跳转

综述:

本设计选用了如下指令,基于此设计出了单周期MIPS处理器,并在单周期的基础上添加了5级流水线设计出了带五级流水线的MIPS处理器。

第一部分单周期MIPS处理器

一、代码

----------------------------------------------------------------------------------

--ModuleName:

top_mips-Behavioral顶层模块

----------------------------------------------------------------------------------

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entitytop_mipsis

port(reset:

instd_logic;

clk:

instd_logic;

ov:

outstd_logic);

endtop_mips;

architectureBehavioraloftop_mipsis

signals_pc:

std_logic_vector(31downto0);---pc输入

signals_pc_i:

std_logic_vector(31downto0);---pc输出

signals_command:

std_logic_vector(31downto0);---指令

signals_add1_pc:

std_logic_vector(31downto0);---pc+1值

signals_shift:

std_logic_vector(27downto0);--指令低26位左移2位后值

signals_jump_pc:

std_logic_vector(31downto0);--绝对跳转

signals_regdst:

std_logic;----控制信号

signals_jump:

std_logic;

signals_branch:

std_logic;

signals_memread:

std_logic;

signals_memtoreg:

std_logic;

signals_aluop:

std_logic_vector(3downto0);

signals_memwrite:

std_logic;

signals_alusrc:

std_logic;

signals_regwrite:

std_logic;

signals_opa:

std_logic_vector(31downto0);----ALU操作数

signals_opb:

std_logic_vector(31downto0);----ALU操作数

signals_reg_data:

std_logic_vector(31downto0);--寄存器读出的第二个数据

signals_imm_data:

std_logic_vector(31downto0);---低16位符号扩展后

signals_zero:

std_logic;

signals_alu_result:

std_logic_vector(31downto0);

signals_branch_pc:

std_logic_vector(31downto0);----条件跳转

signals_1orbranch:

std_logic_vector(31downto0);

signals_ram_data:

std_logic_vector(31downto0);

signals_wr_data:

std_logic_vector(31downto0);

signals_mux:

std_logic;

signals_alu_ctrl:

std_logic_vector(3downto0);

signals_aimreg_addr:

std_logic_vector(4downto0);写寄存器堆的地址

componentpcis---pc指针模块

port(reset:

instd_logic;

clk:

instd_logic;

pc_i:

instd_logic_vector(31downto0);

pc_o:

outstd_logic_vector(31downto0));

endcomponent;

componentmemoryis---指令存储器

port(reset:

instd_logic;

mem_adr:

instd_logic_vector(31downto0);

mem_out:

outstd_logic_vector(31downto0));

endcomponent;

componentreg_32bit_arrayis---寄存器堆

port(reset:

instd_logic;

clk:

instd_logic;

wr_en:

instd_logic;

addr_wr:

instd_logic_vector(4downto0);

addr1_rd:

instd_logic_vector(4downto0);

addr2_rd:

instd_logic_vector(4downto0);

reg_data_i:

instd_logic_vector(31downto0);

reg_data1_o:

outstd_logic_vector(31downto0);

reg_data2_o:

outstd_logic_vector(31downto0));

endcomponent;

componentramis---数据存储器

port(reset:

instd_logic;

clk:

instd_logic;

rd_en:

instd_logic;

wr_en:

instd_logic;

addr:

instd_logic_vector(5downto0);

data_i:

instd_logic_vector(31downto0);

data_o:

outstd_logic_vector(31downto0));

endcomponent;

componentfsmis----指令译码器

port(

command:

instd_logic_vector(5downto0);

regdst:

outstd_logic;

jump:

outstd_logic;

branch:

outstd_logic;

memread:

outstd_logic;

memtoreg:

outstd_logic;

aluop:

outstd_logic_vector(3downto0);

memwrite:

outstd_logic;

alusrc:

outstd_logic;

regwrite:

outstd_logic);

endcomponent;

componentALU_ctrlis----ALU控制单元

port(

funct_i:

instd_logic_vector(5downto0);

aluop_i:

instd_logic_vector(3downto0);

alu_ctrl_o:

outstd_logic_vector(3downto0));

endcomponent;

componentaluis----ALU

port(

op_a,op_b:

instd_logic_vector(31downto0);

alu_ctrl_i:

instd_logic_vector(3downto0);

zero:

outstd_logic;

result:

outstd_logic_vector(31downto0));

endcomponent;

componentaddis---加法器

port(

op_a,op_b:

instd_logic_vector(31downto0);

result:

outstd_logic_vector(31downto0);

ov:

outstd_logic);

endcomponent;

begin

s_shift<=s_command(25downto0)&"00";---左移2位

s_add1_pc<=s_pc+1;---pc+1

s_jump_pc<=s_add1_pc(31downto28)&s_shift;---无条件跳转地址

s_mux<=s_branchands_zero;

s_aimreg_addr<=s_command(20downto16)whens_regdst='0'else

s_command(15downto11);

s_opb<=s_reg_datawhens_alusrc='0'else

s_imm_data;

s_1orbranch<=s_add1_pcwhens_mux='0'else

s_branch_pc;

s_pc_i<=s_1orbranchwhens_jump='0'else

s_jump_pc;

s_wr_data<=s_alu_resultwhens_memtoreg='0'else

s_ram_data;

---expand

s_imm_data<=s_command(15)&x"0000"&s_command(14downto0);

mips_pc:

pcportmap(reset=>reset,

clk=>clk,

pc_i=>s_pc_i,

pc_o=>s_pc);

mips_memory:

memoryportmap(reset=>reset,

mem_adr=>s_pc,

mem_out=>s_command);

mips_regs:

reg_32bit_arrayportmap(

reset=>reset,

clk=>clk,

wr_en=>s_regwrite,

addr_wr=>s_aimreg_addr,

addr1_rd=>s_command(25downto21),

addr2_rd=>s_command(20downto16),

reg_data_i=>s_wr_data,

reg_data1_o=>s_opa,

reg_data2_o=>s_reg_data);

mips_ram:

ramportmap(reset=>reset,

clk=>clk,

wr_en=>s_memwrite,

rd_en=>s_memread,

addr=>s_alu_result(5downto0),

data_i=>s_reg_data,

data_o=>s_ram_data);

mips_fsm:

fsmportmap(command=>s_command(31downto26),

regdst=>s_regdst,

jump=>s_jump,

branch=>s_branch,

memread=>s_memread,

memtoreg=>s_memtoreg,

aluop=>s_aluop,

memwrite=>s_memwrite,

alusrc=>s_alusrc,

regwrite=>s_regwrite);

mips_aluctrl:

ALU_ctrlportmap(funct_i=>s_command(5downto0),

aluop_i=>s_aluop,

alu_ctrl_o=>s_alu_ctrl);

mips_alu:

aluportmap(op_a=>s_opa,

op_b=>s_opb,

alu_ctrl_i=>s_alu_ctrl,

zero=>s_zero,

result=>s_alu_result);

mips_add:

addportmap(op_a=>s_add1_pc,

op_b=>s_imm_data,

result=>s_branch_pc,

ov=>ov);

endBehavioral;

----------------------------------------------------------------------------------

--ModuleName:

pc-Behavioralpc模块

----------------------------------------------------------------------------------

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entitypcis

port(reset:

instd_logic;

clk:

instd_logic;

pc_i:

instd_logic_vector(31downto0);

pc_o:

outstd_logic_vector(31downto0));

endpc;

architectureBehavioralofpcis

begin

process(clk,reset,pc_i)

begin

ifreset='1'then

pc_o<=x"00000000";

elsif(clk'eventandclk='1')then

pc_o<=pc_i;

endif;

endprocess;

endBehavioral;

----------------------------------------------------------------------------------

--ModuleName:

memory-Behavioral程序存储器模块

------------------------------指令存储器64×32----------------------------------------------------

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entitymemoryis

port(reset:

instd_logic;

mem_adr:

instd_logic_vector(31downto0);

mem_out:

outstd_logic_vector(31downto0));

endmemory;

architectureBehavioralofmemoryis

TYPEmem_dataisarray(0to63)ofstd_logic_vector(31downto0);---指令存储器

signalrom_table:

mem_data;

begin

process(reset,mem_adr,rom_table)

begin

if(reset='1')then

rom_table<=(---------将指令通过RESET固化进去

"00000000000000000000000000000000",---nop

"00000000000000000000000000000000",---nop

"00000000001000100000100000100000",---add

"00000000011000100001000000100010",---sub

"00000000100001010001100000100100",---and

"00000000110001110010000000100101",---or

"00000001000010010010100000100110",---xor

"00000001010010110011000000100111",---nor

"00000001100011010011100000000100",---sllv

"00000001110011110100000000000110",---srlv

"00000111111000000000000000000010",---bltz

"00000000000000000000000000000000",

"00000000000000000000000000000000",

"00010010001011110000000000000010",---beq

"00000000000000000000000000000000",

"00000000000000000000000000000000",

"00010110010100110000000000000010",---ben

"00000000000000000000000000000000",

"00000000000000000000000000000000",

"00000110000000000000000000000010",---bltz

"00000000000000000000000000000000",

"00000000000000000000000000000000",

"00010010001100010000000000000010",---beq

"00000000000000000000000000000000",

"00000000000000000000000000000000",

"00010111111000000000000000000010",---ben

"00000000000000000000000000000000",

"00000000000000000000000000000000",

"00100010011111100000000011111111",---addi

"00110010100111010000000000011001",---andi

"00110110110111000000000000011000",---ori

"10001100000110110000000000001111",---lw

"10101100000101110000000000011111",---sw

"00001000000000000000000000011101",---j

"00000000000000000000000000000000",

"000000000000000000000