计算机的并行接口大全.docx

《计算机的并行接口大全.docx》由会员分享,可在线阅读,更多相关《计算机的并行接口大全.docx(36页珍藏版)》请在冰点文库上搜索。

计算机的并行接口大全

计算机的并行接口,计算机的并行接口大全

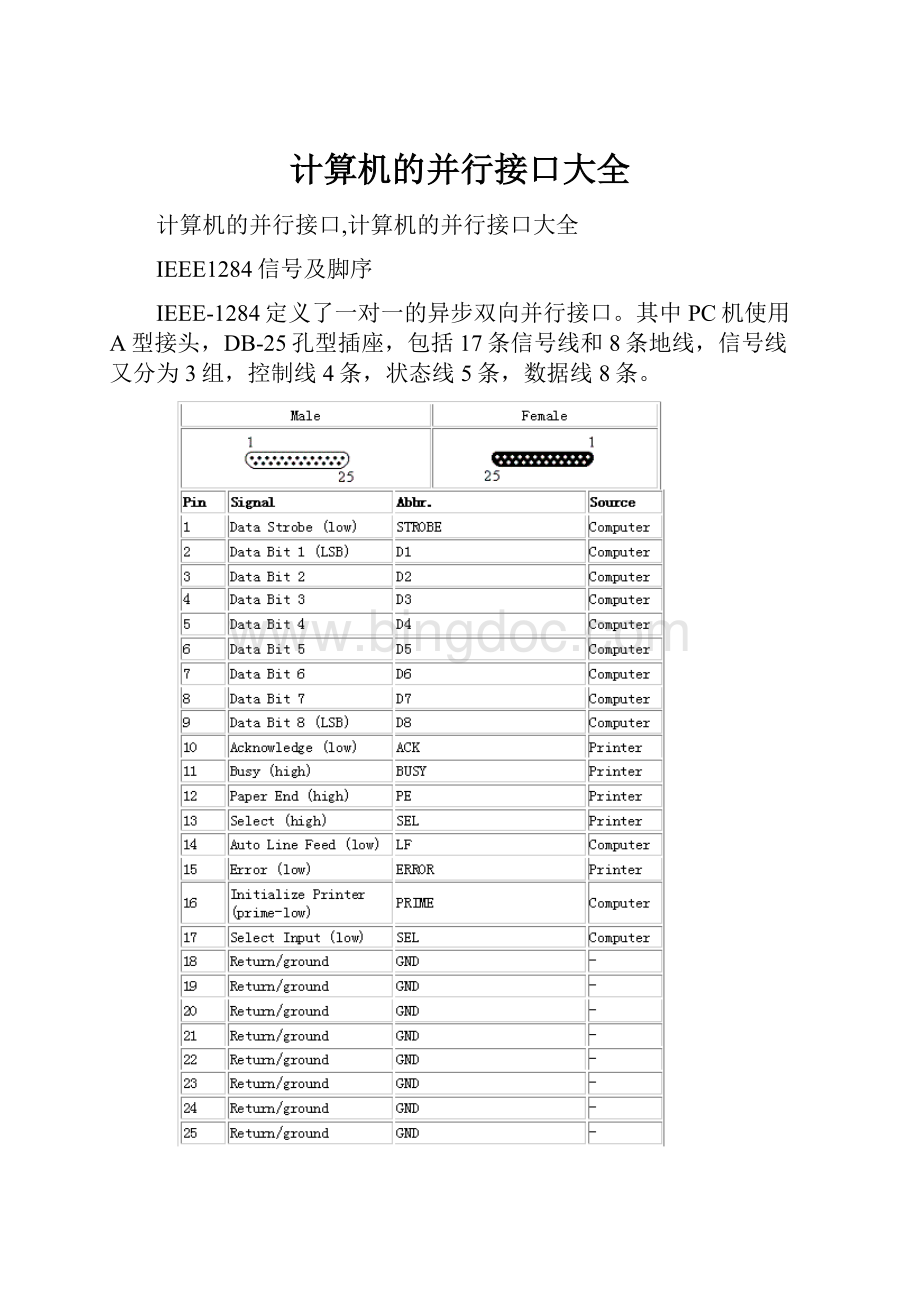

IEEE1284信号及脚序

IEEE-1284定义了一对一的异步双向并行接口。

其中PC机使用A型接头,DB-25孔型插座,包括17条信号线和8条地线,信号线又分为3组,控制线4条,状态线5条,数据线8条。

打印机使用B型接头,为36PIN0.085inch间距的Champ连接器,称Centronics连接器

36PINCentronics连接器的各脚信号的含义

C型:

新的Mini-Centronics36PIN连接器,0.050inch间距,既可用于主机,也可用于外设

D型25针和36针Centronics的针脚定义对照:

A型、B型、C型连接器的针脚定义对照:

4. IEEE1284接口的对接:

PC机DB-25与打印机Centronics36PIN连接器的信号对应关系:

PC机边A型(DB-25)与打印机边B型(Centronics36PIN)连接器的对接:

PC机边A型(DB-25)与打印机边C型(Mini-Centronics36PIN)连接器的对接:

PC机边C型(Mini-Centronics36PIN)与打印机边B型(Centronics36PIN)连接器的对接:

5. IEEE1284硬件接口

IEEE-1284定义了2种级别的接口兼容性,LevelI用于产品不需要高速模式,但需要利用反向通道能力的场合;LevelII用于长电缆和高速传输率场合。

并行接口输出的是TTL标准的逻辑电平,输入信号也要符合TTL标准。

这种特性可以使接口容易应用在电子设计中。

大部分的PC并行接口能吸收和输出12mA左右的电流,如应用时小于或大于这个值,应使用缓冲电路。

为了保持与早期的Centronics接口兼容,使用OC(opencollector)驱动器,使用上拉电阻(pull-upresistor)标准电阻值为2.2k欧或4.7k欧。

控制线与状态线仅要求上拉电阻Rp,数据线和Strobe线还要求串联电阻Rs来匹配线路阻抗,调整串联电阻值使其与驱动器的输出阻抗之和等于45欧到55欧的线路阻抗。

比如驱动IC输出阻抗为15欧,则需要33欧的串联电阻。

IEEE-1284接口芯片:

因为最小输出驱动电压为2.4V,标准TTL的+5V或低压TTL的+3.3V的芯片都可以使用。

Fairchild、ST、TI公司都有类似芯片,如74ACT1284、74LVC161284、74LV161284等,还有专用的ESD芯片74F1071等。

6. IEEE1284信号规格表

本文参考了以下资料,表示感谢:

温正伟原载电子报的资料

.interfacebus./Design_Connector_1284.html

ckp.made-it./ieee1284.html

.fapo./1284int.htm

zone.ni./devzone/cda/tut/p/id/3466

.homestead.co.uk/

系统分类:

接口电路 |

用户分类:

信号接口 |

标签:

并行接口IEEE-1284打印机CentronicsD25 |

来源:

整理 |

点击查看原文

发表评论阅读全文(2165)|回复(0)

发表于2007/12/301:

45:

50

2

计算机的并行接口

(2)

2. IEEE1284定义的5种工作模式

为了提高Centronics接口的性能,也要兼容过去的标准,IEEE1284定义了5种工作模式:

SPP模式:

StandardParallelPort标准并行接口,也称为Compatibilitymode兼容模式,Nibble模式:

从PC机到外设8-bit数据线,反向4-bit数据线

Byte模式:

8-bit双向传输,速率在50KB/s到150KB/s之间

EPP模式:

EnhancedParallelPort增强并行接口,允许任一方向的高速字节传输

ECP模式:

ExtendedCapabilitiesPort扩展功能并行接口,允许PC机发送数据块

符合IEEE1284标准的并口,使用设备ID(Deviceidentificationsequence)来实现即插即用(PlugandPlay)配置,使并口更易于使用。

各种模式都可以使用相同的连接器和电缆连接方式,因硬件和编程方式的不同,传输速度可以从50KBits/秒到2MB/秒不等。

2.1)SPP模式:

即传统的Centronics并行接口,所以也称Centronicsmode

提供基本的信号,包括8-bit数据线,4条控制线(Strobe、InitializePrinter、SelectPrinter、AutoFeedline)和5条状态线(Busy、Acknowledge、Select、PaperEmpty、Fault),需要三个不同的寄存器来进行数据的读写操作。

SPP模式是最基本的工作模式,异步、字节单向传输,数据率在50KB/s到150KB/s之间。

使用AB-cable电缆可传6米,而使用新的CC-cable电缆可达10米。

基本的SPP模式的时序如图:

当打印机准备好接收数据,设BUSY为低,主机发出有效的数据到数据线,等待至少500ns然后发出STROBE负脉冲持续至少500ns,有效的数据在STROBE上升沿后至少要维持500ns。

打印机接收数据并设BUSY有效以指示处理数据,当打印机完成数据接收,发出ACK脉冲至少500ns,然后清除BUSY以指示准备好接收下一个字节数据。

Centronics标准的握手信号略有不同,nStrobe为最小宽度大于1us的负脉冲,nAck为宽度大于5us的响应负脉冲,由于nAck信号的负脉冲较短,一般不会查询它,而是查询Busy。

主机软件通过4步来完成1字节数据通过并口的传输:

1. 把有效数据写入数据寄存器

2. 检查BUSY状态线,等待其无效(0)

3. 写控制寄存器,使STROBE有效(0)

4. 写控制寄存器,使STROBE失效

(1)

SPP模式要求的最小的建立时间、保持时间和脉冲宽度限制了其性能,考虑到软件的等待时间,IEEE1284最大的数据传输率为150kbytes/s,而Centronics典型为10kbytes/s,这对于点阵行式打印机已经足够了,但对于高速的激光打印机就显露出不足。

SPP模式下的信号定义:

为操作并行口,SPP定义了寄存器,并映射到PC机的I/O空间。

寄存器包括了以并口地址为基址的3块连续的寄存器,并口地址常见为3BCH、378H和278H,其中都包括数据、状态和控制寄存器,分别对应数据、状态和控制信号线操作,通常称为数据端口、状态端口和控制端口。

打印机卡1的地址常为378H,其中数据口0378H、状态口0379H、控制口037AH;打印机卡2的地址常为278H,其中数据口0278H、状态口0279H、控制口027AH。

支持新的IEEE1284标准的并口,使用8到16个寄存器,地址为378Hor278H,即插即用(PlugandPlay)兼容的的并口适配器也可以重新加载。

并口的寄存器定义:

数据寄存器:

所占用的地址是并行接口的基地址,对应于于接口的2-9针

状态寄存器:

占用的地址是基地址加1,对应于接口的10,11,12,13,15针,是只读寄存器,其中包含一个IRQ中断位(由Ack相反后形成),当有中断发生这个数据位为“0”。

Bit7(引脚11)在输入+5V电平时,数据值为”0”,有反转的特性。

控制寄存器:

占用的地址是基地址加2,对应于接口的1,14,16,17针,其中Bit0,Bit1,Bit3有反转的特性。

Bit4为IRQ应用,当向Bit4写入“1”时,将使ACK(引脚10)信号反相后成为中断请求IRQ信号,通常为IRQ5或IRQ7。

并口使用的3BCH、378H和278H三个基地址几乎都支持SPP、ECP和EPP模式(3BCH这个地址在早期的并口打印机适配器上不支持EPP和ECP模式)。

三个不同基地址的地址段如下:

一些集成的1284I/O控制器使用FIFObuffer传输数据称为FastCentronics或ParallelPortFIFOMode,也使用SPP协议,但用硬件产生strobe信号来实现控制信号握手,使数据率能超过500KB/s。

然而,这不是IEEE1284定义的标准模式。

2.2)Nibble模式:

用于从打印机或外部设备得到反向数据的常用方式,

Nibble模式利用4条状态线把数据从外设传回电脑。

标准的并行口提供5条外设到PC机的信号线,用于指示外设的状态,利用这些信号线,外设可以分2次发送1字节(8-bit)数据,每次发半字节(nibble:

4-bit)信息。

因为nACK信号一般用来提供外设中断,所以难以把传输的nibble(半字节)信息通过状态寄存器(Statusregister)合成1字节,需要软件读状态信号并作相应操作来得到正确的字节信息。

Nibble模式的数据率为50kbps(6米电缆),使用新型10米CC-cable电缆的数据率为150kbps。

Nibble模式的优势在于具有并口的PC机都可以执行这种方式,但只能用于反向通道为低速率的场合。

下表定义了Nibble模式的信号:

下图描述了Nibble模式的基本时序

Nibble模式数据传输步骤:

1. 主机通过设置HostBusy为低表明可以接收数据

2. 外设把第一个半字节(nibble)输出到状态线

3. 外设设置PtrClk为低指示nibble数据有效

4. 主机设置HostBusy为高指示接收到nibble数据,而正在处理

5. 外设设置PtrClk为高应答主机

6. 重复步骤1到5来接收第二个半字节(nibble)

Nibble模式与SPP模式相似,需要软件通过设置和读取并口的控制信号线来实现协议。

Nibble模式与SPP模式结合建立完整的双向通道,形成最简单的双向传输方式。

从PC机到外设8-bit数据线,反向4-bit数据线,支持单向打印机接口,提供了全速率的前向传输和半速率的反向传输,速率在50KB/s到150KB/s之间。

2.3)Byte模式:

在数据线上实现反向传输的方式

Byte模式利用数据线把8-bit数据从外设传输到主机。

标准并行口的8-bit数据线只能从主机向外设单向传输,需要抑制住控制数据线的驱动器,使数据可以从打印机传到电脑。

Byte模式数据传送,一次传送一个字节,与nibble模式下需要的两数据周期不同,速度和由电脑到打印机的一样,在50KB/s到150KB/s之间,使用新型CC-cable可在10米电缆上达到500kbps。

下表定义了Byte模式的信号:

Byte模式数据传输步骤:

1. 主机通过设置HostBusy为低表明可以接收数据

2. 外设把第一个字节(byte)数据输出到数据线

3. 外设设置PtrClk为低指示byte数据有效

4. 主机设置HostBusy为高指示接收到byte数据,而正在处理

5. 外设设置PtrClk为高应答主机

6. 重复步骤1到5来接收其他字节(byte)数据

下图描述了Byte模式的基本时序

制造商首先在IBM PS/2并口上增加了对8-bit数据线的读取能力,实现Byte模式,使之成为双向口,称为扩展并口的Type1。

此外,还提供了Type2和Type3,使用DMA方式。

在Type2和3的DMA写数据时,DMA控制器向数据寄存器写数据,而STROBE脉冲自动产生,当从外设收到ACK,发出DMA请求,下一个字节发出。

外设可以设置BUSY来延迟传输。

在Type2和3的DMA读数据时,ACK脉冲产生DMA请求,发起对系统存储器的传输,DMA控制器读取数据寄存器,STROBE脉冲自动产生。

Type2和3的DMA传输依照SPP模式时序进行。

虽然IBM定义了Type2和3方式提高了并口的性能,但只有IBM计算机实现这种功能,缺乏软件来支持这种DMA特性。

相比较,EPP和ECP是种工业标准,为更广泛的硬件和软件制造商支持。

2.4)EPP模式:

EnhancedParallelPort增强型并行端口,可实现高速双向数据传输

EPP模式由Intel、Xircom,andZenithDataSystems设计,提供了一个高性能的并行接口,是IEEE1284标准中的一部分,可以和标准并行接口通用,有相同的寄存器映射关系,协议首先由Intel386SL芯片组(82360I/Ochip)实现。

EPP模式的信号定义

EPP模式有一个数据周期和一个地址周期,提供了4种传输周期时序:

1. 数据写周期时序

2. 数据读周期时序

3. 地址写周期时序

4. 地址读周期时序

数据周期时序用于在主机和外设间传输数据,地址周期时序用于分配地址、通道、命令和控制信息。

EPP地址写周期:

主机首先设置WRITE*,并把地址信号发到数据线上,设置ASTROBE*;外设取消WAIT*,指示已准备接收地址字节;主机然后取消ASTROBE*;外设在ASTROBE*上升沿锁存地址数据,然后设置WAIT*,指示准备开始下一周期。

EPP地址读周期:

主机取消WRITE*,使数据线处于高阻状态,设置ASTROBE*;外设发地址字节到数据线,取消WAIT*指示地址有效;主机检测到WAIT*取消,读地址,然后取消ASTROBE;外设然后使数据线处于高阻状态,设置WAIT*,指示准备开始下一周期。

EPP数据写周期:

主机设置WRITE*,把数据字节发到数据线,设置DSTROBE*;外设取消WAIT*,指示准备接收数据;主机然后取消DSTROBE*;外设在DSTROBE*上升沿锁存数据,然后设置WAIT*,指示准备开始下一周期。

EPP数据读周期:

主机取消WRITE*,使数据线处于高阻状态,设置DSTROBE*;外设把数据字节发往数据线,取消WAIT*,指示数据有效;主机检测到WAIT*取消,读数据,然后取消DSTROBE*;外设外设然后使数据线处于高阻状态,设置WAIT*,指示准备开始下一周期。

EPP模式在3个SPP模式并口寄存器外又定义了5个寄存器,用于把地址或数据自动发到并口数据线上,然后自动产生地址和数据的选通(strobe)信号。

EPP模式的数据、状态和控制寄存器与SPP模式的配置相同。

把数据写入AutoAddressStrobe寄存器,将把数据发到并口数据线,并伴随自动产生的ASTROBE*低脉冲信号;把数据写入任一AutoDataStrobe寄存器,将把数据发到并口数据线,并伴随自动产生的DSTROBE*低脉冲信号;当一个AutoDataStrobe寄存器在读取,DSTROBE*信号受脉冲控制,返回电平值。

EPP寄存器接口:

从软件角度看,EPP模式是扩展了SPP的并口寄存器。

SPP的并口包括数据Data、状态Status和控制Control3个寄存器,地址为并口基址(baseaddress)的偏移(offset)。

EPP寄存器定义如下:

通过产生一个对“base_address+4”的I/O写指令,EPP控制器产生需要的数据写(Data_Write)周期的handshake信号和strobes用来传输数据。

而对基址(ports0到2)的I/O指令将实现标准并行口的操作,以保证与标准并口的兼容。

而对"base_address+3"的I/O操作,会产生地址读写周期。

Ports5到7的作用在不同硬件中有差别,可用作实现16-bit或32-bit的软件接口,或用作配置寄存器,也可能不使用。

标准并口的数据传输需要7个软件步骤,EPP增加了其他的硬件和寄存器,通过单I/O指令自动产生控制strobes和数据传输的handshaking信号,保证以ISA总线速度传输,最大数据率为2Mbytes/s,在其他平台上可能达到10Mbytes/s。

EPP的微处理器的总线结构使之易于直接与外设硬件通讯。

EPP模式还有进一步的块传输能力,使用REP_IO指令,依靠主机适配器的支持。

EPP模式数据写时序的步骤:

1. 程序对PORT4(EPPDataPort)执行I/O写周期

2. nWrite信号有效,数据发送到并口

3. 设datastrobe有效,然后nWAIT设置为低

4. 等待外设的响应(nWAIT变为无效)

5. 设置datastrobe无效,结束EPP周期

6. ISA的I/O周期结束

7. nWAIT设置为低,指示下一个周期开始

下图是EPP数据写时序的实例,CPU信号nIOW是用来强调全部的handshake在一次I/O中完成

注意,全部数据传输发生在一次ISA的I/O周期中,这表明使用EPP协议,数据传输率可为500KB/s到2MB/s,这样外设在性能上接近ISA卡。

因为使用互锁握手信号协议,数据可在很低的速率下传输。

Nibble、Byte、EPP和ECP模式都使用互锁握手信号协议。

所谓互锁握手信号,指每次控制信号的变化都需要另一边的响应。

EPP模式允许任一方向的高速字节传输,但不是同时,是半双工方式,为光盘机、磁带机、硬盘机和网络适配器设计,数据率从500KB/S到2MB/S,使用AB-cable电缆可传6米,而使用新的CC-cable电缆可达10米。

2.5)ECP模式:

ExtendedCapabilityPort扩展功能并行接口,也可实现高速双向数据传输

ECP模式是由MicrosoftandHewlettPackard提出,是对标准并口的扩展,作为打印机和扫描仪类的外设的高级通讯模式,允许图象数据压缩、排队中的FIFO(先入先出)和高速双向通信。

数据传送速度大约2—4MB/S。

ECP协议重新定义了SPP模式的信号,如下表:

ECP模式提供了2种数据传输周期时序,可用于2个方向:

1. 数据周期datacycle

2. 命令周期commandcycle

命令周期又分为2种类型,RLE(Run-LengthCount)和通道编址(Channeladdress)。

RLE方式实现数据的实时压缩,压缩率可达64:

1,特别用于打印机和扫描仪传输大量光栅图像数据(含有大量的相同数据串)时,但必须主机和外设都支持才可以实现。

通道编址与EPP的地址有不同,是用于一种物理设备包括多种逻辑设备的场合,比如FAX/Printer/Modem一体机。

ECP模式定义前向传输为主机到外设,有2种前向传输周期,当HostAck为高,指示进行data周期;当HostAck为低,command周期进行,数据描述用RLEcount或Channeladdress,数据字节的Bit8用来指示RLE或是Channeladdress,如果bit8为0,则bit1-7描述RunLengthCount(0-127),如果bit8为1,则bit1-7描述Channeladdress(0-127),下图描述了一个data周期和一个command周期的时序。

ECP模式的前向传输时序:

1. 主机发送数据到数据线,并设置HostAck为高来指示一个datacycle的开始

2. 主机设置HostClk为低,指示数据有效

3. 外设设置PeriphAck为高响应主机

4. 主机设置HostClk为高,这是边缘触发信号,用于使数据存入外设

5. 外设设置PeriphAck为低,指示准备好接收下一字节

6. 循环重复,但这次为commandcycle,因为HostAck为低

注意:

接口2侧都使用FIFO,发出的数据都认为已被接收。

在第4步,HostClk变为高,data被触发进入外设,数据指针计数器更新。

在有些情况下这有可能造成传输数据丢失。

ECP模式定义反向传输为从外设传输到主机,反向传输时,当并口线上数据有效,外设设置PeriphClk为低,主机在接收数据后设置HostAck为低。

下图描述了反向通道的command周期紧随data周期的时序:

上图也显示出ECP和EPP协议的不同。

在EPP模式,软件可以执行混合的读写操作,而不需要额外的协议;而在ECP模式,改变数据传输方向必须协商。

主机要求反向传输通道需设置nReverseRequest并等待外设的nAckReverse的响应,然后才可以进行反向数据传输。

另外,如果以前为DMA传输,软件必须等待DMA完成或中断DMA(要FIFO确定准确的已传输的数据量),然后要求反向通道。

ECP模式的反向Data和Command周期

1. 主机设置nReverseRequest为低,要求反向传输通道

2. 外设设置nAckReverse为低,响应主机

3. 外设发送数据到数据线,并设置PeriphAck为高指示data循环

4. 外设设置PeriphClk为低指示数据有效

5. 主机设置HostAck为高确认

6. 外设设置PeriphClk为高,这是边沿触发信号,用于使数据存入主机

7. 主机设置HostAck为低,指示准备好接收下一个字节

8. 循环重复,但这次是command周期,因为PeriphAck为低

ECPFIFO的使用,无论DMA方式或可编程I/O方式,减弱了与ISA的关联,软件不会精确知道数据传输的状态,只关心传输是否完成。

在Microsoft的规格书"TheIEEE1284ExtendedCapabilitiesPortProtocolandISAInterfaceStandard"中,定义了基于ISA的ECP模式的通用寄存器和适配器的工作模式。

ECP寄存器利用了定义的6个寄存器,只需要3个I/O口操作,注意寄存器的定义与工作模式有关。

ECP寄存器描述:

ECP模式在3个SPP模式并口寄存器外又定义了6个寄存器,用于把地址或数据自动发到并口数据线上,然后自动产生地址和数据的选通(strobe)信号。

ECP的Address和Data的FIFO包括至少16字节,可用于前向和反向传输,可以平滑数据流和提高数据率。

向AddressFIFO寄存器写数据,会自动发往并口。

ECP的DataFIFO寄存器用于主机和外设间的数据传输。

ECP模式并口寄存器配置图:

ECP模式的目的是实现并口的即插即用(plug-and-play)性能和在Windows环境下进行高性能双向传输。

ECP模式允许任一方向的高速字节传输,也是半双工方式,为打印机和扫描仪设计,数据率从500KB/S到1MB/S,使用AB-cable电缆可传6米,而使用新的CC-cable电缆可达10米。

ECP主要使用DMA而不是直接的I/O操作,目的是传输大的数据块。

2.6)工作模式选择过程(Negotiation):

一个设备可能设计为有多种工作模式,但不能同时使用,每次只能选用一种。

IEEE1284发明了协商(negotiation)方式,主机必须要判断所