干凯磊实现R型指令的CPU设计实验.docx

《干凯磊实现R型指令的CPU设计实验.docx》由会员分享,可在线阅读,更多相关《干凯磊实现R型指令的CPU设计实验.docx(11页珍藏版)》请在冰点文库上搜索。

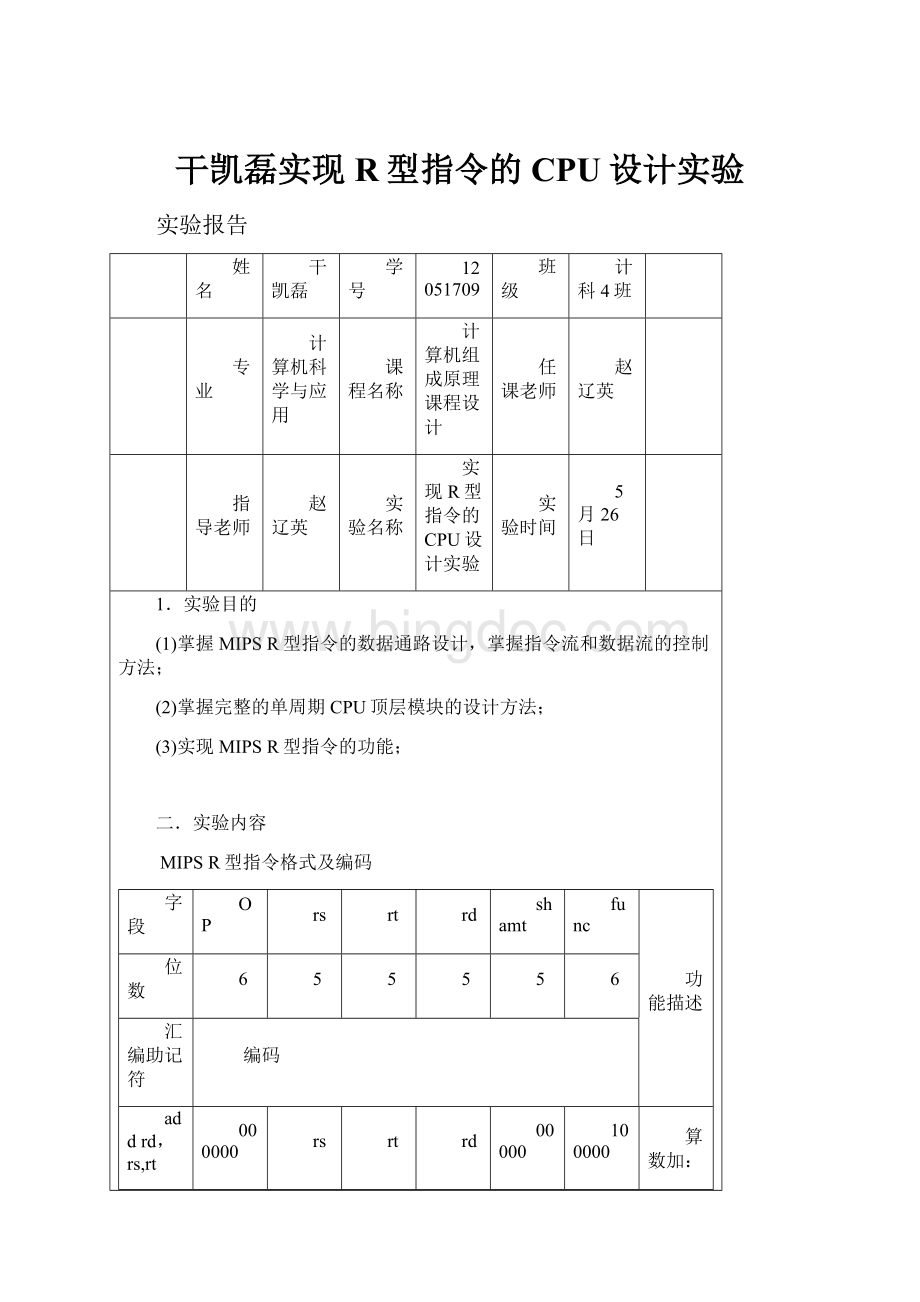

干凯磊实现R型指令的CPU设计实验

实验报告

姓名

干凯磊

学号

12051709

班级

计科4班

专业

计算机科学与应用

课程名称

计算机组成原理课程设计

任课老师

赵辽英

指导老师

赵辽英

实验名称

实现R型指令的CPU设计实验

实验时间

5月26日

1.实验目的

(1)掌握MIPSR型指令的数据通路设计,掌握指令流和数据流的控制方法;

(2)掌握完整的单周期CPU顶层模块的设计方法;

(3)实现MIPSR型指令的功能;

二.实验内容

MIPSR型指令格式及编码

字段

OP

rs

rt

rd

shamt

func

功能描述

位数

6

5

5

5

5

6

汇编助记符

编码

addrd,rs,rt

000000

rs

rt

rd

00000

100000

算数加:

rs+rt→rd

subrd,rs,rt

000000

rs

rt

rd

00000

100010

算数减:

rs-rt→rd

andrd,rs,rt

000000

rs

rt

rd

00000

100100

逻辑与:

rs&rt→rd

orrd,rs,rt

000000

rs

rt

rd

00000

100101

逻辑或:

rs|rt→rd

xorrd,rs,rt

000000

rs

rt

rd

00000

100110

逻辑异或:

rs⊕rt→rd

norrd,rs,rt

000000

rs

rt

rd

00000

100111

逻辑或非:

~(rs|rt)→rd

slturd,rs,rt

000000

rs

rt

rd

00000

101011

无符号数小于则置位:

if(rssllvrd,rt,rs

000000

rs

rt

rd

00000

000100

逻辑左移:

(rt<三.实验代码

moduleR_CPU(rst,clk,SW,LED,ALU_F);

inputrst,clk;

input[1:

0]SW;

outputreg[7:

0]LED;

output[31:

0]ALU_F;

wire[31:

0]Inst_code;

R_CPU_1my_cpu(clk,rst,ALU_F);

always@(*)

begin

case(SW[1:

0])

2'b00:

LED[7:

0]=ALU_F[7:

0];

2'b01:

LED[7:

0]=ALU_F[15:

8];

2'b10:

LED[7:

0]=ALU_F[23:

16];

2'b11:

LED[7:

0]=ALU_F[31:

24];

default:

LED[7:

0]=8'b00000000;

endcase

end

endmodule

moduleR_CPU_1(

inputclk,

inputrst,

output[31:

0]ALU_F);

wire[31:

0]Inst_code;

wire[4:

0]Rs,Rt,Rd;

wire[5:

0]OP,func;

wire[31:

0]ALU_A,ALU_B;

wireZF,OF;

regWrite_Reg;

regSet_ZF,Set_OF;

reg[2:

0]ALU_OP;

IFmy_if(.clk(clk),.rst(rst),.Instr_Code(Inst_code));

assignOP=Inst_code[31:

26];

assignRs=Inst_code[25:

21];

assignRt=Inst_code[20:

16];

assignRd=Inst_code[15:

11];

assignfunc=Inst_code[5:

0];

REGmy_reg(.Clk(~clk),.Reset(rst),.R_Addr_A(Rs),.R_Addr_B(Rt),.W_Addr(Rd),.W_Data(ALU_F),.Write_Reg(Write_Reg),.R_Data_A(ALU_A),.R_Data_B(ALU_B));

ALUmy_alu(.F(ALU_F),.ZF(ZF),.OF(OF),.A(ALU_A),.B(ALU_B),.ALU_OP(ALU_OP));

always@(*)

begin

ALU_OP=3'b000;

Write_Reg=1'b0;

Set_ZF=1'b0;

Set_OF=1'b0;

if(OP==6'b000000)

begin

Write_Reg=1'b1;

Set_ZF=1'b1;

case(func)

6'b100000:

ALU_OP=100;

6'b100010:

ALU_OP=101;

6'b100100:

ALU_OP=000;

6'b100101:

ALU_OP=001;

6'b100110:

beginALU_OP=010;Set_OF=1;end

6'b100111:

beginALU_OP=011;Set_OF=1;end

6'b101011:

ALU_OP=110;

6'b000100:

ALU_OP=111;

endcase

end

end

endmodule

moduleIF(

inputrst,

inputclk,

output[31:

0]Instr_Code);

wire[31:

0]pc_new;

reg[31:

0]pc;

ROMyour_instance(.clka(clk),.addra(pc[7:

2]),.douta(Instr_Code));

assignpc_new=pc+4;

always@(negedgeclkorposedgerst)

begin

if(rst)

pc<=32'h00000000;

else

pc<=pc_new;

end

endmodule

moduleREG(

inputClk,

inputReset,

input[4:

0]R_Addr_A,

input[4:

0]R_Addr_B,

input[4:

0]W_Addr,

input[31:

0]W_Data,

inputWrite_Reg,

output[31:

0]R_Data_A,

output[31:

0]R_Data_B

);

reg[31:

0]REG_Files[0:

31];

integeri;

assignR_Data_A=REG_Files[R_Addr_A];

assignR_Data_B=REG_Files[R_Addr_B];

always@(posedgeClkorposedgeReset)

begin

if(Reset)

begin

for(i=0;i<=31;i=i+1)

REG_Files[i]<=32'h0000_0000;

end

else

begin

if(Write_Reg)

REG_Files[W_Addr]<=W_Data;

end

end

endmodule

moduleALU(F,ZF,OF,A,B,ALU_OP);

outputreg[31:

0]F;

outputZF,OF;

input[31:

0]A,B;

input[2:

0]ALU_OP;

wireSF,PF;

regCF,OF;

parameterANDD=3'b000,

ORR=3'b001,

XORR=3'b010,

NORR=3'b011,

ADD=3'b100,

SUB=3'b101,

SLT=3'b110,

SRL=3'b111,

Zero_32=32'h0000_0000,

One_32=32'h0000_0001;//常量0和1,32位数据

always@(*)

begin

OF=0;

CF=0;

case(ALU_OP[2:

0])

ANDD:

F=A&B;

ORR:

F=A|B;

XORR:

F=A^B;

NORR:

F=~(A|B);

ADD:

begin

{CF,F}=A+B;

OF=A[31]^B[31]^F[31]^CF;

end

SUB:

begin

{CF,F}=A-B;

OF=A[31]^B[31]^F[31]^CF;

end

SLT:

F=(A>B)?

Zero_32:

One_32;

SRL:

F=B<endcase

end

assignZF=~|F;

assignSF=F[31];

assignPF=~^F;

endmodule

四.电路图

5.引脚配置

六.实验结果及分析

R型指令CPU实验结果记录表

序号

指令

执行结果

结论

1

0000ffff

00000000

正确

2

0025ffff

ffffffff

正确

3

0125ffff

00000001

正确

4

0175ffff

00000002

正确

5

0225ffff

00000004

正确

6

0275ffff

00000005

正确

7

0325ffff

ffffffe0

正确

8

0375ffff

fffffffe

正确

9

0425ffff

ffffffe2

正确

10

0475ffff

ffffffe2

正确

11

0525ffff

ffffffe7

正确

12

0575ffff

ffffffce

正确

13

0625ffff

ffffffcd

正确

14

0675ffff

ffffffcf

正确

15

0725ffff

0000002f

正确

16

0775ffff

00000000

正确