问题总结BJT.docx

《问题总结BJT.docx》由会员分享,可在线阅读,更多相关《问题总结BJT.docx(18页珍藏版)》请在冰点文库上搜索。

问题总结BJT

BJT知识总结

问题1:

纵向横向晶体管区别

1.集成NPN晶体管

在双极型线性集成电路中NPN晶体管的用量最多,所以它的质量对电路性能的影响最大。

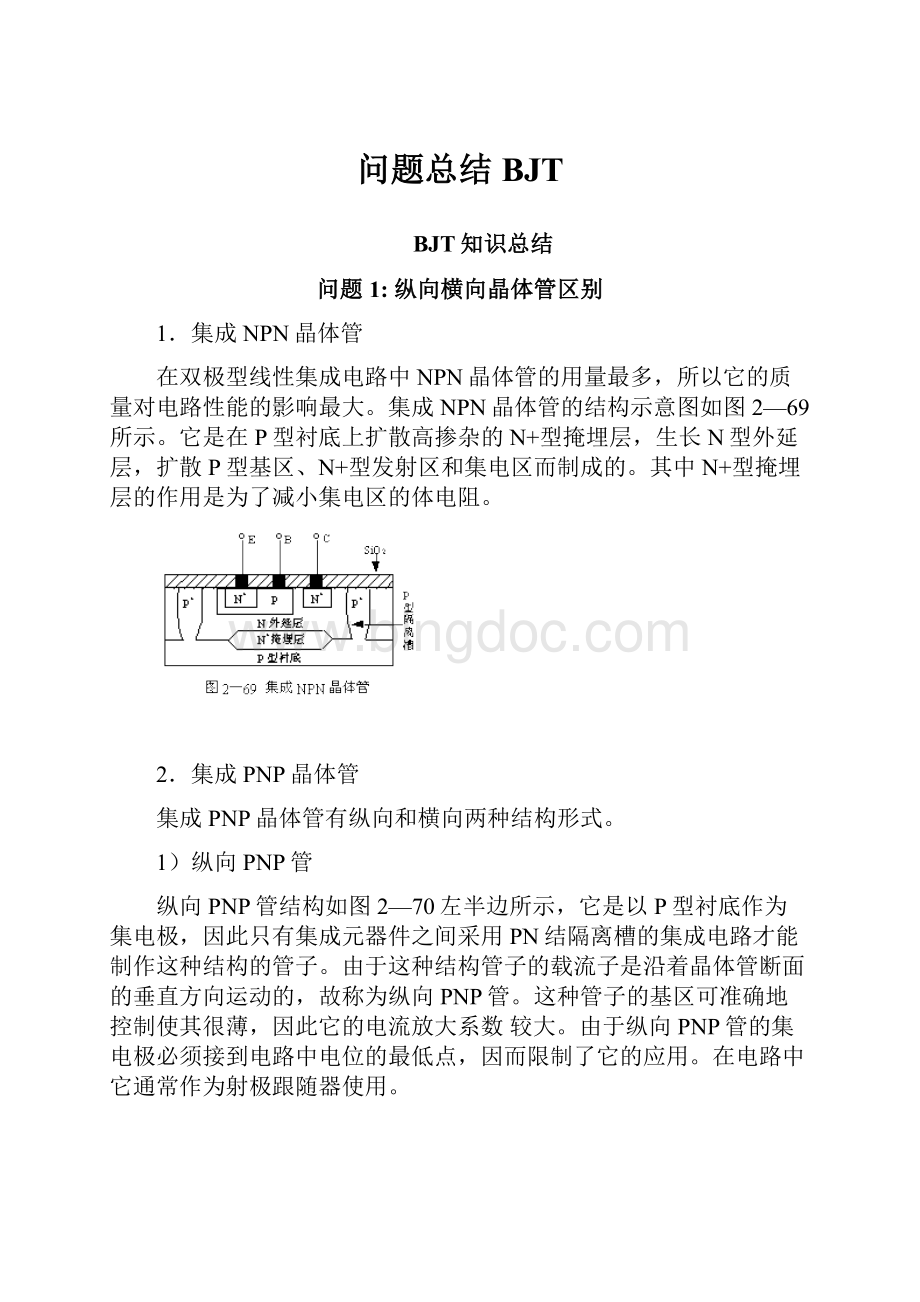

集成NPN晶体管的结构示意图如图2—69所示。

它是在P型衬底上扩散高掺杂的N+型掩埋层,生长N型外延层,扩散P型基区、N+型发射区和集电区而制成的。

其中N+型掩埋层的作用是为了减小集电区的体电阻。

2.集成PNP晶体管

集成PNP晶体管有纵向和横向两种结构形式。

1)纵向PNP管

纵向PNP管结构如图2—70左半边所示,它是以P型衬底作为集电极,因此只有集成元器件之间采用PN结隔离槽的集成电路才能制作这种结构的管子。

由于这种结构管子的载流子是沿着晶体管断面的垂直方向运动的,故称为纵向PNP管。

这种管子的基区可准确地控制使其很薄,因此它的电流放大系数较大。

由于纵向PNP管的集电极必须接到电路中电位的最低点,因而限制了它的应用。

在电路中它通常作为射极跟随器使用。

2)横向PNP管

横向PNP管结构如图2—70右半边所示,这种结构管子的载流子是沿着晶体管断面的水平方向运动的,故称为横向PNP管。

由于受工艺限制,基区宽度不可能很小,所以它的值相对较低,一般为十几倍到二、三十倍。

横向PNP管的优点是:

发射结和集电结都有较高的反向击穿电压,所以它的发射结允许施加较高的反压;另外它在电路中的连接方式不受任何限制,所以比纵向PNP管有更多的用途。

它的缺点是结电容较大,特征频率fT较低,一般为几~几十兆赫。

问题2:

相近的尺寸下,为什么BJT的工作工作频率比CMOS的高,噪声低,从器件的角度分析.

BJT工作频率比CMOS高是因为fT更大:

BJT的fT=2uVt/2piWB*WB,CMOS的fT=1.5u(Vgs-Vth)/2piL*L,在相同工艺条件下,WB可以远小于L,所以BJT的fT比CMOS大.BJT噪声特性比CMOS更好是因为:

BJT电流流动主要在体内(基区在体内),而CMOS的导电沟道在表面,所受散射更多,所以噪声更大.但是现在L可以做的越来越小了,工作频率达到或者超过BJT没有问题了。

但是噪声可能还不如BJT。

如果从电路的角度讲,ft~gm/C,gm越大,寄生电容越小,ft就越高。

总的来说,现在一般大家都用CMOS了。

问题3:

带隙基准为什么叫带隙?

带隙电压是指什么?

当带隙基准温度系数为0的时候可以推出VREF=Eg/q+(4+m)VT,m=-1.5,这里这个T是常数,是VREF温度系数为零的那一点,假如设计带隙温度零点为常温300K,这时候VT是0.026V=26mV.硅的价带和禁带之间的宽度为常数Eg=1.12eV,

VREF=1.12+2.5*0.026≈1.12=Eg/e,Eg/e占VREF电压的绝大部分,所以有带隙基准之名.

问题4:

三极管开关速度与加速电容

晶体管的开关速度即由其开关时间来表征,开关时间越短,开关速度就越快。

BJT的开关过程包含有开启和关断两个过程,相应地就有开启时间ton和关断时间toff,晶体管的总开关时间就是ton与toff之和。

如何提高晶体管的开关速度?

——可以从器件设计和使用技术两个方面来加以考虑。

(1)晶体管的开关时间:

晶体管的开关波形如图1所示。

其中开启过程又分为延迟和上升两个过程,关断过程又分为存储和下降两个过程,则晶体管总的开关时间共有4个:

延迟时间td,上升时间tr,存储时间ts和下降时间tf;

ton=td+tr,toff=ts+tf

在不考虑晶体管的管壳电容、布线电容等所引起的附加电容的影响时,晶体管的开关时间就主要决定于其本身的结构、材料和使用条件。

①延迟时间td:

延迟时间主要是对发射结和集电结势垒电容充电的时间常数。

因此,减短延迟时间的主要措施,从器件设计来说,有如:

减小发射结和集电结的面积(以减小势垒电容)和减小基极反向偏压的大小(以使得发射结能够尽快能进入正偏而开启晶体管);而从晶体管使用来说,可以增大输入基极电流脉冲的幅度,以加快对结电容的充电速度(但如果该基极电流太大,则将使晶体管在导通后的饱和深度增加,这反而又会增长存储时间,所以需要适当选取)。

②上升时间tr:

上升导通时间是基区少子电荷积累到一定程度、导致晶体管达到临界饱和(即使集电结0偏)时所需要的时间。

因此,减短上升时间的主要措施,从器件设计来说有如:

增长基区的少子寿命(以使少子积累加快),减小基区宽度和减小结面积(以减小临界饱和时的基区少子电荷量),以及提高晶体管的特征频率fT(以在基区尽快建立起一定的少子浓度梯度,使集电极电流达到饱和);而从晶体管使用来说,可以增大基极输入电流脉冲的幅度,以加快向基区注入少子的速度(但基极电流也不能过大,否则将使存储时间延长)。

③存储时间ts:

存储时间就是晶体管从过饱和状态(集电结正偏的状态)退出到临界饱和状态(集电结0偏的状态)所需要的时间,也就是基区和集电区中的过量存储电荷消失的时间;。

而这些过量少子存储电荷的消失主要是依靠复合作用来完成,所以从器件设计来说,减短存储时间的主要措施有如:

在集电区掺Au等来减短集电区的少子寿命(以减少集电区的过量存储电荷和加速过量存储电荷的消失;但是基区少子寿命不能减得太短,否则会影响到电流放大系数),尽可能减小外延层厚度(以减少集电区的过量存储电荷)。

而从晶体管使用来说,减短存储时间的主要措施有如:

基极输入电流脉冲的幅度不要过大(以避免晶体管饱和太深,使得过量存储电荷减少),增大基极抽取电流(以加快过量存储电荷的消失速度)。

④下降时间tf:

下降时间的过程与上升时间的过程恰巧相反,即是让临界饱和时基区中的存储电荷逐渐消失的一种过程。

因此,为了减短下降时间,就应该减少存储电荷(减小结面积、减小基区宽度)和加大基极抽取电流。

总之,为了减短晶体管的开关时间、提高开关速度,除了在器件设计上加以考虑之外,在晶体管使用上也可以作如下的考虑:

a)增大基极驱动电流,可以减短延迟时间和上升时间,但使存储时间有所增加;b)增大基极抽取电流,可以减短存储时间和下降时间。

图2

(2)晶体管的增速电容器:

在BJT采用电压驱动时,虽然减小基极外接电阻和增大基极反向电压,可以增大抽取电流,这对于缩短存储时间和下降时间都有一定的好处。

但是,若基极外接电阻太小,则会增大输入电流脉冲的幅度,将使器件的饱和程度加深而反而导致存储时间延长;若基极反向电压太大,又会使发射结反偏严重而增加延迟时间,所以需要全面地进行折中考虑。

可以想见,为了通过增大基极驱动电流来减短延迟时间和上升时间的同时、又不要增长存储时间和产生其它的副作用,理想的基极输入电流波形应该是如图2所示阶梯波的形式,这样的阶梯波输入即可克服上述矛盾,能够达到提高开关速度的目的。

实际上,为了实现理想的基极电流波形,可以方便地采用如图3所示的基极输入回路(微分电路),图中与基极电阻RB并联的CB就称为增速电容器。

在基极输入回路中增加一个增速电容器之后,虽然输入的电流波形仍然是方波,但是通过增速电容器的作用之后,所得到的实际基极输入电流波形就变得很接近于理想的基极电流波形了,于是就可以减短开关时间、提高开关速度。

问题5:

达林顿管与普通三极管有什么不同?

组成复合管的两个晶体管,可以是同极性的,也可以是不同极性的三极管,复合管的极性与前面第一个三极管的极性相同。

与单个三极管相比,复合管的特性有:

1、电流放大系数很大,近似为两个三极管电流放大系数之积;

2、输入阻抗很高,是第二个三极管输入阻抗与第一个三极管的电流放大系数之积;

3、电路稳定性差。

受温度影响时,复合管的电流放大系数、穿透电流的变化远比单个三极管大;

4、复合管的截止频率比单管低,高频特性差。

问题6:

什么是三极管的软击穿?

三极管的击穿是指三极管的PN结不能产生压降限制电流的现象。

击穿时PN结的温度上升,如果还没有破坏PN结的结构,则造成击穿的条件去除后,PN结的功能能够得到恢复或部分恢复,就可认为不是硬击穿或称为软击穿。

若温度上升太高,PN结的结构完全破坏,击穿的条件去除后,PN结的功能就不能得到恢复,这种击穿称为硬击穿。

硬击穿的三极管不能正常工作,通常说烧坏了,需要更换。

出现软击穿的三极管,性能也已经下降很多,一般也应该进行更换,但应急情况下还可暂时坚持工作,只是随时都可能变成硬击穿而完全不能工作。

问题7均匀基区PNP少子浓度分布

问题8:

均匀基区PNP的能带图

问题9:

基区输运系数

问题10:

提高基区输运系数的方法

问题11:

基区渡越时间

问题12:

发射结注入效率

问题13:

小电流时放大系数的下降

问题14:

发射区重掺杂效应

问题15:

基区陷落效应

问题16:

LEC晶体管

问题17:

异质结双极性晶体管

问题18:

基区宽度调制效应

问题19:

基区穿通

问题20:

基区电阻

问题21:

基区扩展效应

问题22:

发射结电流集边效应

问题23:

二次击穿

问题24:

晶体管的安全工作区

问题25:

提高开关速度的方法

问题26:

降低基区电阻的方法

非工作基区重掺杂,深结深,基极接触孔下重掺杂。

但工作基区掺杂浓度不宜不过高,否则会使发射结注入效率下降,基区少子迁移率下降,渡越时间增加,发射结电容增加,发射结击穿电压下降。

问题27:

问题28:

问题29: