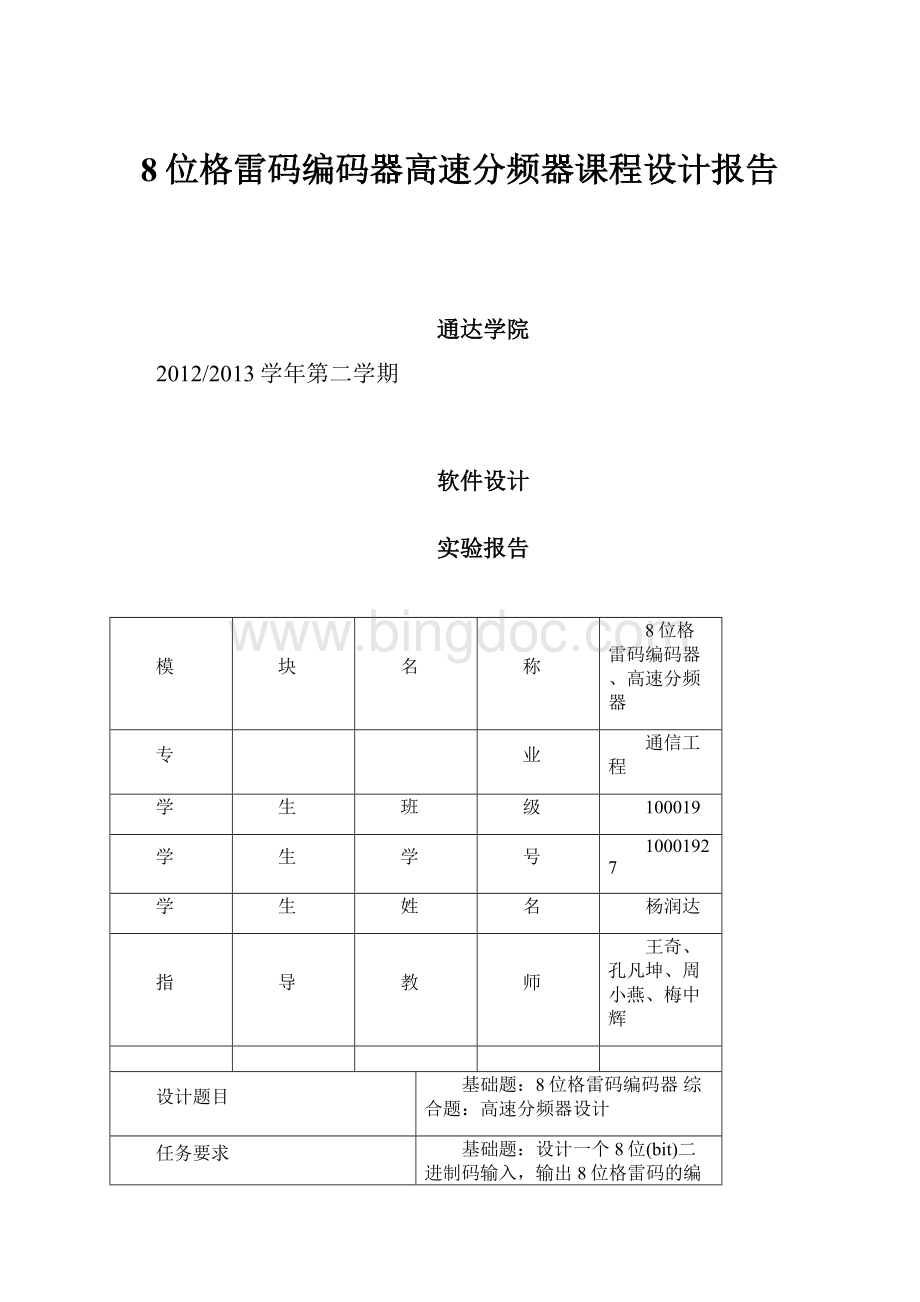

8位格雷码编码器高速分频器课程设计报告Word文档格式.docx

《8位格雷码编码器高速分频器课程设计报告Word文档格式.docx》由会员分享,可在线阅读,更多相关《8位格雷码编码器高速分频器课程设计报告Word文档格式.docx(14页珍藏版)》请在冰点文库上搜索。

B7---B0并行8位,输出G7---G0并行8位,提示:

当i<

7时:

G(i)=B(i+1)xorB(i),G(7)=B(7))。

综合题:

有一个10MHz的时钟源,为得到4Hz,3Hz,2Hz和1Hz的信号,请设计一种分频器。

实验设备

及软件

QuartusII9.0

同组人员

学号及姓

无

参考文献

[1]王振红,VHDL电路设计与应用实践教程:

机械工业出版社。

[2]徐向民,数字系统设计及VHDL实践:

[3]毛为勇,祁中洋,王兰,基于FPGA的任意小数分频器的设计:

桂林航天工业高等专科学校学报

实验目的:

8位格雷码编码器及高速分频器设计

1.全面了解如何应用该硬件描述语言进行高速集成电路设计

2.通过软件使用、设计与仿真环节使学生熟悉EDA-VHDL开发环境

3.通过对基本题、综合题的设计实践,使学生掌握硬件系统设计方法(自底向上或自顶向下),熟悉VHDL语言三种设计风格,并且培养应用VHDL语言解决实际问题的能力。

实验设备:

PC机

实验课题:

一、8位格雷码编码器

1、主要功能

设计一个8位(bit)二进制码输入,输出8位格雷码的编码器(输入:

B7---B0并行8位,输出G7---G0并行8位,提示:

当i<

7时:

G(i)=B(i+1)xorB(i),G7)=B⑺。

2、设计原理

根据组合逻辑电路的分析方法,先列出其真值表再通过卡诺图化简,可以很快的找出格雷码与二进制码之间的逻辑关系。

其转换规律为:

高位同,从高到低看异同,异出‘1'

同出‘0'

也就是将二进制码转换成格雷码时,高位是完全相同的,下一位格雷码是‘1’还是‘0'

完全是相邻两位二进制码的“异”还是“同”来决定。

下面举一个简单的例子加以说明。

假如要把二进制码10110110转换成格雷码,则可以通过下面的方法来完成,方法如图1-1。

二进制码:

Gr町码;

1-1

3、功能仿真

说明:

B7~B0为输入信号,二进制码为:

10110110

G7~G0为输出信号,格雷码为:

11101101

4、实验代码:

见附录

二、高速分频器设计

1、主要功能

设计一个分频器,对lOMhz的时钟源进行分频,以得到4Hz,3Hz,2Hz,1Hz的时钟。

2、设计原理

CD整体思路

因为lOMhz时钟源速度很快,直接分频成1Hz级别的时钟的话分频系数太大,虽然思路简单,但是在实现时会造成quartus的寄存器资源消耗殆尽,导致编译失败。

所以我先通过10分频和100000分频将lOMhz时钟源分频为10Hz的时钟源,然后对10Hz的时钟源分别进行2.5分频,3.3分频,5分频,10分频。

从而得至U4Hz,3Hz,2Hz,1Hz的时钟源。

原理框图如图2-1所示。

图2-1

(02.5分频模块原理

设计一个模3的计数器,再设计一个扣除脉冲电路,加在模3计数器输出

之后,每来两个脉冲就扣除一个脉冲(实际上是使被扣除的脉冲变成很窄的脉冲,可由异或门实现),就可以得到分频系数为2.5的小数分频器。

设需要设计一个分频系数为N-0.5的分频器,其电路可由一个模N计数器、一个二分频器和一个异或门组成,如图2-2所示。

在实现时,模N计数器可设计成带预置的计数器,这样就可以实现任意分频系数为N-0.5的分频器。

电路原理图如图2-2所示。

图2-2

③3.3分频模块设计[3]

设置一个计数器,令其初始值为0;

在时钟源elk的每一个上升沿,计数器加上Q,若计数器里面的值小于P,则发出删除一个脉冲的信号,将delete置为低电平;

若其值大于P,则将计数器的值减去P,并且将delete置为高电平,不发出删除脉冲的信号。

本实验中要将一个10Hz的时钟源分频为3Hz的时钟信号,则Q=3P=10b

电路原理图如图2-3所示。

图2-3

45分频模块设计

定义两个计数器,分别对输入时钟的上升沿和下降沿进行计数,然后把这两个计数值输入一个组合逻辑,用其控制输出时钟的电平。

这是因为计数值为奇数,占空比为50%,前半个和后半个周期所包含的不是整数个elkin的周期。

5分频,前半个周期包含2.5个elkin周期,后半个周期包含2.5个elkin周期。

510分频模块设计

定义一个计数器对输入时钟进行计数,在计数的前一半时间里,输出高电

平,在计数的后一半时间里,输出低电平,这样输出的信号就是占空比为50%

的偶数分频信号。

10分频,计数值为0~4输出高电平,计数值为5~9输出低电平。

由于题目所给的lOMhz时钟信号频率过大,如果直接对它进行分频的话将难以看到完整的结果,但如果将仿真时间调长,则仿真速度过慢,所以在仿真中,我将第一次分频的分频系数调低,然后选择适当的输入时钟频率,以验证2.5分

频,3.3分频,5分频,10分频的正确性。

仿真结果如图2-4所示。

EIri

◎知

T」hr

Uhkx

初0blUDQMro.c4tDabtftM4HDfjSQ.Ob*STC0uflIODm»

D.DUApbiTID.Dm

I■II・p--;

IptI

L

—1r—niir—i]1

n,一一一n,■一n.,,口,,,,n...n...n....n...n...n...

.m

图2-4

4、实验代码见附录二

设计总结

本实验主要是运用VHDL语言实现格雷码编码器和高速分频器的设计,相对于其他的来说,本实验比较简单,但在实际做的时候还是遇到不少的问题。

在编译时出现了许多错误,经过反复修改编译,再修改再编译最终排除了所有的错误。

在仿真时一开始看不到完整的结果,通过调节分频系数以及输入时钟频率的等手段仿真成功,验证了2.5分频,3.3分频,5分频,10分频的正确性。

收获和体会

在老师布置好题目后,我仔细进行设计,通过查阅各参考书,最终把实验做出来了,达到了老师对本实验的要求。

在这次设计中我收获颇丰,首先最直接的收获就是我巩固了这节课所学的知识,把它运用到实践中去,并且学到了许多在课本中所没有的知识,通过查阅相关知识,进一步加深对EDA的了解。

其次,我们不管做什么都不能粗心,如我们在输入程序是,把字母打错了时,保存文件时命名与程序中的名称不一样时,都会导致编译错误,在此过程中虽然浪费了不少时间,但这也让我注意到在实际做设计时应该注意的问题,意识到自己的不足,对学过的知识了解不够深刻,掌握的不足够。

总的来说,这次设计还算成功,也让我明白了要把理论知识与实践结合起来,从实践中强化自己的理论,才能更好提高自己的实际动手能力和独立思考能力。

如果在设计过程中遇到问题时,我们要有耐心并细心的查找错误,这也是学习的过程。

附录

格雷码编码器源代码

libraryieee;

useieee.std_logic_1164.all;

entitygreenis

port(B:

instd_logic_vector(7downto0);

G:

outstd_logic_vector(7downto0));

endgreen;

architecturecodeofgreenisbegin

G(7)<

=B(7);

G(6)<

=B(7)XORB(6);

G(5)<

=B(6)XORB(5);

G(4)<

=B(5)XORB(4);

G(3)<

=B(4)XORB(3);

G

(2)<

=B(3)XORB

(2);

G

(1)<

=B

(2)XORB

(1);

G(0)<

=B

(1)XORB(0);

endcode;

附录二

高速分频器源代码

useieee.std_logic_signed.all;

useieee.std_logic_unsigned.all;

entitydiv2isgeneric(N10:

integer:

=10;

N105:

=100000;

N3:

=3;

N5:

=5;

N2:

N10:

=10);

port(cp_10mhz:

instd_logic;

delete:

bufferstd_logic;

cp_10hz:

outstd_logic;

cp_4hz:

bufferstd_logic;

cp_3hz:

cp_2hz:

cp_1hz:

outstd_logic--tempout:

inoutstd_logic);

enddiv2;

architectureclkofdiv2issignalcp1mhz:

std_logic;

signalcnt_1mhz:

integerrange0toN10-1;

signalcp10hz:

signalcnt_10hz:

integerrange0toN105-1;

signalcnt_1hz:

signalcnt_2hz1,cnt_2hz2:

integerrange0toN5-1;

signalcnt_3hz:

integer:

=0;

SIGNALclk_4hz,dix:

STD_LOGIC;

SIGNALcnt_4hz:

constantP:

integer:

constantQ:

--SIGNALdelete:

std_logic;

begin

clk_4hz<

=cp10hzXORdix;

--clk<

=cp10hzxordiv2;

process(cp_10mhz)--计数1Mhz

if(cp_10mhz'

eventandcp_10mhz='

1'

)thenif(cnt_1mhz<

N10-1)thencnt_1mhz<

=cnt_1mhz+1;

else

cnt_1mhz<

=0;

endif;

endprocess;

process(cnt_1mhz)--根据计数值,控制输出时钟脉冲的高、低电平begin

if(cnt_1mhz<

N10/2)then

cp1mhz<

='

;

0'

10Hz

process(cp1mhz)--计数

if(cp1mhz'

eventandcp1mhz='

)thenif(cnt_10hz<

N105-1)thencnt_10hz<

=cnt_10hz+1;

elsecnt_10hz<

endif;

process(cnt_10hz)--根据计数值,控制输出时钟脉冲的高、低电平begin

if(cnt_10hz<

N105/2)then

cp10hz<

cp_10hz<

endprocess;

1Hz

process(cp10hz)--计数

if(cp10hz'

eventandcp10hz='

)thenif(cnt_1hz<

N10-1)thencnt_1hz<

=cnt_1hz+1;

else

cnt_1hz<

process(cnt_1hz)--根据计数值,控制输出时钟脉冲的高、低电平begin

if(cnt_1hz<

cp_1hz<

2Hz

process(cp10hz)

)then--shangshengyanjishuif(cnt_2hz1<

N5-1)thencnt_2hz1<

=cnt_2hz1+1;

cnt_2hz1<

process(cp10hz)

beginif(cp10hz'

)then--xiajiangyanjishuif(cnt_2hz2<

N5-1)then

cnt_2hz2<

=cnt_2hz2+1;

cp_2hz<

whencnt_2hz1<

(N5-1)/2orcnt_2hz2<

(N5-1)/2else'

process(clk_4hz)

if(clk_4hz'

eventandclk_4hz='

)thenif(cnt_4hz=0)thencnt_4hz<

=N2-1;

cp_4hz<

cnt_4hz<

=cnt_4hz-1;

--模N计数器减法计数cp_4hz<

process(cp_4hz)

beginif(cp_4hz'

eventandcp_4hz='

)thendix<

=notdix;

--输出时钟二分频endif;

4Hz

--置整数分频值N

)thencnt_3hz<

=cnt_3hz+Q;

if(cnt_3hz<

P)thendelete<

='

elsecnt_3hz<

=cnt_3hz-P;

delete<

process(cp10hz,delete)begin

cp_3hz<

=cp10hzanddelete;

endclk;

3hz

设计成绩评定

评分内容

具体要求

总分

评分

上机时间

上机时间是否达到要求的学时,按照实际情况给与一定的成绩。

10分

报告审阅结果

报告结构严谨,文字通顺,用语符合技术规范,图表清楚,书写格式规范,不与别人雷同。

30分

验收结果

原理

原理清楚,能较好地理解课题任务并提出实施方案。

20分

完成情况

独立完成规定设计任务,论证、分析、设计、计算、结构、建模、实验正确合理,有一定的创新。

操作

能熟练操作相关工具软件,并利用工具软件完成设计任务。

总成绩(五分制)

100分