EDA技术复习要点课件Word格式.docx

《EDA技术复习要点课件Word格式.docx》由会员分享,可在线阅读,更多相关《EDA技术复习要点课件Word格式.docx(18页珍藏版)》请在冰点文库上搜索。

INSTD_LOGIC_VECTOR(1DOWNTO0);

--输入选择信号

a,b,c,d:

INSTD_LOGIC;

--输入信号

y:

OUTSTD_LOGIC);

--输出端

ENDENTITY;

ARCHITECTUREARTOFMUX41IS

BEGIN

PROCESS(s)

IF(S="

00"

)THENy<

=a;

ELSIF(S="

01"

)THENy<

=b;

10"

=c;

11"

=d;

ELSEy<

=NULL;

ENDIF;

EDNPROCESS;

ENDART;

ENDMUX41;

CASEsIS

WHEN“00”=>

y<

WHEN“01”=>

WHEN“10”=>

WHEN“11”=>

WHENOTHERS=>

NULL;

ENDCASE;

ENDPROCESS;

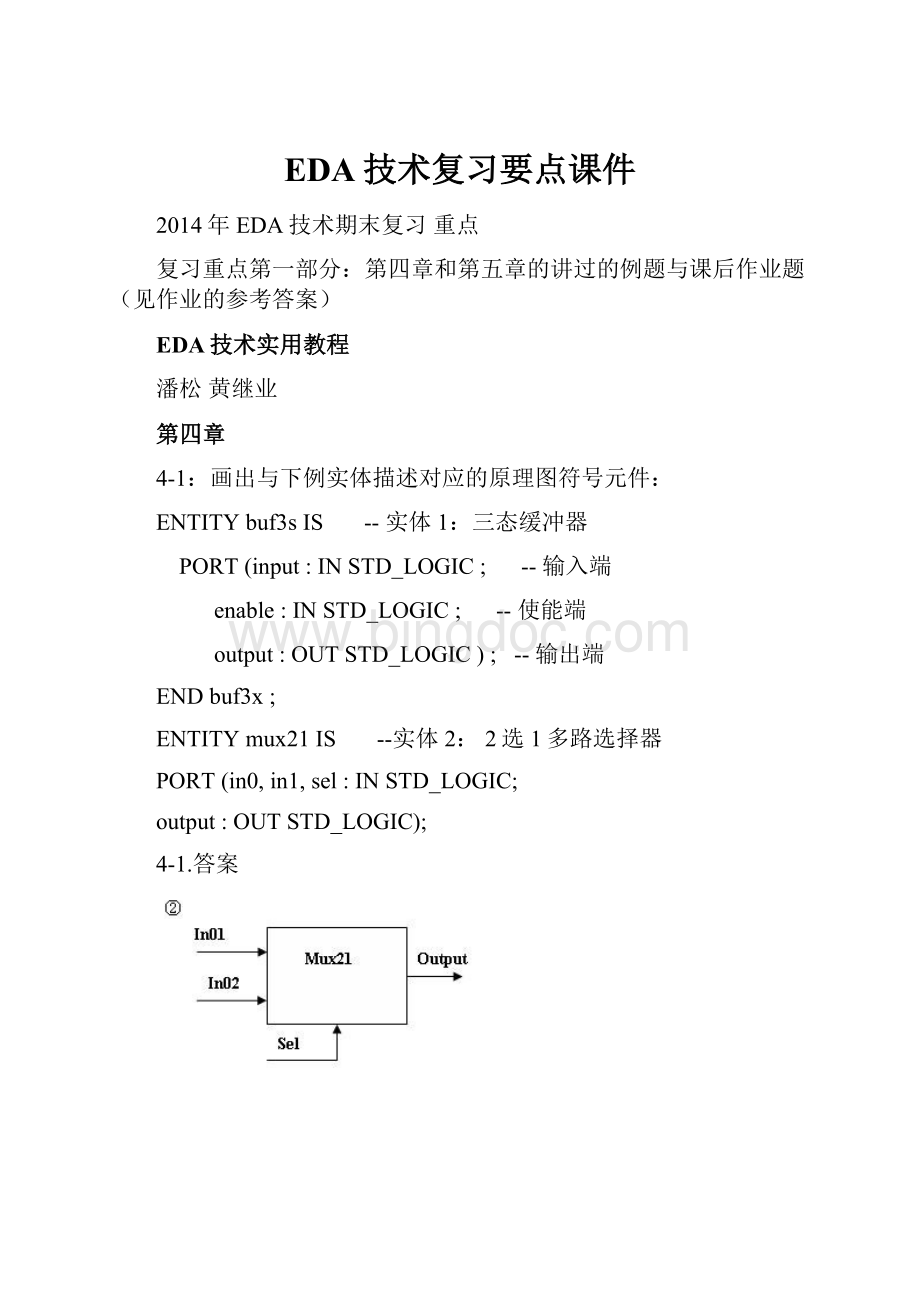

4-3.图4-38所示的是双2选1多路选择器构成的电路MUXK,对于其中MUX21A,当s='

和'

时,分别有y<

='

a'

和y<

b'

。

试在一个结构体中用两个进程来表达此电路,每个进程中用CASE语句描述一个2选1多路选择器MUX21A。

4-3.答案

ENTITYMUX221IS

PORT(a1,a2,a3:

s0,s1:

outy:

ARCHITECTUREONEOFMUX221IS

SIGNALtmp:

STD_LOGIC;

PR01:

PROCESS(s0)

IFs0=”0”THENtmp<

=a2;

ELSEtmp<

=a3;

PR02:

PROCESS(s1)

IFs1=”0”THENouty<

=a1;

ELSEouty<

=tmp;

ENDARCHITECTUREONE;

4-4.下图4-39是一个含有上升沿触发的D触发器的时序电路,试写出此电路的VHDL设计文件。

4-4.答案

ENTITYMULTIIS

PORT(CL:

CLK0:

OUT1:

ARCHITECTUREONEOFMULTIIS

SIGNALQ:

PROCESS(CLK0)

IFCLK‘EVENTANDCLK=’1’

THENQ<

=NOT(CLORQ);

ELSE

OUT1<

=Q;

4-5.给出1位全减器的VHDL描述。

要求:

(1)首先设计1位半减器,然后用例化语句将它们连接起来,图3-32中h_suber是半减器,diff是输出差,s_out是借位输出,sub_in是借位输入。

(2)以1位全减器为基本硬件,构成串行借位的8位减法器,要求用例化语句来完成此项设计(减法运算是x–y-sun_in=diffr)

4-5.答案

底层文件1:

or2a.VHD实现或门操作

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYor2aIS

PORT(a,b:

c:

ENDENTITYor2a;

ARCHITECTUREoneOFor2aIS

c<

=aORb;

ENDARCHITECTUREone;

底层文件2:

h_subber.VHD实现一位半减器

ENTITYh_subberIS

PORT(x,y:

diff,s_out:

:

ENDENTITYh_subber;

ARCHITECTUREONEOFh_subberIS

SIGNALxyz:

STD_LOGIC_VECTOR(1DOWNTO0);

xyz<

=x&

y;

PROCESS(xyz)

BEGIN

CASExyzIS

WHEN"

=>

diff<

;

s_out<

NULL;

顶层文件:

f_subber.VHD实现一位全减器

ENTITYf_subberIS

PORT(x,y,sub_in:

diffr,sub_out:

ENDENTITYf_subber;

ARCHITECTUREONEOFf_subberIS

COMPONENTh_subber

diff,S_out:

ENDCOMPONENT;

COMPONENTor2a

c:

SIGNALd,e,f:

u1:

h_subberPORTMAP(x=>

x,y=>

y,diff=>

d,s_out=>

e);

u2:

d,y=>

sub_in,diff=>

diffr,s_out=>

f);

u3:

or2aPORTMAP(a=>

f,b=>

e,c=>

sub_out);

ENDARCHITECTUREART;

4-6.根据图4-41,写出顶层文件MX3256.VHD的VHDL设计文件。

4-6.答案

MAX3256顶层文件

ENTITYMAX3256IS

PORT(INA,INB,INCK:

INC:

E,OUT:

ENDENTITYMAX3256;

ARCHITECTUREONEOFMAX3256IS

COMPONENTLK35--调用LK35声明语句

PORT(A1,A2:

CLK:

Q1,Q2:

COMPONENTD--调用D触发器声明语句

PORT(D,C:

Q:

COMPONENTMUX21--调用二选一选择器声明语句

PORT(B,A:

S:

C:

SIGNALAA,BB,CC,DD:

LK35PORTMAP(A1=>

INA,A2=>

INB,CLK=INCK,Q1=>

AA,Q2=>

BB);

DPORTMAP(D=>

BB;

CLK=>

INCK,C=>

INC,Q=>

CC);

LK35PORTMAP(A1=>

BB,A2=>

CC,CLK=INCK,Q1=>

DD,Q2=>

OUT1);

u4:

MUX21PORTMAP(B=>

AA,A=>

DD,S=>

BB,C=>

E);

4-7用例化语句写出下图所示的的顶层文件

1、首先编写底层元件adder_1,使其为带使能控制端口的半加器。

ENTITYadder_1IS

PORT(a,b:

co,so:

ENDENTITYadder_1;

ARCHITECTUREfh1OFadder_1is

so<

=NOT(aXOR(NOTb));

co<

=aANDb;

ENDARCHITECTUREfh1;

2、使用VHDL元件例化语句完成下图所示的顶层文件

libraryieee;

useieee.std_logic_1164.all;

ENTITYadder_2is

port(a1,a0,b1,b0,ci:

instd_logic;

s1,s2,co:

outstd_logic);

endadder_2;

architectureoneofadder_2is

componentadder_1

port(x,y,cin:

cout,sum:

endcomponent;

signaltemp:

std_logic;

begin

adder_1portmap(x=>

a1,y=>

a0,cin=>

ci,sum=>

s1;

cout=>

temp);

b1,y=>

b0,cin=>

temp,sum=>

s2;

co);

endone;

第五章

5-1什么是固有延时?

什么是惯性延时?

P139

答:

固有延时(InertialDelay)也称为惯性延时,固有延时的主要物理机制是分布电容效应。

5-2δ是什么?

在VHDL中,δ有什么用处?

P140

δ是什么?

答:

在VHDL仿真和综合器中,默认的固有延时量(它在数学上是一个无穷小量),被称为δ延时。

在VHDL信号赋值中未给出固有延时情况下,VHDL仿真器和综合器将自动为系统中的信号赋值配置一足够小而又能满足逻辑排序的延时量δ;

使并行语句和顺序语句中的并列赋值逻辑得以正确执行。

5-4说明信号和变量的功能特点,以及应用上的异同点。

P117~P118

变量:

变量是一个局部量,只能在进程和子程序中使用。

变量不能将信息带出对它做出定义的当前结构。

变量的赋值是一种理想化的数据传输,是立即发生的,不存在任何延时行为。

变量的主要作用是在进程中作为临时的数据存储单元。

信号:

信号是描述硬件系统的基本数据对象,其性质类似于连接线;

可作为设计实体中并行语句模块间的信息交流通道。

信号不但可以容纳当前值,也可以保持历史值;

与触发器的记忆功能有很好的对应关系。

5-5在VHDL设计中,给时序电路清零(复位)有两种力方法,它们是什么?

解:

设Q定义成信号,一种方法:

Q<

=“000…000”;

其中“000…000”反映出信号Q的位宽度。

第二种方法:

=(OTHERS=>

‘0’);

其中OTHERS=>

‘0’不需要给出信号Q的位宽度,即可对Q清零。

5-6在描述时序电路的进程中,哪一种复位方法必须将复位信号放在敏感信号表中?

给出这两种电路的VHDL描述。

边沿触发复位信号要将复位信号放在进程的敏感信号表中。

(1)边沿触发复位信号

…………………….

ARCHITECTUREbhv0FDFF3IS

SIGNALQQ:

STD_LOGIC;

BEGIN

PROCESS(RST)

IFRST’EVENTANDRST=‘1'

THEN

QQ<

=(Others=>

‘0’);

ENDIF;

ENDPROCESS;

Q1<

=QQ;

END;

………………………

(2)电平触发复位信号

PROCESS(CLK)

IFRST=‘1'

5-7什么是重载函数?

重载算符有何用处?

如何调用重载算符函数?

(1)什么是重载函数?

根据操作对象变换处理功能。

(2)重载算符有何用处?

用于两个不同类型的操作数据自动转换成同种数据类型,并进行运算处理。

(3)如何调用重载算符函数?

采用隐式方式调用,无需事先声明。

5-8判断下面三个程序中是否有错误,若有则指出错误所在,并给出完整程序。

程序1:

SignalA,EN:

std_logic;

…………………

Process(A,EN)

VariableB:

std_logic;

Begin

ifEN=lthenB<

=A;

endif;

--将“B<

=A”改成“B:

=A”

endprocess;

程序2:

Architectureoneofsampleis

variablea,b,c:

integer;

begin

c<

=a+b;

--将“c<

=a+b”改成“c:

=a+b”

end;

程序3:

libraryieee;

useieee.std_logic_1164.all;

entitymux21is

PORT(a,b:

sel:

instd_loglc;

outstd_logle;

);

--将“;

)”改成“)”

endsam2;

--将“sam2”改成“entitymux21”

architectureoneofmux2lis

--增加“process(a,b,sel)begin”

ifsel='

thenc:

elsec:

--应改成“ifsel='

thenc<

elsec<

”

--增加“endprocess;

endtwo;

--将“two”改成“architectureone”

5-9设计含有异步清零和计数使能的16位二进制加减可控计数器。

5-9.答案:

ENTITYCNT16IS

PORT(CLK,RST,EN:

CHOOSE:

INBIT;

SETDATA:

BUFFERINTEGERRANCE65535DOWNTO0;

COUT:

BUFFERINTEGERRANCE65535DOWNTO0);

ENDCNT16;

ARCHITECTUREONEOFCNT16IS

PROCESS(CLK,RST,SDATA)

VARIABLEQI:

STD_LOGIC_VECTOR(65535DOWNTO0);

IFRST='

THEN--计数器异步复位

QI:

'

ELSIFSET=’1’THEN--计数器一步置位

QI:

=SETDATA;

ELSIFCLK'

EVENTANDCLK='

THEN--检测时钟上升沿

IFEN=’1’THEN–检测是否允许计数

IFCHOOSE=’1’THEN--选择加法计数

=QI+1;

--计数器加一

ELSEQI=QI-1;

COUT<

=QI;

--将计数值向端口输出

ENDONE;

复习重点第二部分:

一下为本书中必须掌握的主要知识点,大家对照课本进行总结,深入领会

1、从执行方式看VHDL的描述语句包括那些描述语句?

2、目前流行的硬件描述语言有那些?

3、MAX+PLUS2中各种文件的扩展名有哪些?

4、基于MAX+PLUS2的设计流程

5、目前较流行的EDA设计软件有那些?

6、可编程逻辑器件的分类?

按照变成工艺分哪些类。

VHDL程序设计中常用的库有那些?

哪些库是显式(默认打开的)的,哪些是隐式的?

设计的现行工作库是什么?

7、程序包由那两部分组成?

分别有什么作用?

8、常用的预定义程序包有哪些?

如何调用?

9、目前国际上较大的EDA器件制造公司有那些?

10、VHDL常用的预定义数据类型有哪几种,分别在哪些程序包中?

11、数据类型的转换有哪几种方法?

12、可以构成标识符的字符有?

13、可编程器件(PLD)分为哪两类

14、标准逻辑位数据类型常用的数值有哪几种?

15、完整的条件语句将产生什么电路,不完整的条件语句将产生什么电路。

16、信号和变量有什么区别?

P121

17、VHDL作为工业标准,是由那个机构制定并公布的。

18、实体部分的端口模式有四个类型。

19、从执行方式看VHDL的基本描述语句包括哪两大基本描述语句?

20、VHDL文件存盘时,其主文件名应与实体名一致,扩展名应为什呢

21、硬件描述语言(HDL)的种类很多?

22、EDA技术的含义。

23、目前较流行的集成EDA开发环境(软件)有那些?

24、简述EDA技术的CPLD/FPGA的设计流程。

25、写出实体中的PORT语句结构并说明其作用。

26、简述EDA技术经历了那几个发展阶段。

27、写出元件例化语句语句格式,并说明其作用。

28、试比较图形输入法和文本输入法有何优缺点?

29、结构体的语言格式与作用。

30、写出PROCESS语句结构的一般表达格式?

31、进程语句的设计(或使用)要点?

32、并行信号赋值语句有哪几种?

其语句格式为何?

33、EDA技术常用的输入方法有?

34、什么是实体和结构体,其功能是什么?

,

35、MAX+pulsⅡ的原理图输入法、文本输入法、波形输入法生成的文件扩展名为?

36、VHDL的操作符有那几大类?

每一类的操作符分别是什么?

每一类操作符可以对那些数据进行操作(运算)?

37、VHDL操作符的优先级?

38、结构体常见的功能语句有那些?

39、子程序分为那两类,其结构为什么。

P152-153

40、VHDL的标识符由什么构成。

41、CASE语句的一般形式?

在使用当中的注意事项。

P125-126

42、试着比较IF和CASE语句的差异?

P127

43、FOR循环语句的一般形式?

44、VHDL数据对象有哪几种?

其语句格式如何

45、变量和信号的区别?

46、VHDL常用的数据有哪些?

枚举型的数据类型?

47、实现时序电路和逻辑组合电路分别用什