《超大规模集成电路设计》考试习题含答案完整版Word格式.docx

《《超大规模集成电路设计》考试习题含答案完整版Word格式.docx》由会员分享,可在线阅读,更多相关《《超大规模集成电路设计》考试习题含答案完整版Word格式.docx(14页珍藏版)》请在冰点文库上搜索。

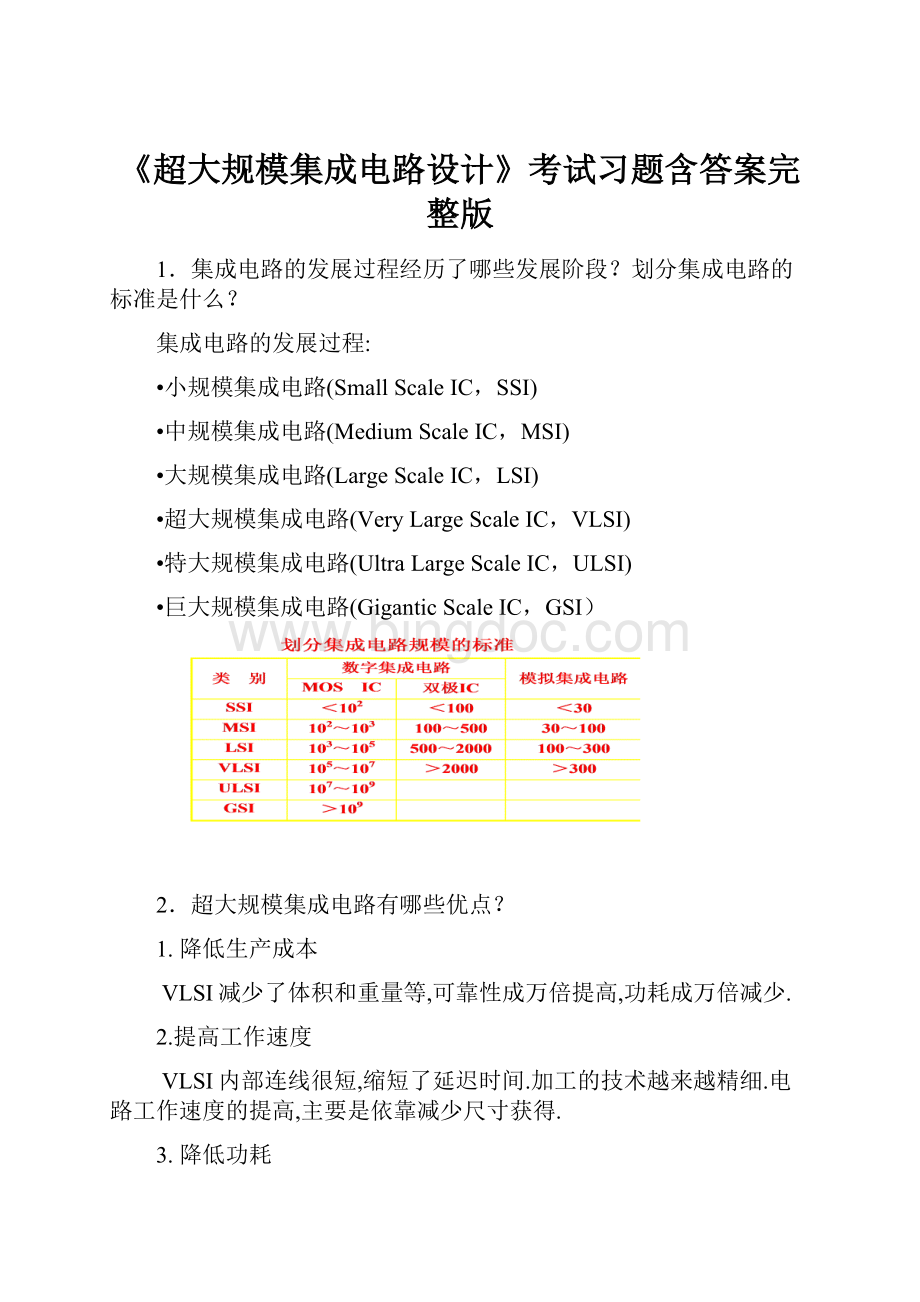

芯片内部电路受干扰小,电路可简化.

5.优越的可靠性

采用VLSI后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。

6.体积小重量轻

7.缩短电子产品的设计和组装周期

一片VLSI组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度.

3.简述双阱CMOS工艺制作CMOS反相器的工艺流程过程。

1、形成N阱2、形成P阱3、推阱4、形成场隔离区5、形成多晶硅栅6、形成硅化物7、形成N管源漏区8、形成P管源漏区9、形成接触孔10、形成第一层金属11、形成第一层金属12、形成穿通接触孔13、形成第二层金属14、合金15、形成钝化层16、测试、封装,完成集成电路的制造工艺

4.在VLSI设计中,对互连线的要求和可能的互连线材料是什么?

互连线的要求

低电阻值:

产生的电压降最小;

信号传输延时最小(RC时间常数最小化)

与器件之间的接触电阻低

长期可靠工作

可能的互连线材料

金属(低电阻率),多晶硅(中等电阻率),高掺杂区的硅(注入或扩散)(中等电阻率)

5.在进行版图设计时为什么要制定版图设计规则?

—片集成电路上有成千上万个晶体管和电阻等元件以及大量的连线。

描述这些基本单元的版图,是一系列几何图形有规则的排列。

为了保证由这些基本单元及其相互连线构成的版图能够在工艺线上生产出来,必须制定版图设计规则。

在芯片尺寸尽可能小的前提下,使得即使存在工艺偏差也可以正确的制造出IC,尽可能地提高电路制备的成品率。

6.版图验证和检查主要包括哪些方面?

DRC(DesignRuleCheck):

几何设计规则检查;

对IC的版图做几何空间检查,保证能在特定的工艺条件下实现所设计的电路,并保证一定的成品率;

ERC(ElectricalRuleCheck):

电学规则检查;

检查电源(power)/地(ground)的短路,浮空的器件和浮空的连线等指定的电气特性;

LVS(LoyoutversusSchematic):

网表一致性检查;

将版图提出的网表和原理图的网表进行比较,检查电路连接关系是否正确,MOS晶体管的长/宽尺寸是否匹配,电阻/电容值是否正确等;

LPE(LayoutParameterExtraction):

版图寄生参数提取;

从版图中提取晶体管的尺寸、结点的寄生电容、连线的寄生电阻等参数,并产生SPICE格式的网表,用于后仿真验证;

POSTSIM:

后仿真,检查版图寄生参数对设计的影响;

提取实际版图参数、电阻、电容,生成带寄生量的器件级网表,进行开关级逻辑模拟或电路模拟,以验证设计出的电路功能的正确性和时序性能等,并产生测试向量。

7.版图设计规则是根据什么制定出来的?

为什么说它是集成电路的性能和集成度与成品率之间的折衷?

从图形如何精确地光刻到芯片上出发,可以确定一些对几何图形的最小尺寸限制规则,这些规则被称为设计规则。

设计规则是电路性能和成品率之间的折中,设计规则保守则成品率高,但电路面积大、性能差一些;

设计规则激进,则电路性能好、面积小,但成品率低。

8.简述设计规则与微米设计规则各自的优缺点?

以为单位:

把大多数尺寸(width,space等等)约定为的倍数

与工艺线所具有的工艺分辨率有关,是线宽偏离理想特征尺寸的上限以及掩膜版之间的最大套准偏差,一般等于栅长度的一半。

优点:

版图设计独立于工艺和实际尺寸,改变值就可以得到不同的设计规则;

缺点:

容易造成芯片面积浪费和工艺难度增加;

以微米为单位:

现代IC设计普遍采用的方法,每个尺寸之间没有必然的比例关系,提高每一尺寸的合理程度;

简化度不高。

9.标准单元法与门阵列法比较有何优点和缺点?

标准单元法与门阵列法比较有明显的优点:

(1)芯片面积的利用率比门阵列法要高。

芯片中没有无用的单元,也没有无用的晶体管。

(2)可以保证100%的连线布通率。

(3)单元可以根据设计要求临时加以特殊设计并加入库内,因而可以得到较佳的电路性能。

(4)可以与全定制设计法相结合功能块。

在芯片内放入经编译得到的宏单元或人工设计的功能块。

标准单元法也存在缺点和问题;

(1)原始投资大。

单元库的开发需要投入大量的人力物力;

当工艺变化时,单元的修改工作需要付出相当大的代价。

因而如何建立一个在比较长的时间内能适应技术发展的单元库是一个突出问题。

(2)成本较高。

由于掩膜版带要全部定制,芯片的加工也要经过全过程,因而成本较高。

因此只有芯片产量达到某一定额(几万至十几万),其成本才可接受。

10.随着工艺进入深亚微米,IC器件的物理实现出现了哪些方面的变化?

随着工艺进入深亚微米,IC器件的物理实现出现了以下3个方面的变化:

(1)逻辑单元的几何尺寸和逻辑单元之间的距离随着特征尺寸的减小而减小,从而使总延时减小。

(2)由于特征尺寸的减小,导线电阻增加。

为了抵消导线横向尺寸的减小,导线侧向尺寸即厚度被适度增加,以使导线电阻的增加不至于过大,从而导致纵向分布电容和边缘分布电容的增加,这两种分布电容都具有导致导线间耦合的性质。

(3)连线延时(主要是侧向分布电容和边缘分布电容引入的延时)在总延时中占据了主导地位,而输入延时也由于工作频率的提高而变得不容忽视。

11.FPGA与CPLD有何相似之处和不同之处?

FPGA是CPLD的一个发展最快的分支,复杂的可编程逻辑器件CPLD是由PLD或GAL发展而来.CPLD延伸出两大分支,即可擦除可编程的逻辑器件EPLD和现场可编程门阵列器件FPGA.

1.

CPLD

FPGA

内部结构

Product-term

Look-upTable

程序存储

内部EEPROM

SRAM,外挂EEPROM

资源类型

组合电路资源丰富

触发器资源丰富

集成度

低

高

使用场合

完成控制逻辑

能完成比较复杂的算法

速度

慢

快

其他资源

-

EAB,锁相环

保密性

可加密

一般不能保密

2.FPGA采用SRAM进行功能配置,可重复编程,但系统掉电后,SRAM中的数据丢失。

因此,需在FPGA外加EPROM,将配置数据写入其中,系统每次上电自动将数据引入SRAM中。

CPLD器件一般采用EEPROM存储技术,可重复编程,并且系统掉电后,EEPROM中的数据不会丢失,适于数据的保密。

3.FPGA器件含有丰富的触发器资源,易于实现时序逻辑,如果要求实现较复杂的组合电路则需要几个CLB结合起来实现。

CPLD的与或阵列结构,使其适于实现大规模的组合功能,但触发器资源相对较少。

4.FPGA为细粒度结构,CPLD为粗粒度结构。

5.FPGA为非连续式布线,CPLD为连续式布线。

12.可测试性设计的对象是什么?

为什么要从事VLSI的可测试性设计?

电路的可控制性和可观察性。

Pin数目有限,大量芯片内部的信息无法访问。

在尽可能少地增加附加引线脚和附加电路,并使芯片性能损失最小的情况下,满足电路可控制性和可观察性的要求。

13.为什么说MOS管的工作速度与

成反比?

提高MOS管的工作速度方法有哪些?

(见18题答案)

电子从源极运动到漏极所需的时间(MOS管的切换时间):

14.某CMOS电路负载电容近似等于

,

为标准反相器栅电容。

已知标准反相器的平均延迟时间

。

试求:

(1)用标准反相器直接驱动负载电容的延迟时间。

(2)用逐级放大反相器直接驱动负载电容的最小延迟时间。

15.什么是可测性设计?

可测性设计包括哪些技术?

可测试性包括哪些重要方面?

可测性设计:

在尽可能少地增加附加引线脚和附加电路,并使芯片性能损失最小的情况下,满足电路可控制性和可观察性的要求。

可测性设计技术:

主要包括分块测试技术、扫描测试技术、特征量分析分块测试技术、边界扫描分块测试技术等。

可测试性的三个重要方面:

故障模型的提取:

将电路失效抽象为故障模型。

测试生成:

产生验证电路的一组测试矢量。

测试设计:

考虑测试效率问题,加入适当的附加逻辑或电路以提高芯片的测试效率。

16.目前VLSI系统设计普遍采用的方法是什么?

它的基本思想什么?

试列举几种设计方法。

可编程逻辑器件设计方法(PLD方法)。

用户通过生产商提供的通用器件自行进行现场编程和制造,或者通过对与或矩阵进行掩膜编程,得到所需的专用集成电路。

PLA、PAL和GAL

FPGA和CPLD

17.半定制设计方法可分为哪几种方法?

它们各自的特点和不足之处是什么?

半定制的设计方法分为门阵列(GA:

GateArray)法和门海(GS:

SeaofGates)法两种。

门阵列方法的设计特点:

设计周期短,设计成本低,适合设计适当规模、中等性能、要求设计时间短、数量相对较少的电路。

不足:

设计灵活性较低;

门利用率低;

芯片面积浪费。

门海方法的设计特点:

门利用率高,集成密度大,布线灵活,保证布线布通率。

仍有布线通道,增加通道是单元高度的整数倍,布线通道下的晶体管不可用。

18.试分析提高MOS管工作速度方法。

1.提高IC加工精度减小沟道长度.

2.加强MOS管的驱动电压(Vgs-Vt),可以减小管子的内阻,加快工作速度。

3.由于,所以NMOS管的工作速度比PMOS管快得多。

可以用NMOS工艺代替PMOS工艺。

19.画出CMOS反相器电压传输特性曲线图,并写出相应的电流方程。

电流方程如下:

设Vtp=-Vtn