COF结构中键合力损伤芯片Al层的研究资料下载.pdf

《COF结构中键合力损伤芯片Al层的研究资料下载.pdf》由会员分享,可在线阅读,更多相关《COF结构中键合力损伤芯片Al层的研究资料下载.pdf(6页珍藏版)》请在冰点文库上搜索。

非导电膜;

金2金共金;

有限元模拟EEACC:

2550X;

0170J中图分类号:

TN306文献标识码:

A文章编号:

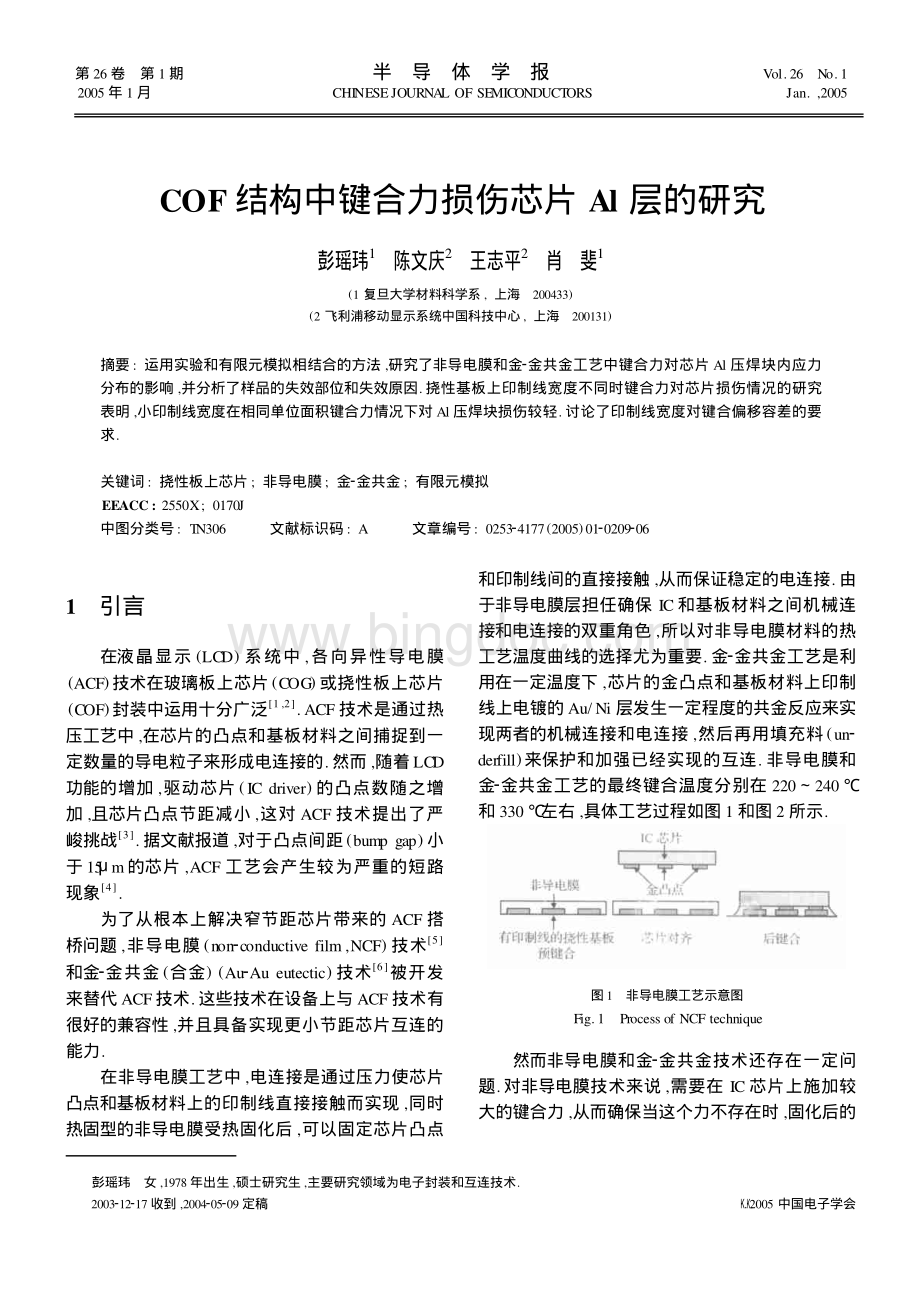

025324177(2005)01202092061引言在液晶显示(LCD)系统中,各向异性导电膜(ACF)技术在玻璃板上芯片(COG)或挠性板上芯片(COF)封装中运用十分广泛1,2.ACF技术是通过热压工艺中,在芯片的凸点和基板材料之间捕捉到一定数量的导电粒子来形成电连接的.然而,随着LCD功能的增加,驱动芯片(ICdriver)的凸点数随之增加,且芯片凸点节距减小,这对ACF技术提出了严峻挑战3.据文献报道,对于凸点间距(bumpgap)小于15m的芯片,ACF工艺会产生较为严重的短路现象4.为了从根本上解决窄节距芯片带来的ACF搭桥问题,非导电膜(non2conductivefilm,NCF)技术5和金2金共金(合金)(Au2Aueutectic)技术6被开发来替代ACF技术.这些技术在设备上与ACF技术有很好的兼容性,并且具备实现更小节距芯片互连的能力.在非导电膜工艺中,电连接是通过压力使芯片凸点和基板材料上的印制线直接接触而实现,同时热固型的非导电膜受热固化后,可以固定芯片凸点和印制线间的直接接触,从而保证稳定的电连接.由于非导电膜层担任确保IC和基板材料之间机械连接和电连接的双重角色,所以对非导电膜材料的热工艺温度曲线的选择尤为重要.金2金共金工艺是利用在一定温度下,芯片的金凸点和基板材料上印制线上电镀的Au/Ni层发生一定程度的共金反应来实现两者的机械连接和电连接,然后再用填充料(un2derfill)来保护和加强已经实现的互连.非导电膜和金2金共金工艺的最终键合温度分别在220240和330左右,具体工艺过程如图1和图2所示.图1非导电膜工艺示意图Fig.1ProcessofNCFtechnique然而非导电膜和金2金共金技术还存在一定问题.对非导电膜技术来说,需要在IC芯片上施加较大的键合力,从而确保当这个力不存在时,固化后的图2金2金共金工艺示意图Fig.2ProcessofAu2Aueutectictechnique非导电膜层能够固定住已经实现机械连接和电连接的芯片凸点.这个较大的键合力在键合工艺的瞬间可能对芯片凸点上面的Al压焊块造成损伤,并且可能会在Al压焊块中形成大的应力集中,从而对芯片的可靠性产生影响.Al压焊块的损伤对非导电膜技术正常电功能的实现无疑有致命的影响.而对金2金共金工艺来说,由于采用比非导电膜工艺更高的键合力和工艺温度,更加剧了上述问题所带来的损伤.本文用实验测试和ANSYS有限元模拟分析相结合的方法,研究了非导电膜和金2金共金工艺中不产生失效的最大键合压力,并探究了产生失效的原因.在此基础上通过改变印制线宽度来避免键合时在Al压焊块中造成的大应力集中.考虑到在实际键合过程中存在偏移容差,讨论了偏移容差对改变印制线宽度的限制范围.2实验及模拟2.1实验实验采用的IC芯片是几何尺寸为1018mm1195mm,厚度为381m(不包括凸点高度)的BOA(bumponactive)芯片,凸点的几何尺寸为30m99m15m,Al压焊块厚度为011m.采用的挠性基板厚度为35m,挠性基板上印制线横截面为梯形,两种印制线上/下底宽度分别为25/31m和17/23m,厚度均为1313m(包括Ni/Au层厚度).将上述部件按照非导电膜工艺和金2金共金工艺在键合力分别为7,9,11和14kgf的条件下制样,制样单位为100片.随后对所制样品进行电功能测试.2.2模拟有限元模拟可以分析封装工艺过程中及封装后模块中的应力分布7.利用ANSYS有限元分析软件对非导电膜和金2金共金工艺在键合瞬间结构内部的应力分布情况进行了模拟.在本文的模拟中,只考虑机械应力,未考虑热固化工艺后所产生的热应力.由于在键合的瞬间非导电膜没有固化,因此考虑到非导电膜工艺和金2金共金工艺的力学状态一致,没有将非导电膜建模.模拟进行2D有限元分析,几何模型示意图如图3所示.所采用芯片的几何参数和实验情况一致.挠性基板印制线宽度取上底数值,分别为17m和25m.图3有限元模型键合单元示意图Fig.3SchemeofabondingunitofFEA模拟中使用的材料参数取自文献8,9,列于表1.表1有限元模拟中采用的材料参数Table1MaterialparametersusedinFEsimulation材料杨氏模量/(Nmm-2)泊松比硅1310000.30铝655260.35金780000.30铜1210000.35挠性基板42000.30有限元单元类型采用PLANE182平面应变类型,具体的网络划分情况如图4所示,采用映射网络划分方法.负载条件与实验相同,分别为7,9,11和14kgf.3结果与讨论3.1键合压力对Al压焊块损伤的影响表2所示为非导电膜和金2金共金工艺中不同键合力情况下的电信号失效测试结果.012半导体学报第26卷图4COF互连结构的有限元分析网格Fig.4MeshforFEAofCOFinterconnectstructure表2样品电性能测试结果Table2Resultofelectricfunctiontest7kgf9kgf11kgf14kgf非导电膜工艺无失效样片无失效样片无失效样片无失效样片金2金共金工艺无失效样片无失效样片无失效样片36%样片失效用光学显微镜分析失效样品发现,样品失效是由于凸点下芯片上Al压焊块的角落位置因应力过大而产生裂缝,如图5所示.比较非导电膜和金2金共金工艺的实验结果可以发现,非导电膜工艺能够比金2金共金工艺承受更大的键合压力.造成这一结果的原因是由于非导电膜工艺中使用了没有导电粒子的薄膜,在键合过程中,这种半固态的胶状物质起到了缓冲的作用.而金2金共金工艺是在键合之后才填充填充料,因此金2金工艺使Al层中的应力情况更为严重.此外,金2金工艺最后键合阶段的温度高于非导电膜工艺100,高温易使Al层损伤,这也是金2金工艺所能承受的压力小于非导电膜工艺的原因.ANSYS模拟加压负载下Al压焊块中的应力分布如图6所示,模拟中只考虑机械应力,未考虑热应力.应力集中位置与实验观察到卸载后的失效部位非常一致,表明键合力过大造成了此区域的细微裂缝.3.2不同接触面积对Al压焊块损伤的影响为了尝试通过改变印制线宽度来避免键合时在图5IC表面Al压焊块中的开裂情况Fig.5CrackonICsurface图6Al压焊块中的等效应力分布Fig.6VonmisesstressdistributionintheAllayerAl压焊块中造成的过大应力集中,进行了不同印制线宽度的挠性基板上所能承受的最大键合力的实验.在键合对准情况相近条件下获得的实验结果如表3所示.表3不同印制线宽度的挠性基板上承受键合力的情况Table3Maximumbondingforcesonfoilsofdifferentcon2ductivetrackwidth印制线上底宽度/m金凸点长度/m总接触面积/mm2键合力状态25.3990.80214.5kgf出现电功能异常16.6990.5259.5kgf没有出现异常112第1期彭瑶玮等:

COF结构中键合力损伤芯片Al层的研究上述实验结果表明,减小印制线宽度,总接触面积减小,但是在相同单位面积键合压力下(18kg/mm2),小印制线宽度的承受力好于大印制线宽度.这说明小印制线的挠性基板在非导电膜或金2金共金工艺中能够减缓所施加的键合力,从而减轻Al压焊块中的最大应力集中.ANSYS对上述情况的模拟结果如图7所示.在小印制线宽度的情况下,由相同键合力引起的Al压焊块中的最大应力都小于较大印制线宽度的情况.考虑到小印制线宽度时的接触面积要小很多,因此在相同单位面积情况下,较大印制线宽度时Al压焊块中应力要比小印制线宽度大很多.图7Al压焊块中的最大等效应力和键合力的关系Fig.7Maximumvonmisesstressinthealuminumpadversusbondingforce3.3不同的键合偏移容差对Al层损伤的影响在实际生产过程中,键合工序中总有偏差,不同的键合机有不同的偏移容差,一般在510m.了解偏移容差对非导电膜和金2金共金工艺中Al压焊块内最大应力的影响,对实际生产中每台机器键合压力参数的调节有指导意义.为了更好地考察偏移容差对不同印制线宽度挠性基板的影响,模拟时印制线宽度的取值为10m和20m,芯片凸点宽度为30m,与实际情况相同.由于印制线长度远大于芯片凸点长度,键合时的前后偏移对结果影响不大,而旋转偏移很少发生,故模拟时仅考虑左右偏移.模拟结果如图8所示,在四种不同的键合压力下,两种印制线宽度的应力随绝对偏移距离的变化趋势各自相同.在同一键合压力情况下,10m和20m印制线宽度的应力随绝对偏移距离的变化情况不同.当偏移距离在25%印制线宽度以内时,Al压焊块内等效应力随绝对偏移距离增大而减少;

当偏移距离在25%50%印制线宽度范围时,应力程度又随绝对偏移距离增大而上升.对20m印制线宽度的挠性基板图8不同键合压力下Al压焊块最大应力和偏移位移的关系(a)7kgf;

(b)9kgf;

(c)11kgf;

(d)14kgfFig.8RelationshipbetweenmaximumvonmisesstressinAlpadandmisalignmentdisplacementundervariousbond2ingforces(a)7kgf;

(d)14kgf来说,偏移距离为5m时,Al层中的最大应力最低,因此选择偏移容差为5m的键合机对20m印制线宽度的挠性基板来说是完全适用的.对10m印212半导体学报第26卷制线宽度的挠性基板来说,5m的偏差将会引起Al层中应力程度剧烈的变化,此时键合机的偏移容差应控制在215m以内.上述结果表明,偏移距离对Al压焊块中最大应力的影响与印制线宽度有关,适当的偏移距离(约25%印制线宽度)可以在一定程度上缓解Al压焊块中的最大应力;

但当偏移距离进一步增加时,应力又迅速上升.4结论通过对非导电膜工艺和金2金共金工艺的实验及模拟研究,可以得到以下结论:

(1)模拟获得的应力集中位置和实验观察到的失效位置一致,表明由于键合过程在Al压焊块中造成的应力集中导致了此位置的开裂.由于非导电膜工艺和金2金共金工艺的步骤和最终键合温度不同,金2金共金工艺在14kgf键合力时就会产生Al层开裂现象,而此时非导电膜工艺没有问题.

(2)在非导电膜或金2金共金工艺中,较小印制线宽度的挠性基板在键合对准情况相近条件下能够适应更大的单位面积键合力.(3)键合机偏移容差对Al压焊块中最大应力的影响与挠性基板上印制线宽度有关,适当的偏移距离(约25%印制线宽度)可以在一定程度上缓解在Al压焊块中的最大应力;

但偏移距离进一步增加时,应力又迅速上升.因此,较宽的印制线宽度对偏移容差要求低,而较小的印制线宽度对键合机偏移容差的要求很高.参考文献1TanCW,ChanYC,YeungNH.Behaviorofanisotropicconductivejointsundermechanicalloading.MicroelectronicsReliability,2003,43:

4812YimM,PaikK.Designandunderstandingofanisotropicconductivefilms(ACFs)forLCDPackaging.IEEETransComponentPackagingTechnol2PartA,1998,21:

2263LiuJ.ACAbondingtechnologyforlowcostelectronicspackagingap2plications2currentstatusandremainingchallenges.Soldering&

Sur2faceMountTechnology,2001,13(3):

394ChiuYW,ChanYC,LuiSM.Studyofshort2curcuitingbetweenad2jacentjointsunderelectricfieldeffectsinfinepitchanisotropiccon2ductiveadhesiveinterconnects.MicroelectronicsReliability,2002,42:

19455ShenGS.LCDdriverICassemblytechnologiesandstatus.IntlSym2posiumonElectrionicMaterialsandPackaging,2002:

3166KimYG,PavulurJK,etal.Thermocompressionbondingeffectsonbump2padadhesion.IEEETransactiononComponents,PackagingandManufacturingTechnology2PartB,1995,18

(1):

1927HuangWeidong,SunZhiguo,CaiXia,etal.Distributionofresidualstressinpackagingassembliesofchiponboard.ChineseJournalofSemiconductors,2003,24(6):

649(inChinese)黄卫东,孙志国,彩霞,等.板上芯片固化后残余应力分布的有限元模拟.半导体学报,2003,24(6):

6498LauJH,PaoYH.SolderjointreliabilityofBGA,CSP,flipchip,andfinepitchSMTassemblies.NewYork:

McGraw2Hill,1997:

1129LauJH,RiceDW,HarkinsCG.Thermalstressanalysisoftapeau2tomatedbondingpackagesandinterconnections.IEEETransactiononComponents,HybridsandManufacturingTechnology,1990,13

(1):

182312第1期彭瑶玮等:

COF结构中键合力损伤芯片Al层的研究DamageofBondingForceonICAluminumPadinCOFStructurePengYaowei1,ChanJusty2,WangZhiping2,andXiaoFei1(1DepartmentofMaterialScience,FudanUniversity,Shanghai200433,China)(2ChinaTechnologyCenter,PhilipsMobileDisplaySystems,Shanghai200131,China)Abstract:

TheimpactofbondingforceonAlpadinICchip,andthemaximumbondingforceareachievedbybothexperimentalandsimulativemethods.Trackwidthandmisalignmentaretwomainfactorsstudied.Theformeraffectsthefoilandinterconnectdesign;

whilethelaterisrelat2edtomanufacturingtolarenceandbondingmachineaccuracy.Itisshownthatthebondingforce,trackwidthandmisalignmenthavegreatinflu2enceonthemaximumstressinthealuminumpadoftheIC.Keywords:

chiponfoil;

non2conductivefilm;

Au2Aueutectic;

finiteelementsimulationEEACC:

0170JArticleID:

025324177(2005)0120209206PengYaoweifemale,wasbornin1978,mastercandidate.Herresearchinterestsmainlyfocusonelectronicpackagingandinterconnecttechnology.Received17December2003,revisedmanuscriptreceived9May2004?

2005ChineseInstituteofElectronics412半导体学报第26卷