计算机组成原理第8章习题指导资料下载.pdf

《计算机组成原理第8章习题指导资料下载.pdf》由会员分享,可在线阅读,更多相关《计算机组成原理第8章习题指导资料下载.pdf(8页珍藏版)》请在冰点文库上搜索。

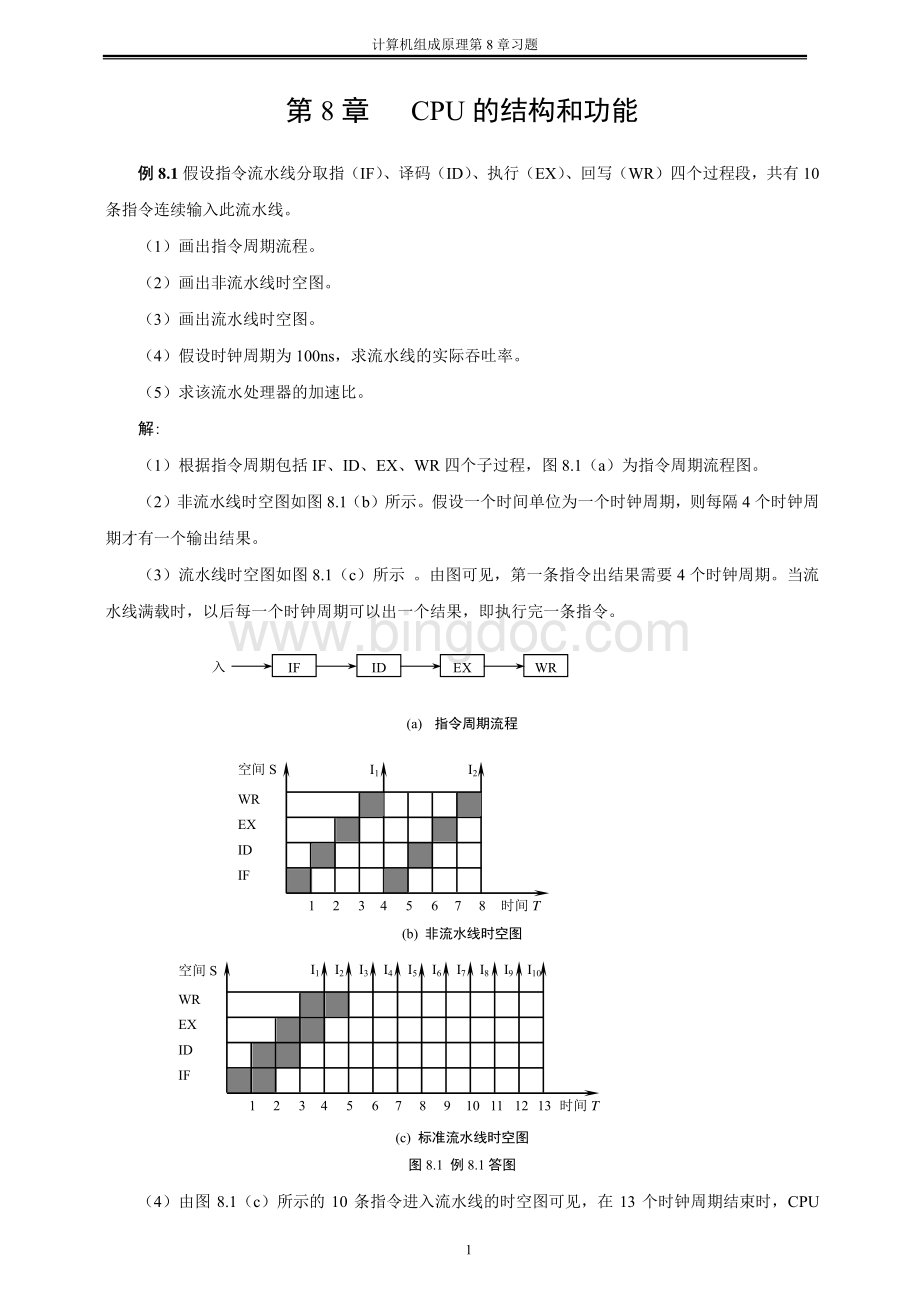

当流水线满载时,以后每一个时钟周期可以出一个结果,即执行完一条指令。

(a)指令周期流程(b)非流水线时空图(c)标准流水线时空图图8.1例8.1答图(4)由图8.1(c)所示的10条指令进入流水线的时空图可见,在13个时钟周期结束时,CPU入IFIDEXWRI6I7I8I9I10I3I2910111213I5I1空间S时间T87654321IFIDEXWRI4I2I1空间S时间T87654321IFIDEXWR计算机组成原理第8章习题2执行完10条指令,故实际吞吐率为:

10/(100ns13)0.77107条指令/秒(5)在流水处理器中,当任务饱满时,指令不断输入流水线,不论是几级流水线,每隔一个时钟周期都输出一个结果。

对于本题四级流水线而言,处理10条指令所需的时钟周期数为T4=4+(101)=13。

而非流水线处理10条指令需410=40个时钟周期。

故该流水处理器的加速比为40133.08例例8.2设某机有四个中断源1、2、3、4,其硬件排队优先次序按1234降序排列,各中断源的服务程序中所对应的屏蔽字如表8.1所示。

表8.1例8.2各中断源对应的屏蔽字中断源屏蔽字123411101201003111140101

(1)给出上述四个中断源的中断处理次序。

(2)若四个中断源同时有中断请求,画出CPU执行程序的轨迹。

(1)根据表8.1,四个中断源的处理次序是3142。

(2)当四个中断源同时有中断请求时,由于硬件排队的优先次序是1234,故CPU先响应1的请求,执行1的服务程序。

由于在该服务程序中设置了屏蔽字1101,故开中断指令后转去执行3服务程序,且3服务程序执行结束后又回到1服务程序。

1服务程序结束后,CPU还有2、4两个中断源请求未响应。

由于2的响应优先级高于4,故CPU先响应2的请求,执行2服务程序。

在2服务程序中由于设置了屏蔽字0100,意味着1、3、4可中断2服务程序。

而1,3的请求已处理结束,因此在开中断指令之后转去执行4服务程序,4服务程序执行结束后又回到2服务程序的断点处,继续执行2服务程序,直至该程序执行结束。

图8.2示意了CPU执行程序的轨迹。

图8.2例8.2CPU执行程序的轨迹例例8.3假设主机框图如图8.3所示,各部分之间的连线表示数据通路,箭头表示信息传送方向。

(1)标明图中X、Y、Z、W四个寄存器的名称。

(2)简述取指令的数据通路。

(3)简述取数指令和存数指令执行阶段的数据通路。

程序4程序3程序2程序1t1、2、3、4同时请求中断服务程序计算机组成原理第8章习题3图8.3例8.3主机框图解:

(1)图中X为存储器数据寄存器MDR,Y为存储器地址寄存器MAR,Z为指令寄存器IR,W为程序计数器PC。

(2)取指令的数据通路是:

WYMXZ。

(3)取数指令是将指令地址码字段指出的存储单元的内容读到AC中。

由于图中X(MDR)与AC无直接通路,要经过ALU实现数据传送,故执行阶段的数据通路是:

X(或Z)YMXALUAC。

存数指令是将AC的内容存入指令地址码字段指出的存储单元中,其执行阶段的数据通路是先置地址X(或Z)YM,然后ACXM。

例例8.4设CPU内有下列部件:

PC、IR、SP、AC、MAR、MDR和CU,要求:

(1)写出完成间接寻址的取数指令LDAX(将主存某单元的内容取至AC中)的信息流。

(2)画出中断周期的信息流,并简要说明。

解:

(1)完成间接寻址的取数指令包括取指、间址和执行三个阶段。

取指阶段的信息流PCMAR地址线CU发出读存储器命令M数据线MDRIR至此指令读至IROP(IR)CU指令操作码送CU分析(PC)+1PC形成下一条指令地址间址阶段的信息流MDR(或IR)的地址码字段MAR地址线CU发出读存储器命令CPU+1主存储器MXYZW状态寄存器ALUACCU+1计算机组成原理第8章习题4M数据线MDR至此有效地址读至MDR执行阶段的信息流MDRMAR地址线CU发出读存储器命令M数据线MDRAC至此数据读至AC中

(2)中断周期的信息流在中断周期内需将程序断点(在PC中)保存起来,通常把断点存入堆栈。

假设进栈操作是先修改堆栈指针,后存入数据,则中断周期的信息流如图8.4所示。

具体可描述为:

CU控制(SP)1SPMAR地址线CU发出写存储器命令PCMDR数据线存储器CU将向量地址(硬件向量法)或中断识别程序入口地址(软件查询法)PCMDRCUMARCPUPC存储器数据总线控制总线地址总线图8.4例8.4中断周期信息流例例8.5流水线中有三类数据相关冲突:

写后读相关(ReadAfterWrite,RAW),读后写相关(WriteAfterRead,WAR),写后写相关(WriteAfterWrite,WAW)。

判断下面三组指令各存在哪种类型的数据相关。

(1)I1SUBR1,R2,R3;

(R2)(R3)R1I2ADDR4,R5,R1;

(R5)+(R1)R4

(2)I3STAM,R2;

(R2)M,M为存储单元I4ADDR2,R4,R5;

(R4)+(R5)R2(3)I5MULR3,R2,R1;

(R2)(R1)R3I6SUBR3,R4,R5;

(R4)(R5)R3解:

在第

(1)组指令中,I1指令运算结果应先写入R1,然后在I2指令中读出R1内容。

由于I2指令进入流水线,使得I2指令在I1指令写入R1前就读出R1的内容,发生RAW相关。

在第

(2)组指令中,I3指令应先读出R2内容并存入存储器单元M中,然后I4指令中将运算结果计算机组成原理第8章习题5写入R2中。

但由于I4指令进入流水线,使得I4指令在I3指令读出R2之前就写入R2,发生WAR相关。

在第(3)组指令中,如果I6指令减法运算完成时间早于I5指令的乘法运算时间,使得I6指令在I5指令写入R3之前就写入R3,导致R3内容错误,发生WAW相关。

例例8.6假设指令流水线分取指令(IF),指令译码/读寄存器(ID),执行/有效地址计算(EX),存储器访问(MEM),结果寄存器写回(WB)五个过程段。

现有下列指令序列进入该流水线。

ADDR1,R2,R3;

(R2)+(R3)R1SUBR4,R1,R5;

(R1)(R5)R4ANDR6,R1,R7;

(R1)AND(R7)R6ORR8,R1,R9;

(R1)OR(R9)R8XORR10,R1,R11;

(R1)XOR(R11)R10试问:

(1)如果处理器不对指令之间的数据相关进行特殊处理,而允许这些指令进入流水线,试问上述指令中哪些指令将从未准备好数据的R1寄存器中取到错误的操作数?

(2)假如采用将相关指令延迟到所需操作数被写回到寄存器后再执行的方式,以解决数据相关的问题,那么处理器执行该指令序列需占多少个时钟周期?

(1)由上述指令序列可见,ADD指令后的所有指令都用到ADD指令的计算结果。

表8.2(a)列出了未采用特殊处理的流水线示意,表中ADD指令在WB段才将计算结果写入寄存器R1中,但SUB指令在其ID段就要从寄存器R1中读取该计算结果。

同样AND指令、OR指令也将受到这种相关关系的影响。

ADD指令只有到第五个时钟周期末尾才能结束对寄存器R1的写操作,使XOR指令可以正常操作,因为它在第六个时钟周期才读寄存器R1的内容。

表8.2(a)未对数据相关进行特殊处理的流水线时钟周期123456789ADDIFIDEXMEMWBSUBIFIDEXMEMWBANDIFIDEXMEMWBORIFIDEXMEMWBXORIFIDEXMEMWB

(2)表8.2(b)列出了对这些指令之间数据相关进行特殊处理的流水示意。

由此表可见,从第一条指令进入流水线到最后一条指令出结果,共需12个时钟周期。

计算机组成原理第8章习题6表8.2(b)对数据相关进行特殊处理的流水线时钟周期123456789101112ADDIFIDEXMEMWBSUBIFIDEXMEMWBANDIFIDEXMEMWBORIFIDEXMEMWBXORIFIDEXMEMWB例例8.7回答下列问题:

(1)一个完整的指令周期包括哪些CPU工作周期?

(2)中断周期前和中断周期后各是CPU的什么工作周期?

(3)DMA周期前和DMA周期后各是CPU的什么工作周期?

(1)一个完整的指令周期包括取指周期、间址周期、执行周期和中断周期。

其中取指和执行周期是每条指令都有的。

间址周期只有间接寻址(存储器间接寻址)的指令才有。

中断周期只有在条件满足时才有。

(2)中断周期前是执行周期,中断周期后是取指周期。

(3)DMA周期前可以是取指周期、执行(取数和存数)周期或中断周期,DMA周期后也可以是取指周期、执行(取数或存数)周期或中断周期。

总之,DMA周期前后都是存取周期。

例例8.8判断下列叙述是否正确,并对有错的句子加以修改。

(1)一个更高级的中断请求一定可以中断另一个正在执行的中断处理程序。

(2)所谓关中断就是屏蔽所有的中断源。

(3)一旦有中断请求出现,CPU立即停止当前指令的执行,转去执行中断服务程序。

(4)为了保证中断服务程序执行后能正确返回到被中断的程序断点处继续执行程序,必须进行现场保护。

(5)中断级别最高的是不可屏蔽中断。

(6)CPU响应中断后,由用户通过关中断指令置“0”允许中断触发器。

(7)在多重中断系统中,CPU响应中断后可以立即响应更高优先级的中断请求。

(8)CPU响应中断时暂停当前程序的运行,自动转去执行中断服务程序。

上述句子中,(4)、(8)正确,其余有错,修改如下:

(1)如果CPU处于关中断状态(允许中断触发器EINT=0),或者更高级的中断源被屏蔽,则优先级高的中断源就不能中断另一个正在执行的中断处理程序。

(2)关中断是指允许中断触发器EINT=0,CPU不允许响应任何中断,这和屏蔽中断源是两个概念。

(3)一旦有中断请求出现,CPU必须执行完当前指令后才能转去受理中断请求(如果允许中断触发器为“1”)。

(5)级别最高的中断不一定是不可屏蔽中断,这与机器的设计有关。

例如8086/8088中,内部中计算机组成原理第8章习题7断的优先级比不可屏蔽中断的级别更高。

(6)CPU响应中断后,不是由用户通过关中断指令置“0”允许中断触发器的,而是由硬件(中断隐指令)自动完成的。

(7)在多重中断系统中,CPU响应中断后,在保护断点和现场以及开中断之前,CPU不能立即响应更高优先级的中断请求。

例例8.9设某机有四个中断源A、B、C、D,其硬件排队优先次序为ABCD,现要求将中断处理次序改为DACB。

(1)写出每个中断源对应的屏蔽字。

(2)按图8.5时间轴给出的四个中断源的请求时刻,画出CPU执行程序的轨迹。

设每个中断源的中断服务程序时间均为20s。

图8.5例8.9设置中断请求的时刻解:

(1)在中断处理次序改为DACB后,每个中断源新的屏蔽字如表8.3所示。

表8.3例8.9各中断源对应的屏蔽字中断源屏蔽字ABCDA1110B0100C0110D1111

(2)根据新的处理次序,CPU执行程序的轨迹如图8.6所示。

图8.6例8.9

(2)答图例例8.10设某机有六个中断源,优先顺序按012345降序排列。

(1)若在某用户程序的运行过程中,依次发生了3、2、1级中断请求,画出CPU的程序运行轨迹。

A程序B程序C程序D程序4050607080903020510t/s程序BDACBDAC405060708090302051510t/s程序计算机组成原理第8章习题8

(2)若在3、2、1级中断请求发生之前,用改变屏蔽字的方法,将优先级的顺序从高到低改为053412。

试在与

(1)相同的请求顺序和请求时间的情况下,画出CPU程序的运行轨迹。

(1)依次发生3、2、1级中断请求的CPU程序运行轨迹示意如图8.7所示。

图8.7例8.10

(1)答图

(2)改变了优先处理顺序后,在与

(1)相同的请求顺序和请求时间的情况下,若3程序较长,2、1提出请求均在3程序的执行时间内,则CPU程序的运行轨迹示意如图8.8(a)所示。

图8.8(a)例8.10

(2)情况1答图若3程序较短,2的请求发生在3程序的执行时间内,1的请求发生在3程序执行结束后,则CPU程序的运行轨迹示意如图8.8(b)所示。

图8.8(b)例8.10

(2)情况2答图程序用户程序3程序2程序1程序t321程序用户程序3程序2程序1程序t321程序用户程序3程序2程序1程序t321