Altera杯 第四届全国研究生电子设计竞赛.docx

《Altera杯 第四届全国研究生电子设计竞赛.docx》由会员分享,可在线阅读,更多相关《Altera杯 第四届全国研究生电子设计竞赛.docx(15页珍藏版)》请在冰点文库上搜索。

Altera杯第四届全国研究生电子设计竞赛

第四届全国研究生电子设计竞賽笔试题2002.8.18

第1类题:

(15分)

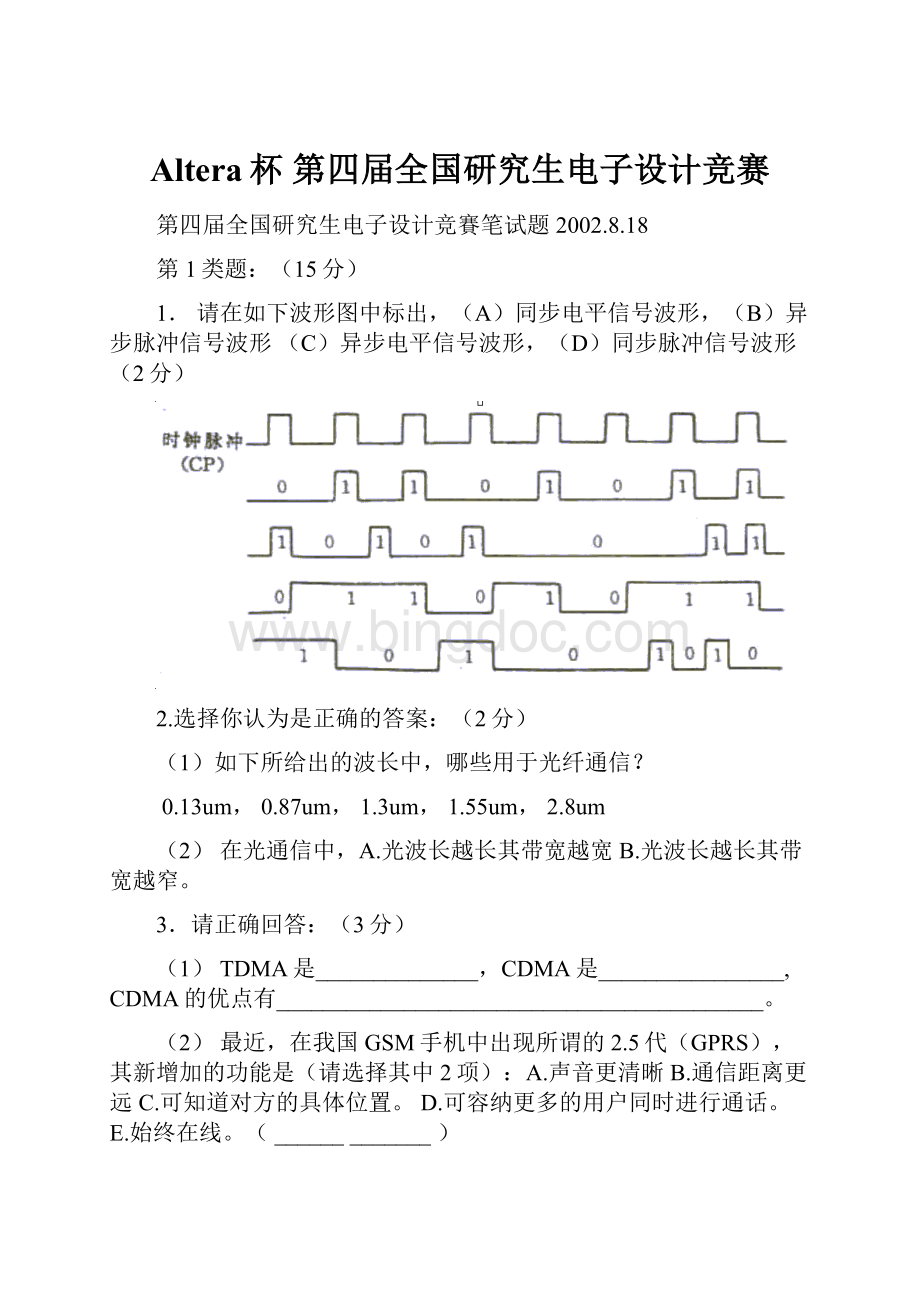

1.请在如下波形图中标出,(A)同步电平信号波形,(B)异步脉冲信号波形(C)异步电平信号波形,(D)同步脉冲信号波形(2分)

2.选择你认为是正确的答案:

(2分)

(1)如下所给出的波长中,哪些用于光纤通信?

0.13um,0.87um,1.3um,1.55um,2.8um

(2)在光通信中,A.光波长越长其带宽越宽B.光波长越长其带宽越窄。

3.请正确回答:

(3分)

(1)TDMA是______________,CDMA是________________,CDMA的优点有__________________________________________。

(2)最近,在我国GSM手机中出现所谓的2.5代(GPRS),其新增加的功能是(请选择其中2项):

A.声音更清晰B.通信距离更远C.可知道对方的具体位置。

D.可容纳更多的用户同时进行通话。

E.始终在线。

(_____________)

(3)未来的无线个人通信的目标是:

在任何______,任何_______,和任何______实现通信。

4.请给出如下缩写术语的英文原文和中文对应词组:

(6分)

SOC

IPREUSE

SDH

ADSL

ISDN

DSP

RTOS

VHDL

CPLD

USB

JTAG

FPGA

MEMS

MCU

MPEG

P2P

XML

UDDI

EDA

VLSI

5.因特网是大家很熟悉的。

由于它的迅速普及和大量使用,再加上新的应用技术的不断涌现,人们发现,它原来的一些协议及规则,使它将面临严重的问题和挑战。

你能说出其中最主要的问题是什么吗?

(提示:

可从IPV6和IPV4中知道)(请选择其中三项最主要的问题):

(______________)(2分)

(A)传送速度不能大幅度提高;(B)要花很长时间才能找到你要联接的网页;(C)允许的IP地址资源太少;(D)声音音质不佳;(E)病毒肆虐;(F)语音延迟;(G)干扰很大;(H)图象失真;(K)保密性丧失。

第2类题:

(8分)

1.下图所示为P阱硅柵CMOS反相器的剖面图,试给出该硅柵CMOS反相器的基本工艺流程(可根据所需光刻版给出流程)。

(3分)

2.请选择正确答案:

(1分)

a)制版和光刻这两种工艺在集成电路制造中十分重要。

我们知道,版分为阳版(正版)和阴版(负版)。

所谓阳版,其透明部分(对应嚗光部分)的图形,将会在光刻后被:

(A)除去;(B)保留。

b)刻工艺中用的胶,有正胶和负胶之分,所谓正胶,其嚗光部分的图形,将会在光刻后被:

(A)除去;(B)保留。

3.假定铝的方块电阻为0.05Ω/□,多晶硅为30Ω/□。

如果线宽为4μm,线长为5μm,用这两种材料构成的导线的电阻各为多少?

随着集成电路工艺的发展,线条的宽度也在缩小。

如果线宽缩为0.5μm,线长不变,试再次计算它们的电阻各为多少?

(注:

不计线端头引出区的电阻值)(4分)

第3类题:

(12分)

1.电路的版图如下图所示:

引出端8是地线,14为电源(Vcc),9为输出端,而1,2,3,4,5都是输入端。

Q为晶体管,R为电阻。

请画出它的对应电路图,并标出与其版图相对应的符号。

并说出它是什么功能的电路。

(8分)

2.在深亚微米工艺中,有两条线相邻且相互靠得比较近。

我们知道,在这种情况中下会发生信号串扰现象。

假定这两条线的其中一条传送的是射频信号,且线的宽度为0.3μm,线间距也为0.3μm,而铝线的厚度为0.5μm。

请问其串扰的主要途径是:

(A)分布电感;(B)线间分布电阻;(C)线间分布电容;(D)电磁辐射。

请选择其中的2项。

(1分)

(___________)

3.集成电路的后端设计中,经常听到人们说DRC,ERC和LVS。

请选择你认为是正确的答案填入相应的空白处:

(3分)

DRC是__________;ERC是__________;LVS是_________。

(A)电路检查;(B)短路检查;(C)开路检查;(D)几何图形检查;(E)电学规则检查;(F)电路设计规则检查;(G)版图设计规则检查;(I)电路连接检查;(J)版图和与其所连电路的正确性检查;(K)通孔检查;(L)电源和地线检查。

第4类题:

(20分)

1、分别指出如下的VHDL描述是否可综合?

说明理由。

(4分)

(1)architecturebeh2ofmux2is

begin

withsel_0select

q<=aafter10nswhen‘0’;

bafter10nswhenothers;

endbeh2;

(2)process(a,b)

begin

c1<=nota;

c2<=aandb;

endprocess;

(3)process

begin

waitona;

C<=nota;

endprocess;

(4)process(clk)begin

if(clk’eventandclk=‘1’)then

q<=d;

else

q<=a;

endif

endprocess;

2、如下图所示电路,试采用流水线技术使其时钟频率提高3倍,请画出改进后的电路示意图,并讨论其系统时钟频率提高的原理及指出其所付出的代价。

(5分)

3.集成电路电路设计方法学中的自顶向下的设计方式的主要流程是:

_____________________________________________________

其中主要验证步骤有:

_____________________________________(2分)

(a)、在每个步骤中,常有哪几种验证方式可供选择,试比较其优缺点。

(2分)

(b)、何谓形式验证,试解释之。

(2分)

4.请分别画出如下VHDL程序所描述的一个电路模型。

(5分)

(1)

(2)

Process(CLK)Process()

BeginVariableX,Y:

std_logic;

If(CLK’eventandCLK=’1’)thenBegin

X<=AandB;If(CLK’eventandCLK=’1’)then

Y<=X;X:

=AandB;

Z<=Y;Y:

=X;

Endif;Z<=Y;

EndProcess;Endif;

EndProcess;

(3)(4)

Process(CLK)Process(CLK)

BeginVariableX,Y:

std_logic;

If(CLK’eventandCLK=’1’)thenBegin

Z<=Y;If(CLK’eventandCLK=’1’)thenY<=X;Z<=Y;

X<=AandB;Y:

=X;

Endif;X:

=AandB;

EndProcess;Endif;

EndProcess;

(5)entitybitlinkis

port(A,B:

instd_logic_vector(3downto0);

EN:

std_logic;

Y:

outstd_logic_vector(7downto0);

Endbitlink;

Architecturedataofbitlinkis

Signaltmp:

std_logic_vector(3downto0);

Begin

tmp<=Band(EN&EN&EN&EN);

Y<=A&tmp;

Enddata;

第5类题:

(30分)

1、采用SR锁存器可实现时钟信号的双相化,其如图所示,请画出其对应输入的输出波形,并指出其特征。

(4分)

2、在状态机的电路设计中,“ONE-HOT”状态编码是指_____________________;

假定状态向量的定义如下:

typestate_typeis(s0,s1,s2,s3,s4)

signalstate:

state_type

如采用(one-hot)编码,需用_______个触发器?

为什么这种编码方式较适用于FPGA应用设计?

(4分)

3、如下图(a)所示为用时钟同步输出信号Mealy型状态机的状态图。

图(b)为该状态机的电路框图。

试用VHDL描述之。

并讨论,为何这种状态机可以实现输出信号的“无毛刺”。

(7分)

4.设计一个同步电路,该电路输出IS=X1/3,EN为使能端,Done指示运算结束。

输入X的范围是0—255;其中X=0—64出现的概率较大,精度要求1‰,其它数值精度要求1%,自行决定IS的位数。

(15分)

EN

(1)给出设计方案(算法思路,精度保证的方案)。

(2)采用HDL进行设计描述。

(本题可另纸书写)

第6类题:

(15分)

1.在深亚微米集成电路技术成熟的条件下,有人说“FPGA将会全面取代ASIC”,有人说“不可能,两回事”。

还有人说“两者的技术特性将融合,ASIC中将有FPGA构造,FPGA中将有ASIC功能模块”。

试以技术专家的角度,阐述你的观点。

(5分)

2.集成电路自出现以来,发展速度极快,现在其规模已达到超大规模,甚至到系统级(SOC);最细的光刻线条也由微米达到亚微米,甚至达到深亚微米量级。

但是,当我们观察集成电路片上的晶体管时,会发现它们都是在同一层面上排列(平铺)的,这就好象人们居住在“平房”中一样。

最近,有人宣称要制造三维多层立体集成电路,这就相当于从“平房”过渡到“楼房”,这无疑将使集成电路的集成度大幅提高,其意义是深远的,将会使集成电路技术推向一个新的发展阶段。

请简单说明其所需的关键技术是什么,并且想象一下建造“楼房”将会遇到的最严峻技术挑战会是什么,并设想如何解决它。

(5分)

4.在SOC设计中,系统的低功耗设计是设计者和用户关心的主要问题。

请从系统和电路设计的角度,讨论如何降低芯片的功耗。

(5分)

准考证号:

_____________________

EDA“鹏城杯”第四届全国研究生电子设计竞赛(上机试题)

试题一(60分)

设一帧为500us。

有数据流A和B。

A一帧为144Bytes,B一帧为140Bytes。

B数据流按照(图一)中所示的方式映射到数据流A中:

(图一)

映射要求为:

将B数据流顺序映射到A数据流中除去C、D、E、F四个标识字节之后的字节中。

但是,B数据流的第一个字节G在A数据流中的位置由C、D两个标识字节指示,E、F两个标识字节无用。

C、D标识字节内容定义如(图二)所示:

(图二)

1、当H1H2H3H4有效时;

I1J1I2J2I3J3I4J4(I1为最高位)指示出B数据流的第一个字节G在A数据流中的映射位置La。

其中,A数据流一帧的编号如(图一)所示,D标识字节后的第一个字节定义为起始位置0,E后为35,F后为71,C后为105。

H1H2H3H4有效是指H1H2H3H4为1001。

为了容错,采用多数判决准则,H1H2H3H4四比特中的任意三比特满足即可。

I1J1I2J2I3J3I4J4应当在0~139范围之内。

2、当H1H2H3H4无效时;

(a)与上一帧相比,I1I2I3I4任意四位翻转时,La加一,若La已经为139,La加一后的结果为0。

(b)与上一帧相比,J1J2J3J4任意四位翻转时,La减一,若La已经为0,La减一后的结果为139。

(c)当条件(a)、(b)同时满足时,(a)有效,(b)无效。

(d)当条件(a)、(b)都不满足时,La值不变。

H1H2H3H4无效是指H1H2H3H4为0110。

为了容错,采用多数判决准则,H1H2H3H4四比特中的任意三比特满足即可。

I1J1I2J2I3J3I4J4应当在0~139范围之内。

3、通过告警H指示当前所收到的H1H2H3H4值是否为1、2中所定义的H1H2H3H4值,如果成立告警H输出0,否则告警H输出1。

4、通过告警L指示当前所收到的I1J1I2J2I3J3I4J4是否在0~139范围之内,如果成立告警L输出0,否则告警L输出1。

5、K1K2两个比特无用。

已知八位并行数据流A,系统时钟为288K/Sclock,帧同步时钟为2K/SFrame,求出B数据流中第一个字节G映射在A中的位置,并且正确输出告警H和告警L。

时序关系如(图三)所示:

(图三)

(图四)

(1)当Frame为高时,第一个Clock下降沿表示A一帧的开始。

(2)每个Clock上升沿数据A有效。

(3)当G字节映射在0~104范围内时,则在接收到G字节后输出当前帧的G字节,如(图三)所示。

(4)当G字节映射在105~139范围内时,则在接收到D字节后的一个时钟Cycle输出当前帧的G字节,如(图四)所示。

(5)告警L在接收到C字节后产生,告警H需要保持到接收到下一帧的C字节。

(6)告警H在接收到D字节后即时产生,告警H需要保持到接收到下一帧的D字节。

注:

以上所出现的数字500、144、140、105、139、35、36、70、71、104、288、2都为十进制;1001、0110为二进制。

试题二(40分)

Barrelshifter设计

在现代高速RISC微处器里,为了实现在单时钟周期内各种高速的移位操作,都普遍采用Barrelshifter来实现,Barrelshifter已经成为其中一个重要组成部分,barrelshifter设计的最终面积与速度,直接影响着整个RISC系统的性能。

实际上的barrelshifter的设计方法有两种,一种是把结构手工在晶体管级电路上布线实现,这样设计可以做到速度和面积上的最优化,但比较复杂,难度也很大,另一种是在门级电路上实现,这样的设计易于理解,但速度稍逊,以下题目,要求用HDL语言实现两种结构以上的可综合的桶形移位器(barrelshifter),综合成为门级电路,并在FPGA内实行,要求如下:

系统要求:

桶形移位器从物理结构上分为多种,要求在指定的时间内完成两种以上的桶形移位器,并附相应的各类型结构的示意图形以及文字描述,文字描述包括:

在移位过程中,补零/补符号位如何操作,循环移位时的政策。

输入输出区域划分。

功能要求:

实现的功能有:

逻辑左移,逻辑右移,算术左移,算术右移,循环左移,循环右移,内部不允许有时钟控制

信号要求:

a,要求HDL语言描述要能体现桶形移位器的逻辑电路结构。

b,不允许调用有关shifter的库单元或者内核

c,桶形移位器的数据输入(data_in)和输出(data_out)位宽为32位(bit)。

模块信号名如下:

(统一信号名,方便最后检查结果)

modulebarrel_shifter(

data_in,//32bits,theinputdataforbarrelshift

data_out,//32bits,theresultoftheshiftoperation

shift_number,//5bits,theshiftnumberof

//shiftoperation7<//xistheshiftnumber

shift_dir,//1bit,shiftdirection,0forleft

//shiftoperation,

//1forrightshiftoperation

rotaion_shift,//1bit,rotationshiftoperation

algebra_shift,//1bit,algebrashiftoperation

logic_shift//1bit,logicshiftoperation

);

注:

在同一时间内,逻辑位移,算术位移,循环位移三种情况只有一种能发生,不会有两种,或者两种以上的情况都同时发生。

综合与布线要求:

a,将设计文件综合并布线成为FPGA可下载电路文件,要求指出优化目标(optimizationgoal),优化效果(optimizationeffort),目标时钟频率,要求所做的设计都采用同一综合布线环境

使用的FPGA型号

优化目标

优化效果

目标时钟

频率

b,并根据postplace&routestatictimingreport的结果,以及占用的FPGA的资源,简单分析这各种结构在timing上以及面积上的优劣:

文件名

设计类型

最大组合

路径延时

最大网络

延时

等效门数

结构注释

并生成各种结构的postplace&routesimulationmodel