ED3CH008 GENESIS作业流程.docx

《ED3CH008 GENESIS作业流程.docx》由会员分享,可在线阅读,更多相关《ED3CH008 GENESIS作业流程.docx(38页珍藏版)》请在冰点文库上搜索。

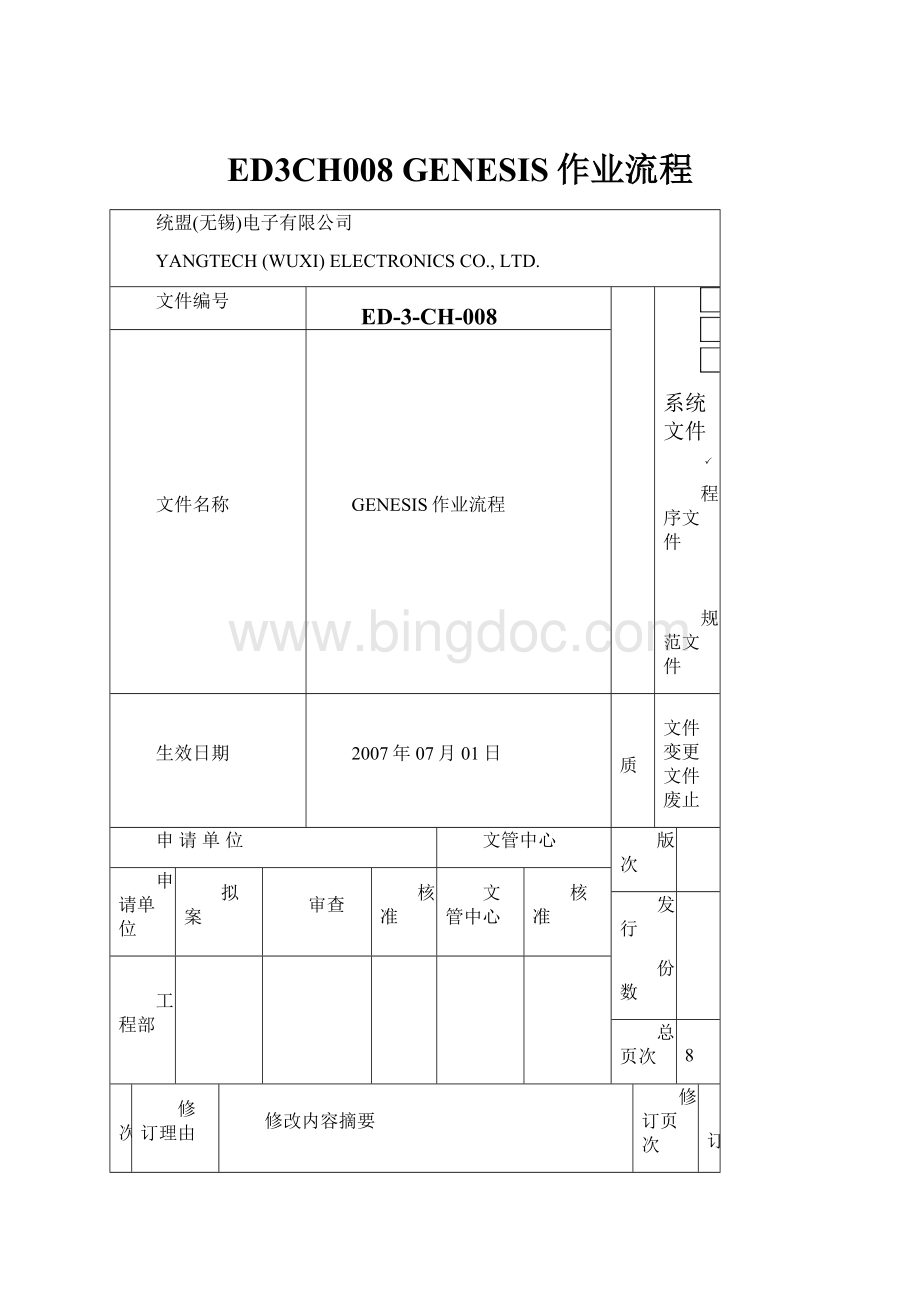

ED3CH008GENESIS作业流程

统盟(无锡)电子有限公司

YANGTECH(WUXI)ELECTRONICSCO.,LTD.

文件编号

ED-3-CH-008

文

件

类

别

系统文件

程序文件

规范文件

文件名称

GENESIS作业流程

生效日期

2007年07月01日

性质

文件变更文件废止

申请单位

文管中心

版次

A

申请单位

拟案

审查

核准

文管中心

核准

发行

份数

1

工程部

总页次

18

版次

修订理由

修改内容摘要

修订页次

修订日期

文件适用单位

发行管制章

单

位

总经理室

制造部

工程部

品保部

业务部

管理部

资材部

资讯部

财务部

关务部

1

如未盖蓝色资料室发文章即为非管制文件或参考用,不作更新之服务

统盟(无锡)电子有限公司

GENESIS作业流程

版本编号

ED-3-CH-008

版次

A

修定日期

2007年07月01日

页次

第1页,共18页

1.目的:

将客户传来的资料,经由GENESIS软件处理排版,做出适合生产线的底片,以确保生产线顺利生产及产出。

2.通用范围:

举凡客户所交付的GERBERFILE、ECN、钻孔程序、以及外包商资料及底片。

3.用语定义:

Dri-钻孔程序

L2~L7-内层底片(4层板-L2.L36层板-L2.L3.L4.L5…..以此类推。

)

COMPSOLD-外层底片(COMP->GOP层,COLD-DOTTOM层)

CMSM-防焊底片(COMP->GOP层,COLD-DOTTOM层)

CLSL-文字底片(CL->GOP层,SL-DOTTOM层)

M1-外钻程序

钻孔程序..扩展名K1-钻孔表

T1-靶孔程序

P1-内钻程序

CDOTSDOT-印刷用塞孔底片.

CSOLT1-喷涂用塞孔底片

.BGT-GENESIS的档案格式。

档案格式.RAR-压缩档

.DXF-图片文件

4.权责:

本操作规范由工程部课级主管审核,经部级主管核准后发行。

如未盖蓝色资料室发文章即为非管制文件或参考用,不作更新之服务

统盟(无锡)电子有限公司

GENESIS作业流程

版本编号

ED-3-CH-008

版次

A

修定日期

2007年07月01日

页次

第2页,共18页

5.流程图:

负责单位

作业流程

使用表单

制程制前课

无

如未盖蓝色资料室发文章即为非管制文件或参考用,不作更新之服务

统盟(无锡)电子有限公司

GENESIS作业流程

版本编号

ED-3-CH-008

版次

A

修定日期

2007年07月01日

页次

第3页,共18页

6.内容

6-1设置层别属性(SetMatrixandLayermerge)

6-1-1将pcb归原点,因为在转入转出不同作业环境时可能原点坐标偏移

a.将所有层次设为影响层(工作层按鼠标右键选AffectedAll)

b.S+C开锁点

c.Ctrl+X搬移对象,点选起点坐标,再于字段键入终点坐标0,0

d.关影响层(工作层按鼠标右键选Affectednone)

6-1-2进入Matrix修改层名后,执行Action>Re-arrangerow定义层次,让计算机能辨识分析

6-1-3把此pcb另copy一名为org之step做为备份

6-1-4确认pcb尺寸,因为先前经过公英制的换算,尺寸可能会有误差,我们可以直接新增nt层做出正确尺寸的成型线(12mil),原来各层的成型线都不用变动,之后若需要放大成型线或套成型线负片都只使用nt层的即可

6-1-5以成型线产生Profile来清除pcb成型线外不需要的对象

a.选取nt层里的成型框

b.选Edit>Creat>Profile自动产生出围绕成型框的Profile(若是遇到成型框较复杂时

c.可能无法自动产生,可利用Step>Profile>Rectangle指令,在坐标区输入成型框左下角与右上角两点的坐标,即可产生矩形的profile)

d.将所有层次设为affectedlayer(若有机构图层,该层可不勾选予以保留)

e.在层别显示处按鼠标右键,选择Cliparea>

Method:

profile

Cliparea:

outside

margin:

60mil

6-1-6定datumpoint,做为ary排版时的基准点

a.选择Step>DatumPoint

b.在坐标区输入pcb左下坐标(以space键区隔xy),通常为(0,0)

如未盖蓝色资料室发文章即为非管制文件或参考用,不作更新之服务

统盟(无锡)电子有限公司

GENESIS作业流程

版本编号

ED-3-CH-008

版次

A

修定日期

2007年07月01日

页次

第4页,共18页

6-2制作钻孔层

6-2-1如果客户本身有提供钻孔层(如果客户没有提供钻孔层,请参考下页的资料)

利用drilltoolsmanager,在drillsize字段输入钻孔孔径(此时输入的钻孔孔径要进位成整数,pth四舍五入,npth二以上进位,这么做是为了取接近的整数大小方便计算机作业,而现场人员会依据工单上正确的孔径作业),并设定其钻孔属性(via、pth、npth让计算机在分析时可以判读)

6-2-2设定孔径size与属性时,遇到相同成品孔径却不同属性时

e.先把size、属性都设成相同(原则上都设成pth,因为之后挑出npth有彩图可参考)执行apply套用到gerber之后,参考彩图去找出原本应是npth的pad

f.利用edit>reshape>changesymbol换回npth正确的size

g.利用edit>attributes来更正钻孔属性

h.按drilltoolsmanager里的updatetable把d上的size与属性套用到字段中

6-2-3如果客户没有提供钻孔层,自行利用替换功能substitute把map的符号换成钻孔pad

i.先把map另copy一层为d。

(Edit>copy>otherlayer)

j.开启edit>reshape>substitute

k.选取一个map符号,在symbol的字段输入要换的size

l.点一下datum前的图形会自动产生坐标,也可在坐标输入栏内自行输入

m.利用edit>attributes来修改钻孔属性

6-2-4相同成品孔径不同属性的处理方式同上页2.1的作法

做出slot孔(但是slot孔中的导引孔先不用做出来,不然之后在执行去除重复孔的时后会被delete掉)

n.DFM>RedundancyCleanup>NFPRemoval(ERF中选择removeduplicatepads),去除重复孔

o.Analysis>Board-drillchecks,可检验出是否有via孔间的距离不足6mil,若不足的要请op降孔径,如果连原稿也不足则要询问客户(via孔边到via孔边至少6mil以上,避免第二钻因板面不平,造成下钻时角度倾斜而断针);双连孔的问题也会标示,有可能是没对位的重复孔,要再处理

p.补上先前没有做的slot孔的导引孔

6-2-5将copynpth孔到nt层(包含成型线与npth孔),方便后续作业.

如未盖蓝色资料室发文章即为非管制文件或参考用不作更新之服务

统盟(无锡)电子有限公司

GENESIS作业流程

版本编号

ED-3-CH-008

版次

A

修定日期

2007年07月01日

页次

第5页,共18页

6-3内层(GND&VCC)

6-3-1制作前若发现有正负片分层,需要先分开正负片

q.在该层按鼠标右键,选择unmerge,把正负片分层

r.将产生的每一层都设成影响层,执行Edit>Reshape>linetopad(把线画成的点转成pad,因为执行contourize消负片功能前需使用过滤器把pad先搬到别层,否则pad会被转成surface)

s.将所有pad及线路先整理到同一层,并执行DFM>RedundancyCleanup>NFPRemoval去除重复孔,工作层要放对

t.把铜箔区块的正负片一层一层套完,每套一层负片就要执行一次contourize

u.最后将pad及线路与铜箔放到同一层即可

6-3-2所有对象全面缩1mil(主要是因为隔离线会有过咬蚀的情况,所以先缩小),缩小后隔离线6mil以下的加回1mil.

6-3-3放大成型线

铜箔区一般内缩20mil,避免成型时伤害洗刀或是成品铜箔外露,所以copy加大成为40mil(相当于单边20mil)的正片的成型框到内层.

v.选copy>otherlayer.

w.layername选nt;invert(正负属性反转)选NO;resizeby(加减大小)键入28.

x.若是有金手指,有金手指相临的成型线内缩深度为斜边深度+20mil,就要加大成为(斜边深度+20mil)*2.

6-3-4换thermal为标准格式ths(开口10mil,宽度至少6mil,孔到内缘要6.5mil)或是依客户要求去除thermal

y.先删除小于dri的thermal

zz.遇到方形thermal不用换格式,通常只要加大1mil即可让宽度符合6.5mil

aa.用过滤器选取所有thermal,用Edit>Reshape>Break打散成为surface

bb.用过滤器关线、pad选取刚刚打散的surface,用Edit>Reshape>fill转成线

cc.Ctrl+w把图形转换为线的显示状态,使用Edit>Reshape>Substitute把线段的thermal替换回标准的symbol,只要注意开口是否有10mil,可以不管其它规格,等计算机涨ring时自动处理

6-3-5涨ring

如未盖蓝色资料室发文章即为非管制文件或参考用不作更新之服务

统盟(无锡)电子有限公司

GENESIS作业流程

版本编号

ED-3-CH-008

版次

A

修定日期

2007年07月01日

页次

第6页,共18页

6-3-6依钻孔层涨大内层隔离pad,pth单边大7mil,npth单边大10mil

dd.DFM>Optimization>Power/GroundOptimization,ERF选Power/Ground(mils),查看结果,把隔离ring不够的pad加大

ee.如果有比钻孔小的隔离pad,要开org的钻孔与内层查看,若原稿就是如此,可删除,否则要询问

6-3-7分析

Analysis>Power/GroundCheck,ERF选P/G(mils)

ff.PTHannularRing:

ring边距离(内层的ring边代表隔离)

gg.PTHtoCopper:

pad到铜箔

hh.Slivers:

长条,不用处理

ii.LocalSpacing:

细小区块,3mil以下需要补满

6-3-8图形比对

jj.copyorg内层、pcb内层、drill层以及加大20mil的nt层比对

kk.检查是否还有未加大的隔离pad

ll.检查被隔离pad包围后,通道过小不足10mil的情况,有的话削隔离pad,让电流顺利通过

6-3-9测netlist

mm.先把其余不测的层次之层性改为Misc

nn.开启Actions>NetlistAnalysis,输入做为参考层的Job及step

oo.从上半部的Netlisttype选择出Current,接着执行Recalc

pp.再从type里选出Reference,接着在update里选择settoCURnetlist

qq.在下半部输入正确的Job及step,type选择Current,再按Recalc

rr.最后再按compare,查看结果,只要没有short或是open的情况即可

如未盖蓝色资料室发文章即为非管制文件或参考用不作更新之服务

统盟(无锡)电子有限公司

GENESIS作业流程

版本编号

ED-3-CH-008

版次

A

修定日期

2007年07月01日

页次

第7页,共18页

6-4内层走线层

6-4-1涨ring

依钻孔层涨大内层线路pad,单边至少要大4mil

DFM>Optimization>Signallayer,ERF选inner-4ring,查看结果,把没放大的手动放大

6-4-2所有对象放大

Edit>Resize>Global,全面加大预放值(依checklist上的标示)

6-4-3套nt

利用nt层套负片到内层,使npth与铜箔线路保持安全间距

ss.把nt层成型线加大16mil(此时的成型线为28mil=12+16),pad加大16mil(单边大6mil),方便用来与内层比对

tt.用Action>ReferenceSelection的指令,在mode字段选Covered,而

uu.ReferenceLayer的字段输入nt,按apply,然后删除反白的对象(ctrl+b),被删掉的对象是标示npth 的pad

vv.查看成型线的地方,如有碰到铜箔则需套除(用Edit>copy>otherlayer,Invert要选yes),若套除的铜箔区有线路、pad,缩小为24mil的成型线来套,仍碰到则需询问客户(套除后代表线路或铜面距成型边有12mil以上的安全距离)

成型边有金手指的部分同GND&VCC内缩处理

6-4-4最后各层以配合SearchNT层的方式来查看各个Npth孔(利用过滤器里的search,出现searchpopup窗口后,searchlayer字段选nt层,可把线的对象关掉),如果遇到铜箔则需把所套的NT负片再加大8mils;如有碰到线段或pad,需询问客户,是否移线或削pad以达到制程标准(套除后代表npth孔距线路至少6mil,距铜箔10mil)如果觉得铜箔与pad的间距有点小,可先分析处理铜箔与pad的间距问题.

6-4-5削pad

削完后ring边保留3mil,极限2.5mil

如未盖蓝色资料室发文章即为非管制文件或参考用不作更新之服务

统盟(无锡)电子有限公司

GENESIS作业流程

版本编号

ED-3-CH-008

版次

A

修定日期

2007年07月01日

页次

第8页,共18页

ww.DFM>Optimization>Signallayer,ERF选inner(0.5或1)oz-shave(3.5或3),依op设计的要求,查看结果

xx.未达最小间距要求者,自行削pad(极限2.5mil)

yy.如果有被计算机削的pad旁有铜箔,被削的应该是铜箔,所以要把计算机削pad用的负片拿掉,自行削铜箔

6-4-6加泪滴(b56.K60不加泪滴)

要自行先将要加泪滴的pad选取,可使用影响层,多层一起加泪滴

zzz.先用过滤器把size介于最小钻孔到60mil的pad全部选取起来(DFM会自行比对出有钻

aaa.孔的pad加上泪滴)

bbb.DFM>Yield>improvement>AdvancedTeardropsCreations,ERF选InnerTeardrop(mils),查

ccc.看结果

ddd.开长条图选择性查看,手动把接线小于15mil而计算机未自动加泪滴的pad加上泪滴(在

eee.加线的功能上,其属性要设为Tear_drop:

勾选Attributes,values里要选Tear_drop)

fff.用过滤器挑出刚刚计算机加上的泪滴线,Edit>Resize>Global缩小0.1mil方便以后修改

ggg.时选取

6-4-7分析

Analysis>SignalLayerCheck,ERF选inner-4ring(mils)

hhh.Padtopad:

最少3mil

iii.PadtoCircuit:

最少3mil

jjj.CircuittoCircuit:

最少3mil

kkk.LocalSpacing:

不足3mil要补

6-4-8图形比对

lll.开org内层线路、pcb内层线路、drill层以及加大16 mil的nt层核对

mmm.核对时,铜箔区内的npth孔周围应是挖空的,才表示有足够距离,其余的线路或铜箔只要不碰到nt即可

nnn.核对完记得将nt层回复到12mil的size,若是怕忘记,在套除时可以另外copy一层来使用,保持nt层size的不变

6-4-9测netlist

ooo.先把其余不测的层次之层性改为Misc

ppp.开启Actions>NetlistAnalysis,输入做为参考层的Job及step

如未盖蓝色资料室发文章即为非管制文件或参考用不作更新之服务

统盟(无锡)电子有限公司

GENESIS作业流程

版本编号

ED-3-CH-008

版次

A

修定日期

2007年07月01日

页次

第9页,共18页

qqq.从上半部的Netlisttype选择出Current,接着执行Recalc

rrr.再从type里选出Reference,接着在update里选择settoCURnetlist

sss.在下半部输入正确的Job及step,type选择Current,再按Recalc

ttt.最后再按compare,查看结果,只要没有short或是open的情况即可

6-5Ary排版

6-5-1做完pcb内层后,进入Matrix新增一step命名为ary,进入arystep,将pcb排版,做出折断边与块状铜箔,在折断边加上AI孔、光学点及阻抗测线,排屑孔以及V-cut测点等对象,视checklist如何注明

6-5-2做出nt层的成型线

6-5-3先确认pcb内nt的成型线尺寸是否符合彩图或机构图,之后设定排版时才不会有误差,排版有三种排法

uuu.手动排版

Step>Panelization>S&R>Edit叫出排版工具列

Horiz(Vert)gap:

pcb水平与垂直的间距

点选addsteps,NumX(Y):

X与Y轴方向的片数

vvv.自动排版(含折断边)

Step>Panelization>Step&Repeat>Automatic叫出自动排版窗口

setpname输入pcb;mode选择parameters

panelwidth(height):

成型尺寸X(Y)

paneltop(bottom.left.right)margin:

pcb到上(下.左.右)方版边距离

panelstepX(Y):

pcb在x(y)轴上的间距,执行后可得排版框

www.阴阳板(多pcb合并也可使用)

先进Matrix产生一个pcb2空层,把pcb每层的内容copy到pcb2相对应的层次,例如pcb的cdot的内容会在pcb2的sdot里(dri、nt、csdt1直接copy即可)

进入ary执行Step>Panelization>Step&Repeat>Table叫出并板窗口

AnchorPoint:

pcb下标点

Nx、Ny:

X与Y轴方向的片数

Dx、Dy:

X与Y轴方向的间距

Angle:

旋转角度

Mirror:

是否镜射

如未盖蓝色资料室发文章即为非管制文件或参考用不作更新之服务

统盟(无锡)电子有限公司

GENESIS作业流程

版本编号

ED-3-CH-008

版次

A

修定日期

2007年07月01日

页次

第10页,共18页

xxx.勾选Editorcontrols中的S&RFeatures可以在ary显示出pcb图形,但是无法变更修改pcb的任何内容

yyy.Step>Panelization>S&EEdit可叫出排版工具列来旋转(RotateStep)pcb内容

zzzz.利用格点Grid,根据建立的排版框画出ary的成型线

6-5-4根据OP在彩图与孔径设计表上的设计,在dri层及nt层加上AI工具孔、排屑孔、邮票孔,dri层还多了阻抗测孔

6-5-5内层GND&VCC的折断边添加上比AI孔大32mil以及比阻抗测孔大20mil的隔离pad

6-5-6在内层走线层以及外层线路层的折断边加上块状铜箔(桥接部分不加铜箔);在块状铜箔做出AI孔与阻抗测孔的隔离pad

aaaa.在折断边拉出接近大小的铜箔区块

bbbb.copy加大32mil的nt层负片套铜箔区块,产生内缩22mil(大约20-25mil皆可)以及比

cccc.AI孔大32mil的隔离pad(规范是单边15mil)

dddd.copy加大20mil的阻抗测孔负片套铜箔

6-5-7依彩图、checklist添加光学点于外层线路上(记得同板内一样要加大),需先套大于光学点防焊6mil以上的负片做隔离pad(光学点防焊会在checklist上会注明大小)

6-5-8做出阻抗测线

checklist会标示要导通以及接线的层次,以六层板为例,若标示出L1(加线)、L2、L5、L6(加线),表示

eeee.L1该层加测线导通,其它三孔做隔离pad(仍要有线路pad;还需注明测孔层别,用字高60、宽40、粗8mil左右)

ffff.L2该层导通,其它三孔做隔离pad

gggg.L3该层全部做隔离pad

hhhh.L4该层全部做隔离pad

iiii.L5该层导通,其它三孔做隔离pad

jjjj.L6该层加测线导通,其它三孔做隔离pad(仍要有线路pad)

线路隔离pad=钻孔+20

线路pad=钻孔+放大值+8

防焊pad=钻孔+放大值+8+4

测线线宽=依ckecklist上op设计+放大值

测线隔离负片=测线线宽x4

如未盖蓝色资料室发文章即为非管制文件或参考用不作更新之服务

统盟(无锡)电子有限公司

GENESIS作业流程

版本编号

ED-3-CH-008

版次

A

修定日期

2007