升压降压电源电路工作原理Word文件下载.docx

《升压降压电源电路工作原理Word文件下载.docx》由会员分享,可在线阅读,更多相关《升压降压电源电路工作原理Word文件下载.docx(29页珍藏版)》请在冰点文库上搜索。

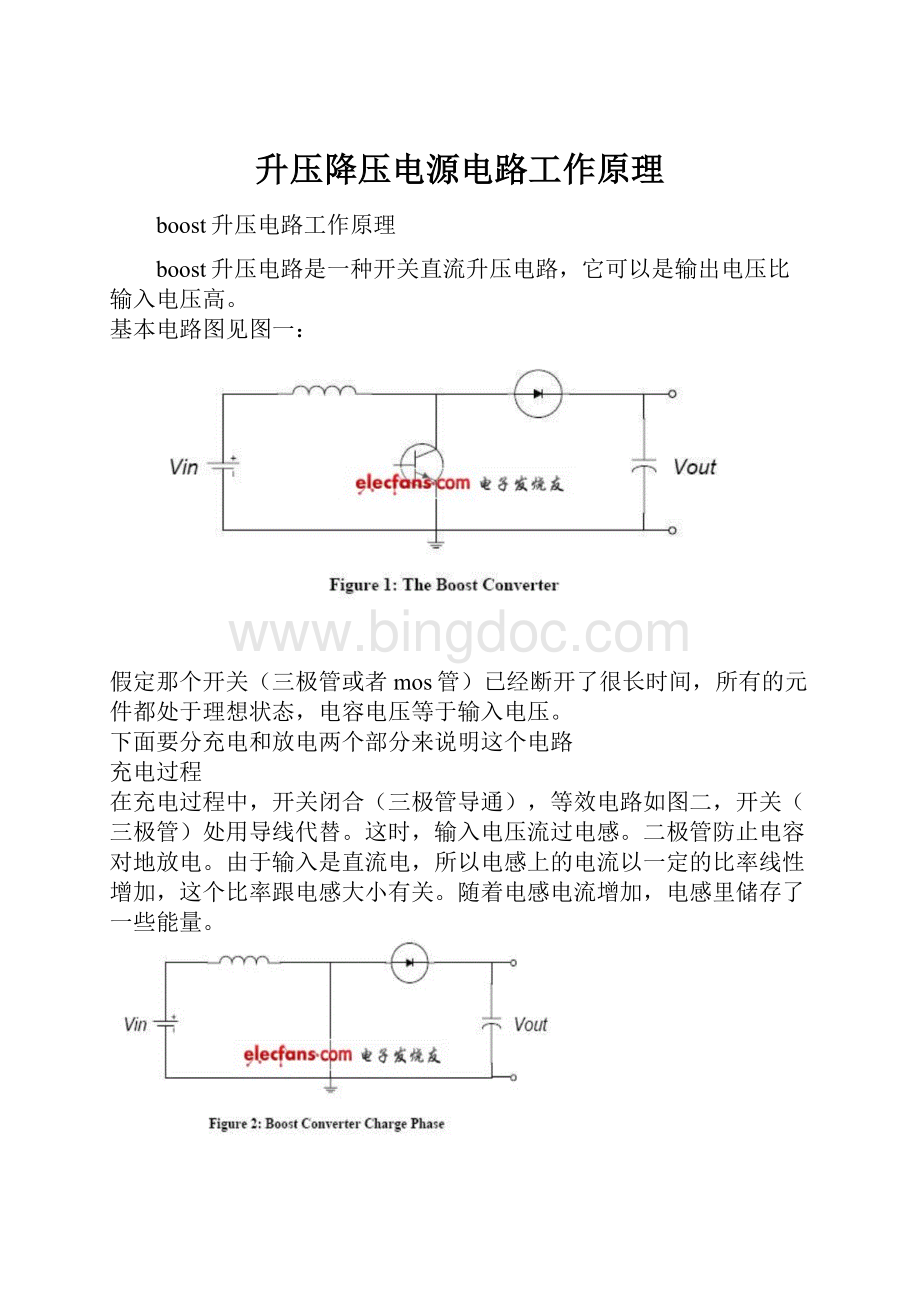

开关管导通时,电源经由电感-开关管形成回路,电流在电感中转化为磁能贮存;

开关管关断时,电感中的磁能转化为电能在电感端左负右正,此电压叠加在电源正端,经由二极管-负载形成回路,完成升压功能。

既然如此,提高转换效率就要从三个方面着手:

1.尽可能降低开关管导通时回路的阻抗,使电能尽可能多的转化为磁能;

2.尽可能降低负载回路的阻抗,使磁能尽可能多的转化为电能,同时回路的损耗最低;

3.尽可能降低控制电路的消耗,因为对于转换来说,控制电路的消耗某种意义上是浪费掉的,不能转化为负载上的能量。

具体计算

已知参数:

输入电压:

12V---Vi

输出电压:

18V---Vo

输出电流:

1A---Io

输出纹波:

36mV---Vpp

工作频率:

100KHz---f

1:

占空比

稳定工作时,每个开关周期,导通期间电感电流的增加等于关断期间电感电流的减少,即Vi*don/(f*L)=(Vo+Vd-Vi)*(1-don)/(f*L),整理后有

don=(Vo+Vd-Vi)/(Vo+Vd),参数带入,don=0.572

2:

电感量

先求每个开关周期内电感初始电流等于输出电流时的对应电感的电感量

其值为Vi*(1-don)/(f*2*Io),参数带入,Lx=38.5uH,

deltaI=Vi*don/(L*f),参数带入,deltaI=1.1A

当电感的电感量小于此值Lx时,输出纹波随电感量的增加变化较明显,

当电感的电感量大于此值Lx时,输出纹波随电感量的增加几乎不再变小,由于增加电感量可以减小磁滞损耗,另外考虑输入波动等其他方面影响取L=60uH,

deltaI=Vi*don/(L*f),参数带入,deltaI=0.72A,

I1=Io/(1-don)-(1/2)*deltaI,I2=Io/(1-don)+(1/2)*deltaI,

参数带入,I1=1.2A,I2=1.92A

3:

输出电容:

此例中输出电容选择位陶瓷电容,故ESR可以忽略

C=Io*don/(f*Vpp),参数带入,

C=99.5uF,3个33uF/25V陶瓷电容并联

4:

磁环及线径:

查找磁环手册选择对应峰值电流I2=1.92A时磁环不饱和的适合磁环

Irms^2=(1/3)*(I1^2+I2^2-I1*I2),参数带入,irms=1.6A

按此电流有效值及工作频率选择线径

其他参数:

电感:

L占空比:

don

初始电流:

I1峰值电流:

I2线圈电流:

Irms

C电流的变化:

deltaI整流管压降:

Vd

两种降压升压电路原理图

2011年11月15日11:

06

来源:

电子发烧友网

作者:

小兰

我要评论(0)

图显示两种降压升压电路,可在输入电压可能大于或小于输出电压的情形下使用。

这些电路与前述两种降压拓扑有相同的折冲特点,与电流侦测电阻与门极驱动的位置有关。

图2的降压升压拓扑,显示接地参考的闸极驱动。

此拓扑需要位准移位电流侦测讯号,不过反向的升压降压拓扑则具有接地参考的电流侦测及位准移位闸极驱动。

如果控制IC与负输出有关,且电流侦测电阻与LED进行交换,即可利用有效的方式配置反向升压降压拓扑。

只要适当控制IC,即可直接测量输出电流,也可以直接驱动MOSFET。

求DC-DC升降压电路原理及设计要点?

DC-DC升压与降压电路简介

DC/DC转换器电路的各种特性(效率、纹波、负载瞬态响应等)可根据外设元件的变更而变更,尽量在各种制约条件下,设计出最接近要求规格的DC/DC转换器电路。

1、DC/DC转换的基本工作原理

最基本的基本型DC/DC转换器电路为升压和降压电路。

1)升压电路

FET为ON时的电路图

在FET为ON的时间里在L积蓄电流能。

虚线表示的电流路径虽是微小的漏电流,但会使轻负载的效率变差。

FET为OFF时的电路图

在FET为OFF时,L要保持OFF前的电流值,相当于在输入回路增加了一个“电源”。

由于线圈的左端被强制性固定于VIN,因此输出VOUT的电压要大于VIN,即升压电路原理。

由此,FET的ON时间越长(FET的触发占空比D越大),L里积蓄的电流能越大,越能获得电源功率,于是升压就越高。

但是,FET的ON时间太长的话,给输出侧供电的时间就极为短暂,FET为ON时的损失也就增大,变换效率变差。

因此,通常要限制占空比的最大值,不超过适宜的占空比D。

2)降压电路

在FET为ON的时间里,L积蓄电流能的同时为输出供电。

在FET为OFF时,L要保持OFF前的电流值,使SBD为ON。

此时,由于线圈的左端被强制性地降到0V以下,VOUT的电压下降,即降压电路原理。

由此,FET的ON时间长L里积蓄的电流能越大,越能获得大功率电源,降压的幅度越小。

降压时,由于FET为ON时也要给输出供电,所以不需要限制占空比的最大值。

2、DC/DC转换电路的设计要点

设计要点:

(1)稳定工作(=不会因异常振动等误动作、烧损、过电压而损坏)

(2)效率大

(3)输出纹波小

(4)负载瞬态响应好

这些设计指标可通过变更DC/DC转换器IC和外设元件得到某种程度的改善。

3、开关频率的选择

DC/DC转换器IC具备固有的开关频率,频率的不同会对各种特性产生影响。

以XC9237A18C(1.2MHz)和XC9237A18D(3MHz)为例表明开关频率与效率的关系。

测试电路图(降压型DC-DC),如下图所示。

CIN:

10μF,CL:

10μF,L=4.7μH(NR3015T-4R7M),Topr=25℃

XC9237A18C(振荡频率1.2MHz)开关频率与效率的关系,如下图所示:

XC9237A18D(振荡频率3MHz)开关频率与效率的关系,如下图所示:

效率最大的电流值不同是因为不同的开关频率适合的感应系数值也不同的缘故。

对于结构相同的线圈,感应系数越大直流电阻越增加,重负载时的损失增加,由此,效率最大的电流值越是低频的越会向轻负载侧移动。

相反,频率高则因FET的充放电次数增加和IC自身的静态消耗电流增大,3MHz产品比1.2MHz产品在轻负载时的效率大幅度变差。

综合来看,可知1.2MHz产品的效率峰值大,效率最大的输出电流值峰值小。

此外,PFM工作时,轻负载时的频率都进一步下降,效率明显得到改善。

3、FET的选择

RDS:

Drain-sourceON-Resistance

RDS引起的损失:

RDS可以看成是FET的漏源极间电阻成分,因而会发热而损失能量,负载越大其损失越是增大。

因此,重负载时减少RDS引起的损失效果较好。

CISS:

InputCapacitance

CISS引起的损失:

CISS可以看成是FET的栅源极间充放电时被丢弃的功率。

驱动电压和开关频率越大损失就越大,由于重负载时和轻负载时损失值基本相同,所以会使轻负载时的效率大幅度变差。

因此,轻负载时减少CISS引起的损失对提高效率的效果较好。

虽然RDS和CISS都是越小损失也越小,但因RDS和CISS成反比关系,改善损失大的一方效果更好。

一般电压额定值定为使用电压的1.5倍~2倍,RDS和CISS引起的损失较小。

输入电流=输出(负载)电流×

输出电压÷

输入电压÷

效率

效率未知时,可姑且升压时采用70%、降压时采用80%来计算。

测试实例:

更换FET,测试效率,FET的参数规格如下表所示:

XC9220C093的测试电路:

测试的效率图:

4、线圈的选择

线圈引起的损失表现为线圈的绕线电阻RDC和铁氧体磁心产生的损失等。

开关频率不同的话,最佳L值也不同。

因为线圈的电流与FET的ON时间成正比,与L值成反比。

对于2MHz左右的开关频率,可以认为线圈的大部分损失是RDC引起的损失,首先应选择RDC小的线圈。

如果为了减小RDC而选择L值过小的线圈的话,在FET为ON的时间内电流值过大,FET、SBD、线圈产生的热损失变大,效率下降。

而且,因电流增加,纹波也增大。

相反,如果L值过大的话,RDC变大,不仅重负载时的效率变差,而且铁氧体磁心发生磁饱和,L值急速减少,这样就不能发挥出线圈的性能,陷入电流过大引起发热的危险状态。

因而,为了在L值大的线圈流经大电流,形状上必须有一定程度的大小,以避免磁饱和。

综上所述,相对于线圈的外形尺寸和效率两个方面,适当的L值已被限定,如下表所示:

实例:

XC9104D093(升压)电路只变更了L值后的效率和纹波。

测试电路如下:

XC9220A093(降压)电路只变更了L值后的效率和纹波。

5、SBD的选择

SBD的损失为正向热损失VF×

IF和反向漏电流IR引起的热损失的合计值。

因此,选择VF、IR都小的产品比较理想。

但是,VF与IR成反比关系,一般要视负载电流而选用。

VF在重负载时大,考虑到IR与负载无关为一定的值,所以轻负载时选择IR小的产品对提高效率的效果较好,重负载时选择VF小的产品效果较好。

选择SBD的要点见下表:

比较两个SBD在轻重负载时的效率。

与XBS203V17相比,XBS204S17的VF大IR小,轻负载时的效率好,重负载时的效率差。

下表是详细参数:

测试电路和效率曲线如下:

6、CL的选择

CL越大则纹波越小,但过分大的话,电容器的形状也大,成本提高。

CL由所需的纹波大小而定。

以10mV~40mV的纹波大小为目标,升压和降压CL值参考下表:

升压:

CL值为表中值乘以升压比

降压:

CL值为表中值乘以降压比

纹波与ESR成正比,与电容值成反比。

以下是测试电路和纹波与CL的关系图:

注:

铝电解电容时,没有并联的陶瓷电容的话,ESR过大难以获得输出电流。

7、CIN的选择

虽然不及CL对输出稳定性的影响大,但CIN也是电容值越大、ESR越小则输出稳定性越好,纹波也越小。

大到某种程度,降低输出纹波的效果会变小,从防止对输入侧的电磁干扰EMI的意义上说,电容值应从CL的一半左右开始探讨较好。

CIN不会因ESR太小而输出振荡,所以ESR越低越好。

CIN与纹波的关系,测试电路如下:

CIN值变化的输入侧纹波,见下图:

8、RFB1,和RFB2的选择

使用FB(反馈)产品时,RFB1、RFB2用于决定输出电压,对同一输出电压有时可考虑多种组合。

此时选择RFB1+RFB2=150kΩ~500kΩ比较妥当。

这里成为问题的是轻负载时的效率和重负载时的输出稳定性。

因为流向RFB1、RFB2的电流没有被作为输出功率使用,而视作DC/DC转换器的损失,所以要想提高轻负载时的效率的话,要将RFB1、RFB2设定得大一些(RFB1+RFB2<

1MΩ左右)。

而要想提高重负载时的瞬态响应的话,则要做好轻负载时的效率差的准备,将RFB1、RFB2设定得比标准值小1位数,使FB端子的电压稳定性提高即可。

9、CFB的选择

CFB是纹波反馈调整用电容器,该值也会影响负载瞬态响应。

CFB过小:

电压恢复到恒定状态的时间短,但负载变重时电压急剧下降;

CFB过大:

负载变重时的瞬间电压下降虽小,但电压恢复到恒定状态的时间长。

在特别的情况下,重负载时会出现从CFB反馈到FB端子的纹波的影响过大,输出不稳定的情况。

出现这种情况时,不连接CFB有时能使工作稳定。

求电容降压限流电路工作原理?

?

电容降压工作原理发起投票|删除电容降压的工作原理2009年04月27日星期一13:

25

电容降压的工作原理并不复杂。

他的工作原理是利用电容在一定的交流信号频率下产生的容抗来限制最大工作电流。

例如,在50Hz的工频条件下,一个1uF的电容所产生的容抗约为3180欧姆。

当220V的交流电压加在电容器的两端,则流过电容的最大电流约为70mA。

虽然流过电容的电流有70mA,但在电容器上并不产生功耗,应为如果电容是一个理想电容,则流过电容的电流为虚部电流,它所作的功为无功功率。

根据这个特点,我们如果在一个1uF的电容器上再串联一个阻性元件,则阻性元件两端所得到的电压和它所产生的功耗完全取决于这个阻性元件的特性。

例如,我们将一个110V/8W的灯泡与一个1uF的电容串联,在接到220V/50Hz的交流电压上,灯泡被点亮,发出正常的亮度而不会被烧毁。

因为110V/8W的灯泡所需的电流为8W/110V=72mA,它与1uF电容所产生的限流特性相吻合。

同理,我们也可以将5W/65V的灯泡与1uF电容串联接到220V/50Hz的交流电上,灯泡同样会被点亮,而不会被烧毁。

因为5W/65V的灯泡的工作电流也约为70mA。

因此,电容降压实际上是利用容抗限流。

而电容器实际上起到一个限制电流和动态分配电容器和负载两端电压的角色。

采用电容降压时应注意以下几点:

1根据负载的电流大小和交流电的工作频率选取适当的电容,而不是依据负载的电压和功率。

2限流电容必须采用无极性电容,绝对不能采用电解电容。

而且电容的耐压须在400V以上。

最理想的电容为铁壳油浸电容。

3电容降压不能用于大功率条件,因为不安全。

4电容降压不适合动态负载条件。

5同样,电容降压不适合容性和感性负载。

6当需要直流工作时,尽量采用半波整流。

不建议采用桥式整流。

而且要满足恒定负载的条件。

以上是电容降压工作原理的简单介绍。

前些日子我曾再次提出一个问题,就是只用电阻和电容可以组成什么电路,进一步讲只用一个电阻和一个电容可以组成什么电路。

此篇可以是一个回答,有兴趣的可以再想一想还能组成什么电路。

其实电阻、电容和电感作为电子电路的基本元件,熟知它们的特性并灵活地应用它。

采用电容降压电路是一种常见的小电流电源电路﹐由于其具有体积小﹑成本低﹑电流相对恒定等优点﹐也常应用于LED的驱动电路中。

图一为一个实际的采用电容降压的LED驱动电路﹕请注意﹐大部分应用电路中没有连接压敏电阻或瞬变电压抑制晶体管﹐建议连接上﹐因压敏电阻或瞬变电压抑制晶体管能在电压突变瞬间(如雷电﹑大用电设备起动等)有效地将突变电流泄放﹐从而保护二级关和其它晶体管﹐它们的响应时间一般在微毫秒级。

电路工作原理﹕

电容C1的作用为降压和限流﹕大家都知道﹐电容的特性是通交流﹑隔直流﹐当电容连接于交流电路中时﹐其容抗计算公式为﹕

XC=1/2πfC

式中﹐XC表示电容的容抗﹑f表示输入交流电源的频率﹑C表示降压电容的容量。

流过电容降压电路的电流计算公式为﹕

I=U/XC

式中I表示流过电容的电流﹑U表示电源电压﹑XC表示电容的容抗在220V﹑50Hz的交流电路中﹐当负载电压远远小于220V时﹐电流与电容的关系式为﹕

I=69C

其中电容的单位为uF﹐电流的单位为mA

下表为在220V﹑50Hz的交流电路中﹐理论电流与实际测量电流的比较

电阻R1为泄放电阻﹐其作用为﹕当正弦波在最大峰值时刻被切断时﹐电容C1上的残存电荷无法释放﹐会长久存在﹐在维修时如果人体接触到C1的金属部分﹐有强烈的触电可能﹐而电阻R1的存在﹐能将残存的电荷泄放掉﹐从而保证人﹑机安全。

泄放电阻的阻值与电容的大小有关﹐一般电容的容量越大﹐残存的电荷就越多﹐泄放电阻就阻值就要选小些。

经验数据如下表﹐供设计时参考﹕

D1~D4的作用是整流﹐其作用是将交流电整流为脉动直流电压。

C2﹑C3的作用为滤波﹐其作用是将整流后的脉动直流电压滤波成平稳直流电压

压敏电阻(或瞬变电压抑制晶体管)的作用是将输入电源中瞬间的脉冲高压电压对地泄放掉﹐从而保护LED不被瞬间高压击穿。

LED串联的数量视其正向导通电压(Vf)而定﹐在220VAC电路中﹐最多可以达到80个左右。

组件选择﹕电容的耐压一般要求大于输入电源电压的峰值﹐在220V,50Hz的交流电路中时﹐可以选择耐压为400伏以上的涤纶电容或纸介质电容。

D1~D4可以选择IN4007。

滤波电容C2﹑C3的耐压根据负载电压而定﹐一般为负载电压的1.2倍。

其电容容量视负载电流的大小而定。

工作原理,两个阶段²

t=0时V导通,E向负载供电,uo=E,io按指数曲线上升²

t=t1时V关断,io经VD续流,uo近似为零,io呈指数曲线下降²

为使io连续且脉动小,通常使L值较大

图3-1降压斩波电路的原理图及波形a)电路图b)电流连续时的波形c)电流断续时的波形Ø

数量关系电流连续时,负载电压平均值

(3-1)

a——导通占空比,简称占空比或导通比

Uo最大为E,减小a,Uo随之减小——降压斩波电路。

也称为Buck变换器(BuckConverter)。

负载电流平均值

(3-2)电流断续时,uo平均值会被抬高,一般不希望出现Ø

斩波电路三种控制方式

(1)脉冲宽度调制(PWM)或脉冲调宽型——T不变,调节ton

(2)频率调制或调频型——ton不变,改变T

(3)混合型——ton和T都可调,使占空比改变其中PWM控制方式应用最多Ø

基于“分段线性”的思想,可对降压斩波电路进行解析

WelcomeTo

Download!

!

欢迎您的下载,资料仅供参考!