完整word版集成电路CAD复习例题 +解析Word下载.docx

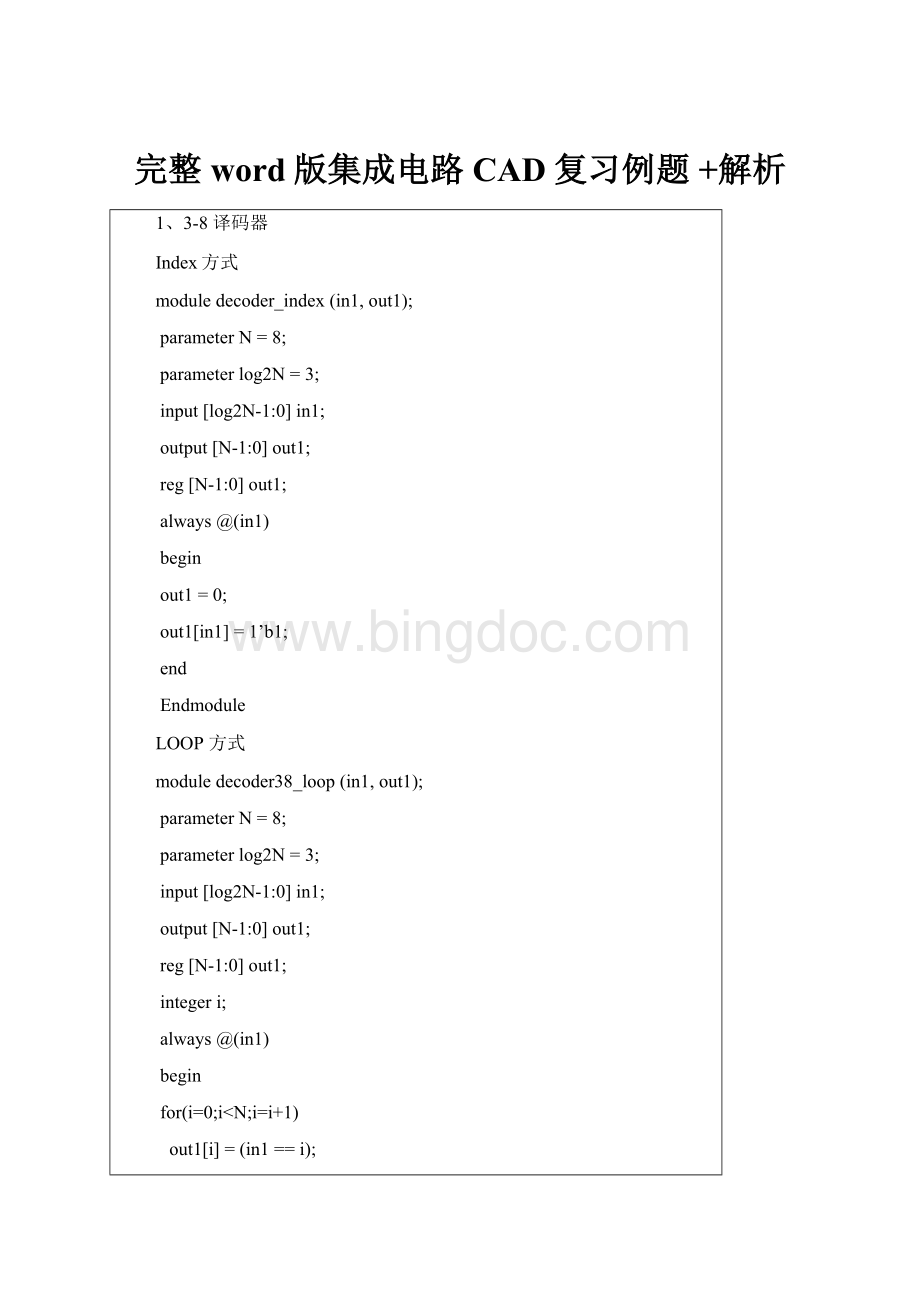

《完整word版集成电路CAD复习例题 +解析Word下载.docx》由会员分享,可在线阅读,更多相关《完整word版集成电路CAD复习例题 +解析Word下载.docx(18页珍藏版)》请在冰点文库上搜索。

另一种:

modulecode8_3(in,out)

input[7:

0]in;

output[2:

0]out;

wire[7:

reg[2:

always@(in)begin

if(in[7]==1)out=3’111;

elseif(in[6]==1)out=3’b110;

elseif(in[5]==1)out=3’101;

elseif(in[4]==1)out=3’b100;

elseif(in[3]==1)out=3’b011;

elseif(in[2]==1)out=3’b010;

elseif(in[1]==1)out=3’b001;

elseif(in[0]==1)out=3’b000;

default:

out=3’bx;

end

endmodule

3、奇偶校验位产生器

moduleparity(even_bit,odd_bit,input_bus);

outputeven_bit,odd_bit;

input[7:

0]input_bus;

assigneven_bit=^input_bus;

//产生偶校验位

assignodd_bit=~even_bit;

//产生奇校验位

4、4选1数据选择器

第一种方法

modulemux(d1,d2,d3,d4,se1,se2,dout);

inputd1;

inputd2;

inputd3;

inputd4;

inputse1;

inputse2;

outputdout;

regdout;

always@(d1ord2ord3ord4orse1orse2)

case({se1,se2})

2'

b00:

dout=d1;

b01:

dout=d2;

b10:

dout=d3;

b11:

dout=d4;

endcase

第二种方法

if(!

se1)

begin

se2)

dout=d1;

else

dout=d2;

end

elsebegin

dout=d3;

dout=d4;

第三种方法

modulese(d1,d2,d3,d4,se1,se2,dout);

assigndout=se1?

se2?

d4:

d3:

d2:

d1;

第四种方法

modulemux4_1(out,in0,in1,in2,in3,sel);

outputout;

inputin0,in1,in2,in3;

input[1:

0]sel;

regout;

always@(in0orin1orin2orin3orsel)//敏感信号列表

case(sel)

b00:

out=in0;

b01:

out=in1;

b10:

out=in2;

b11:

out=in3;

out=2'

bx;

5、4位全加器及4位全加器的仿真程序

moduleadder4(cout,sum,ina,inb,cin);

output[3:

0]sum;

outputcout;

input[3:

0]ina,inb;

inputcin;

assign{cout,sum}=ina+inb+cin;

Endmodule

第二种:

moduleadder_4bit(s,co,a,b,ci);

//4位全加器//

output[3:

0]s;

outputco;

input[3:

0]a,b;

inputci;

f_adderf0(a[0],b[0],ci,s[0],ci1);

f_adderf1(a[1],b[1],ci1,s[1],ci2);

f_adderf2(a[2],b[2],ci2,s[2],ci3);

f_adderf3(a[3],b[3],ci3,s[3],co);

endmodule

modulef_adder(ain,bin,cin,sum,cout);

//1位全加器//

outputsum,cout;

inputain,bin,cin;

wired,e,f;

h_adder(ain,bin,e,d);

h_adder(e,cin,sum,f);

or(cout,d,f);

moduleh_adder(a,b,so,co);

//半加器//

inputa,b;

outputso,co;

assignso=a^b;

assignco=a&

b;

4位全加器的仿真程序

`timescale1ns/1ns

`include"

adder4.v"

moduleadder_tp;

//测试模块的名字

reg[3:

//测试输入信号定义为reg型

regcin;

wire[3:

//测试输出信号定义为wire型

wirecout;

integeri,j;

adder4adder(sum,cout,a,b,cin);

//调用测试对象

always#

cin=~cin;

//设定cin的取值

initial

begin

a=0;

b=0;

cin=0;

for(i=1;

16;

i=i+1)

#10a=i;

//设定a的取值

end

initial

begin

for(j=1;

j<

j=j+1)

#10b=j;

//设定b的取值

initial//定义结果显示格式

$monitor($time,,,"

%d+%d+%b={%b,%d}"

a,b,cin,cout,sum);

#160$finish;

endmodule

6、带同步清0、同步置1的D触发器

moduled_ff_1(CLK,RSTn,clr,D,Q,en);

inputCLK,RSTn,clr;

inputD,en;

outputQ;

regQ;

always@(posedgeCLK)begin

if(~RSTn)begin

Q<

=1'

b1;

end

elsebegin

if(clr)beginQ<

elsebegin

if(en)begin

=D;

endelsebegin

=Q;

end

7、带异步清0、异步置1的JK触发器

moduleJK_FF(CLK,J,K,Q,RS,SET);

inputCLK,J,K,SET,RS;

regQ;

always@(posedgeCLKornegedgeRSornegedgeSET)

if(!

RS)Q<

b0;

elseif(!

SET)Q<

elsecase({J,K})

2'

Q<

=~Q;

default:

Q<

endcase

8、8位数据锁存器

modulelatch_8(qout,data,clk);

output[7:

0]qout;

input[7:

0]data;

inputclk;

reg[7:

always@(clkordata)

if(clk)qout<

=data;

9、同步置数、同步清零的8位二进制计数器

modulecount(out,data,load,reset,clk);

inputload,clk,reset;

reg[7:

always@(posedgeclk)//clk上升沿触发

if(!

reset)

out=8'

h00;

//同步清0,低电平有效

elseif(load)

out=data;

//同步预置

else

out=out+1;

//计数

10、异步清零、同步置数的1位十进制计数器

modulecount10(out,data,load,reset,clk);

reg[3:

always@(posedgeclkornegedgereset)//clk上升沿触发

out=8'

elseif(out<

9)

out=out+1;

out=0;

11、4位串并转换器

modulepal_serial_4(//四位并串转换程序

clk,rst,load,

din,dout

);

inputclk,rst,load;

0]din;

0]databuff;

always@(posedgeclkornegedgerstorposedgeload)

rst)databuff<

=4'

elseif(load)databuff<

=din;

else//databuff<

={databuff[2:

0],1'

b0};

databuff<

=databuff<

<

1;

//将寄存器内的值左移,依次读出

assigndout=databuff[3];

moduleserial_pal_4(//四位串并转换程序

clk,en,rst,

cin,cout

inputcin,clk,en,rst;

0]cout;

always@(posedgeclkornegedgerst)

rst)cout<

elseif(en)

cout<

={cout[2:

0],cin};

elsecout<

=cout;

另一种:

moduleshift(nreset,clk,en,in,out);

inputnreset,clk,en,in;

output[3:

reg[1:

0]count;

//移位计数,控制并行数据更新,这里是4bit并行数据

reg[3:

always@(posedgeclkornegedgenreset)

if(~nreset)

count<

=2'

b00;

=count+2'

b01;

data<

=4'

b0000;

ealeif(en)

={data[2:

0],in};

end//并行输出

out<

elseif(en&

&

(count==2'

b11))

=data;

12、模为60的BCD码加法计数器

modulecount60(qout,cout,data,load,cin,reset,clk);

output[7:

outputcout;

inputload,cin,clk,reset;

always@(posedgeclk)//clk上升沿时刻计数

if(reset)

qout<

=0;

//同步复位

else

if(load)

//同步置数

if(cin)

if(qout[3:

0]==9)//低位是否为9,是则

qout[3:

0]<

//回0,并判断高位是否为5

if(qout[7:

4]==5)

qout[7:

4]<

=qout[7:

4]+1;

//高位不为5,则加1

else//低位不为9,则加1

=qout[3:

0]+1;

assigncout=((qout==8‘h9)&

cin)?

1:

0;

//产生进位输出信号

13、BCD码—七段数码管显示译码器

moduledecode47(a,b,c,d,e,f,g,D3,D2,D1,D0);

outputa,b,c,d,e,f,g;

inputD3,D2,D1,D0;

//输入的4位BCD码

rega,b,c,d,e,f,g;

always@(D3orD2orD1orD0)

case({D3,D2,D1,D0})//用case语句进行译码

4'

d0:

{a,b,c,d,e,f,g}=7'

b1111110;

d1:

b0110000;

b1101101;

b1111001;

b0110011;

d5:

b1011011;

d6:

b1011111;

d7:

b1110000;

d8:

b1111111;

d9:

b1111011;

14、七人投票表决器,4人同意即为通过,反之不通过。

modulevoter7(pass,vote);

outputpass;

input[6:

0]vote;

reg[2:

regpass;

always@(vote)

sum=0;

=6;

i=i+1)//for语句

if(vote[i])sum=sum+1;

if(sum[2])

pass=1;

//若超过4人赞成,则pass=1

pass=0;

15、设计一个简单的状态机,功能是检测一个5位二进制序列“10010”

moduleVrSMex(CLOCK,X,Z);

inputCLOCK,X;

outputZ;

regZ;

0]Sreg,Snext;

parameter[2:

0]A=3'

b000,

B=3'

b001,

C=3'

b010,

D=3'

b011,

E=3'

b100,

F=3'

b101;

always@(posedgeCLOCK)

Sreg<

=Snext;

always@(X,Sreg)begin

case(Sreg)

A:

if(X==0)Snext=A;

elseSnext=B;

B:

if(X==0)Snext=C;

C:

if(X==0)Snext=D;

D:

elseSnext=E;

E:

if(X==0)Snext=F;

F:

defaultSnext=A;

always@(Sreg)

A,B,C,D,E:

Z=0;

Z=1;

defaultz=0;

16、分压式共射放大电路如图所示。

三极管的模型参数为:

IS=1E-16,BF=100,RB=100;

输入交流信号,幅值为1。

求电路的静态工作点,电压放大倍数,输入电阻及输出电阻。

Amplifyingcircuit

VS10AC1

RS12200

C1233.3U

RB137100K

RB23020K

Q1435MQ

RC743.3K

RE501K

CE5050U

C2463.3U

RL605.1K

VCC7012

.MODELMQNPN(IS=1E-16BF=100RB=100)

.OP

.ACLIN101K10K//设交流分析为线性扫描,频率点数10,起始频率1KHZ,终止频率10KHZ

.PLOTACV(6)/V

(2)V

(2)/I(RS)V(6)/I(RL)

.END

17、共栅极放大器(Common-GateAmplifier)又称为电流跟随器,如下图所示,试求其电压增益、电流增益和频宽。

其中NMOS管的沟道宽为60U,长为2U,电阻RG阻值为100K,RD、RL阻值都为4K,RS为100欧姆,电容CC1、CC2、CG都为100UF,电流源IQ为1mA。

问题or,‘,’

*commongateampilifier

.OPTIONSPOST=2LIS

.lib'

.\Mm0355V.l'

tt

M1123GNDNCHW=60UL=2U

RG2GND100K

RDVDD14K

RS4VI100

RLVO04K

CC134100U

CC21VO100U

CG