FPGA仿真流程Word格式.docx

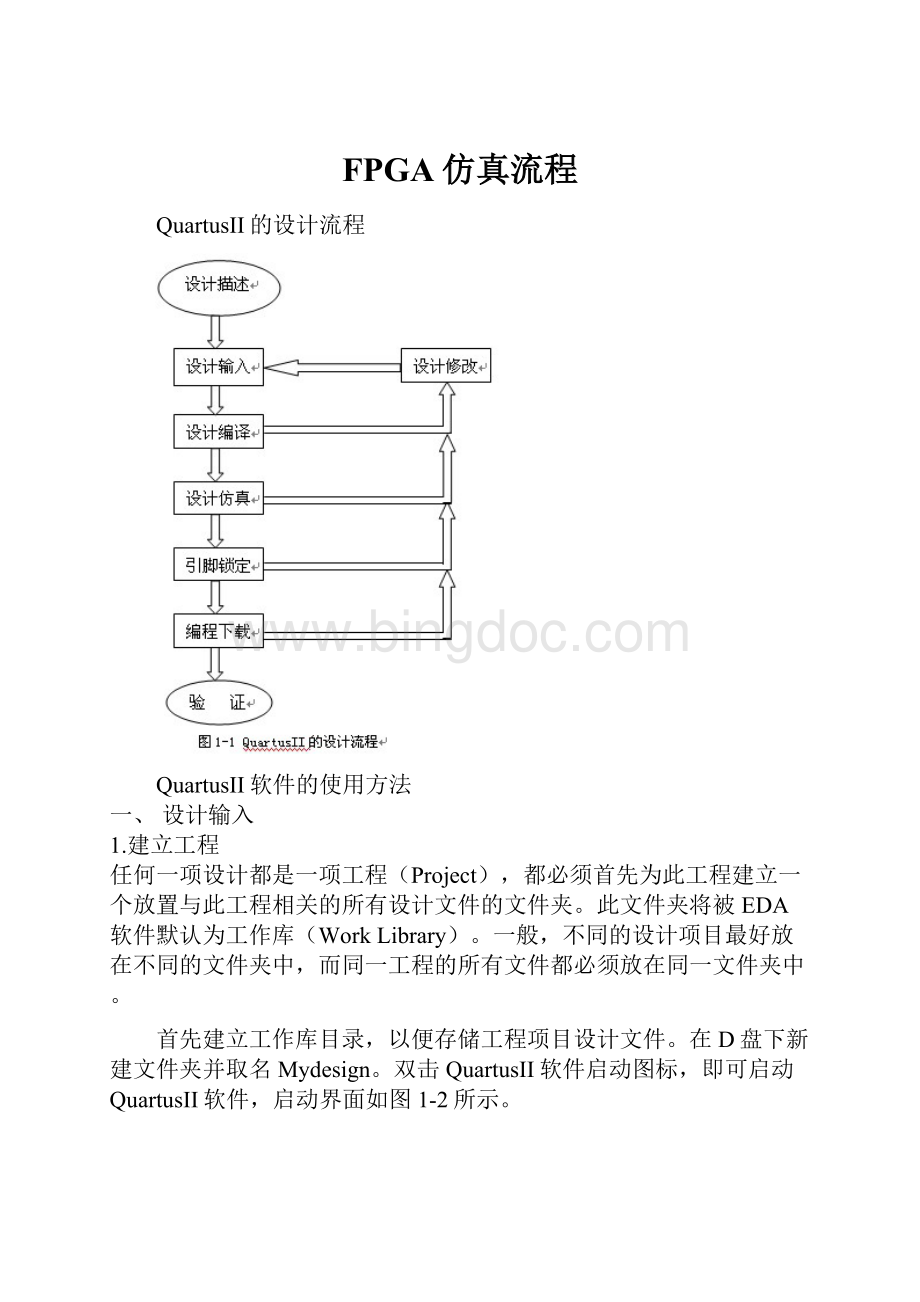

《FPGA仿真流程Word格式.docx》由会员分享,可在线阅读,更多相关《FPGA仿真流程Word格式.docx(31页珍藏版)》请在冰点文库上搜索。

(1)打开建立新工程管理窗。

选择菜单File→NewPrejectWizard命令,即弹出“工程设置”对话框(图1-3),以此来建立新的工程。

(2)在单击图1-3后,出现了设置工程的基本信息,如图1-4所示。

单击此对话框最上一栏右侧的“…”按钮,可以选择工程存放在硬盘上的位置,此例中将工程放在D盘Mydesign文件夹下。

这三行的第一行的d:

\Mydesign表示工程所在的工作库文件夹;

第二行的half_add表示此项工程的工程名,工程名可以取任何其他的名,也可直接用顶层文件的实体名作为工程名,在此就是按这种方式取的名;

第三行是当前工程顶层文件的实体名,这里即为half_add。

(2)将设计文件加入工程中。

单击图1-4中的Next按钮,弹出对话框如图1-5所示,在对话框中单击Filename右侧的“…”按钮,可以将与工程相关的所有VHDL文件(如果有的话)加入进此工程,此工程文件加入的方法有两种:

第1种方法是单击“Add…”按钮,从工程目录中选出相关的VHDL文件;

第2种方法是单击AddAll按钮,将设定的工程目录中的所有VHDL文件加入到工程文件栏中。

如果还没有建立VHDL文件,就直接点击“Next”即可。

(3)选择目标芯片。

单击图1-5中Next按钮出现如图1-6的对话框用来选择目标芯片。

首先在Family栏选芯片系列,在此选FLEX10K系列,并选择此系列的具体芯片EPF10K10LC84-4。

在“Targetdevice”选项下选择“Autodeviceselectedbythefitter”选项,系统会自动给所设计的文件分配一个器件。

如果选择“Specificdeviceselectedin‘Availabledevices’list”选项,用户需指定目标器件。

在右侧的“Filters”窗口“过滤”选择;

Package表示封装;

Pincout表示引脚数,此例选择84;

Speedgrade表示速度等级,此例选择4。

(4)在图1-6中单击“Next”按钮后进入第三方工具选择对话框,如图1-7所示。

用户可以选择所用到的第三方工具,比如ModleSim、Synplify等。

在本例中并没有调用第三方工具,可以都不选.

(5)在图1-7单击“Next”按钮后进入最后确认的对话框,如图1-8所示。

建立的工程的名称、选择的器件和选择的第三方工具等信息,如果无误的话就可以单击“Finish”按钮,弹出如图1-9所示的窗口,在资源管理窗口可以看到新建的工程名称half_add。

当工程建立好以后,我们就可以建立设计文件。

下面我们以一个半加器的VHDL的设计,来演示在QuartusII如何实现VHDL语言输入。

语言输入

(1)建立文件。

在图1-9中,单击“File”菜单下的“New”命令或者使用快捷键Ctrl+N,在弹出“New”对话框如图1-10所示。

在“DeviceDesignFiles”页面下双击“VHDLFile”选项(或选中该项后单击“OK”按钮)后建立新文件,如图1-11所示。

图1-11VHDL文本编辑窗口

(2)输入程序。

在图1-11中输入半加器的VHDL程序,如图1-12所示。

(3)保存文件。

在图1-12中单击保存文件按钮

,弹出对话框如图1-13,将输入的VHDL语言程序保存为文件,注意后缀名是.vhd,单击“保存”按钮即可保存文件,如图1-13。

(4)编译工程。

在图1-11中单击水平工具条上的编译按钮,或选择菜单Processing下的StartComplilation,开始编译,并伴随着进度不断地变化,编译完成后的窗口如图1-14所示。

如果编译过程出现错误,要将错误改正,保存后再次编译,直到编译无错误为止。

到此在QuartusII软件中使用VHDL语言输入完成,接下来是将保存好的VHDL语言程序进行仿真,在软件上验证VHDL语言描述的功能是否能够达到预期目的。

二、设计仿真

设计仿真的目的就是在软件环境下,验证电路的行为和思想是否一致。

仿真分为功能仿真和时序仿真。

功能仿真是在设计输入之后,综合和布局布线之前的仿真,不考虑电路的逻辑和门电路的时间延时,着重考虑电路在理想环境下的行为和预期设计效果的一致性。

时序仿真是在综合、布局布线后,也即电路已经映射到特定的工艺环境后,考虑器件延时的情况下对布局布线的网络表文件进行的一种仿真,其中器件延时信息通过反向标注时序延时信息实现的。

1.仿真文件的生成

(1)建立矢量波形文件。

在图1-14中,单击“File”菜单下的“New”命令,在弹出的“New”对话框中选择“OtherFiles”页面,如图1-15。

选择“VectorWaveformFile”后单击“OK”按钮,弹出如图1-16所示的矢量波形编辑窗口。

(2)添加引脚或节点。

在图1-16中,左键双击“Name”下方空白处,弹出“InsertNodeorBus”对话框,如图1-17所示。

单击对话框“NodeFinder…”按钮后,弹出“NodeFinder”对话框,如图1-18所示。

在图1-18中,在“Filter”后面的方框里选择“Pin:

all”,然后单击“List”按钮,在“NodeFound”栏中列出了设计中的所有的输入/输出引脚号,如图1-19所示。

单击图1-19中的

按钮,所有列出的输入/输出引脚号被复制到右边一侧。

也可以根据情况选择部分引脚号复制到右边,方法是在左边选中想要的引脚号,单击

按钮即可。

选择好了引脚号后,单击“OK”按钮,返回“InsertNodeorBus”对话框,此时,在“Name”和“Type”栏里出现了“MultipleItems”项,如图1-20。

单击“OK”按钮,选中的输入/输出引脚号都添加到矢量波形编辑窗口中,如图1-21所示,单击“OK”按钮,进入矢量波形编辑窗口,如图1-22。

(3)编辑输入信号并保存文件。

在图1-22中单击“Name”下方的“A”,即选中该行的波形。

在本例中将输入信号“A”设置为时钟信号,单击工具栏中的按钮,弹出“Clock”对话框,此时可以修改信号的周期、相位和占空比。

设置完后单击“OK”按钮,输入信号“A”设置完毕。

同理设置其他输入信号“B”,最后单击保存文件按钮,根据提示完成保存工作,如图1-23所示。

同时,为了方便读者熟悉其他波形编辑工具的使用,在图1-24中标注了其他波形编辑工具的功能。

2.功能仿真

功能仿真是忽略延时的仿真,是理想的仿真。

接下来我们一起来进行设计的功能仿真。

首先在图1-23中单击“Assignments”菜单下的“Settings”命令,如图1-25,单击左侧标题栏中的“Simulator”选项后,在右侧的“Simulationmode”的下拉菜单中选择“Functional”选项即可(软件默认的是“Timing”选项),单击“OK”按钮后完成设置。

后需要生成功能仿真网络表。

单击“Processing”菜单下的“GenerateFunctionalNetlist”命令后会自动创建功能仿真网络表,如图1-26所示。

完成后会弹出相应提示框,单击“确定”即可。

最后单击按钮进行功能仿真,如图1-27所示。

从图中可以看出仿真后的波形没有延时,半加器的两个加数作为输入信号,得到了对应的和与进位。

3.时序仿真

QuartusII中默认的仿真为时序仿真,在图1-23中直接单击仿真按钮即可。

如果做完功能仿真后进行时序仿真,需要在“Assignments”→“Settings”→“Simulator”选项后,在右侧的“Simulationmode”的下拉菜单中选择“Timing”选项即可。

仿真完成后的窗口如图1-28所示。

观察波形,可以知道输入输出之间有一定的延时。

三、引脚锁定

引脚锁定是为了对所设计的工程进行硬件测试,将输入/输出信号锁定在器件的某些引脚上。

单击“Assigments”菜单下的“Pins”命令,在弹出的对话框如图1-29所示,在下方的列表中列出了本项目所有的输入/输出引脚名。

在图1-29中,双击与输入端“A”对应的“Location”选项后弹出引脚列表,从中选择合适的引脚,则输入“A”的引脚锁定完毕。

同理完成其他引脚的锁定,如图1-30。

四、编程下载

编程下载是将本次设计所生成的文件通过计算机下载到实验箱里,来验证此次设计是否能够达到预期目的。

需要进行以下几个步骤:

1.编译

锁定引脚后必须再次编译,才能存储这些引脚锁定的信息,单击编译按钮执行编译。

2.配置下载电缆

在“Tools”菜单下选择“Programmer”命令,或者直接单击工具栏上的按钮,弹出如图1-31所示的页面。

单击“HardwareSetup”按钮,弹出“HardwareSetup”对话框,如图1-32所示。

单击“AddHardware”按钮设置下载电缆,弹出如图1-33所示的对话框。

在“Hardwaretype”一栏中选择“ByteBlasterMVorByteBlasterII”后单击“OK”按钮,下载电缆配置完成。

设置成如图1-34所示的选项后,单击“Close”按钮即可。

一般情况下,如果下载电缆不更换,一次配置就可以长期使用,不需要每次都设置。

3.下载模式

JTAG模式是软件的默认下载模式,相应的下载文件为“.sof”格式。

在“Mode”一栏中还可以选择其他的下载模式,例如,PassiveSerial、ActiveSerialProgramming和In-SocketProgramming。

勾选图1-31中下载文件“”右侧的第一个小方框,也可以根据需要勾选其他的小方框。

将下载电缆连接好后,单击“Start”按钮计算机就开始下载编程文件,这样在实验箱上就可以验证实验效果了。

到这里,我们都演示了QuartusII软件的全部使用过程,从建立工程,VHDL语言设计输入,设计仿真到编程下载都演示了一遍,读者跟着上面的操作,就能够到达最后的程序下载,在EDA实验箱上看到最终的效果。

五、原理图输入

在图1-9中,单击“File”菜单下的“New”命令或者使用快捷键Ctrl+N,在弹出“New”对话框如图1-35所示。

在“DeviceDesignFiles”页面下双击“BlockDiagram/SchematicFile”选项(或选中该项后单击“OK”按钮)后建立新文件,如图1-36所示。

(2)在图1-36中对常用的工具栏功能进行了标注,以帮助读者更好地使用这些工具。

在图1-36的图形编辑窗口的空白处双击鼠标左键(或在编辑工具栏单击工具条),弹出如图1-37所示的选择电路符号对话框,选中“primitives”→“logic”→“xor”(或在“Name”输入编辑框中输入“xor”)后,单击“OK”按钮。

此时,光标上与符号连在一起,可以移动光标,将符号移动到合适的位置,如图1-38。

同理,在图中放置一个“and2”符号,在“primitives”→“pin”下选择“input”和“output”两中符号,分别放两个,如图1-39所示。

(3)连接各元器件并命名。

在图1-39中,将光标移到input右侧,待变成十字形光标时,按下鼠标左键(或选中工具栏中的工具,光标自动会变成十字形的连线状态),再将光标移动到异或门的左侧,待连接点上出现蓝色的小方块后释放鼠标左键,即可看到input和异或门之间有一条连线生成。

重复上面的方法将1-39图中各种符号连接起来,如图1-40所示。

双击pin_name使其底色变为黑色后,输入A(或双击input,弹出“PinProperties”对话框,在“Pinname”一栏中填上名字A),将其他引脚使用同样的方法命名。

(4)保存文件。

在图1-40中单击保存文件按钮。

在弹出的对话框中的“文件名”下,输入原理图文件的名称“”,单击“保存”按钮即可保存文件,如图1-41所示。

(5)编译工程。

在图1-41中单击水平工具条上的编译按钮

,或选择菜单Processing下的StartComplilation,开始编译,并伴随着进度不断地变化,编译完成后的窗口如图1-42所示。

如果编译过程出现错误,要根据提示将错误改正,保存后再次编译,直到编译无错误为止。

到此在QuartusII软件中使用原理图输入设计完成,接下来是将绘制好的原理图设计进行仿真,以验证原理图设计是否能够达到预期目的。

仿真方法与VHDL语言文件的方法一样