直接数字频率合成器的设计与分析.docx

《直接数字频率合成器的设计与分析.docx》由会员分享,可在线阅读,更多相关《直接数字频率合成器的设计与分析.docx(23页珍藏版)》请在冰点文库上搜索。

直接数字频率合成器的设计与分析

成绩:

_______

直接数字频率合成器的设计与分析

学院:

电子与信息工程学院

专业:

电子信息科学与技术

班级:

09级电信本二班

姓名:

余金雷

学号:

指导老师:

过老师

时间:

2011年12月13日

1.摘要

随着数字信号处理和集成电路技术的发展,直接数字频率合成(DDS)的应用也越来越广泛。

DDS具有相位和频率分辨率高、稳定度好、频率转换时间短、输出相位连续、可以实现多种数字与模拟调制的优点,而可编程门阵列(FPGA)具有集成度高、通用性好、设计灵活、编程方便、可以实现芯片的动态重构等特点,因此可以快速地完成复杂的数字系统。

由于模拟调相方法有生产性差、调试不方便、调制度控制不精确等缺点,因此采用数字方法实现各种模拟调制也越来越普遍[5]。

现在许多DDS芯片都直接提供了实现多种数字调制的功能,实现起来比较简单,而要实现模拟线性调制具有一定的难度。

因此本设计介绍了一种由单片机控制,并采用FPGA实现DDS功能,产生频率和相位可调的正弦波信号的方法。

与传统的频率合成方法相比,DDS合成信号具有频率切换时间短、频率分辨率高、相位变化连续等诸多优点。

使用单片机灵活的控制能力与FPGA器件的高性能、高集成度相结合,可以克服传统DDS设计中的不足,从而设计开发出性能优良的DDS系统。

直接数字频率合成(DigitalFrequencySynthesis)是一种新的频率合成方法。

随着数字集成电路和微电子技术的发展,DDS技术日益显示出他的优越性。

直接数字频率合成器是一种全数字化的频率合成器。

它由相位累加器、波形存储器、数模转化器和低通滤波器组成。

DDS具有频率分辨率高、频率切换速度快、频率切换是相位变化连续等优点。

本文首先对DDS的原理进行了详细讨论,然后结合现场可编程门阵列器件(FPGA),设计实现了基于FPGA的DDS正弦信号的实现。

本设计采用了用VHDL硬件描述语言和maxplus的顶层原理图等多种方式来实现,并经实践证明是可行的。

关键字EDA技术VHDL硬件描述语言直接数字频率合成器

软件平台MAX+PLUSⅡ

前言

EDA技术是现代电子信息工程领域的一门新技术,它是以大规模可编程逻辑器件为设计载体,一硬件描述语言为系统逻辑描述的主要表达方式,以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具,通过有关的开发软件,自动完成用软件方式设计的电子系统到硬件系统的逻辑编译、逻辑简化、逻辑分割、逻辑综合及优化、逻辑局部布线、逻辑仿真,直至对于待定目标芯片的适配编译、逻辑放映、编程下载等工作,最终形成集成电子系统或专用集成芯片的一门新技术。

它具有用软件方式设计硬件,用软件方式设计的系统到硬件系统的转换是由有关开发软件自动完成的,设计过程中用有关软件进行仿真,系统可现场编程、在线升级,整个系统可集成在一个芯片上,体积小、功耗低、可靠性高的特点。

其主要主要内容:

①大规模可编程逻辑器件②硬件描述语VHDL③软件开发工具④实验开发系统。

它是在先进的计算机工作平台上开发出来的一整套电子系统设计的软硬件工具并提供了先进的电子系统设计方法。

当今的EDA技术更多的是指芯片内的电子系统设计自动化,即片上系统(SOC)设计。

也就是说,开发人员完全可以通过自己的电子系统设计来制定其芯片内部的电路功能,使之成为设计者自己的专用集成电路(ASIC)芯片,可以将设计过程中的许多细节问题抛开,而将注意力集中在系统的总体开发上,实现了真正意义上的电子设计自动化。

随着数字信号处理和集成电路技术的发展,直接数字频率合成(DDS)的应用也越来越广泛。

DDS具有相位和频率分辨率高、稳定度好、频率转换时间短、输出相位连续、可以实现多种数字与模拟调制的优点,而可编程门阵列(FPGA)具有集成度高、通用性好、设计灵活、编程方便、可以实现芯片的动态重构等特点,因此可以快速地完成复杂的数字系统。

由于模拟调相方法有生产性差、调试不方便、调制度控制不精确等缺点,因此采用数字方法实现各种模拟调制也越来越普遍[5]。

现在许多DDS芯片都直接提供了实现多种数字调制的功能,实现起来比较简单,而要实现模拟线性调制具有一定的难度。

因此本设计介绍了一种由单片机控制,并采用FPGA实现DDS功能,产生频率和相位可调的正弦波信号的方法。

DDS技术具有频率切换时间短(<20ns),频率分辨率高(0.01Hz),频率稳定度高,输出信号的频率和相位可以快速程控切换,输出相位可连续,可编程以及灵活性大等优点,它以有别于其他频率合成方法的优越性能和特点成为现代频率合成技术中的姣姣者。

DDS广泛用于接受机本振、信号发生器、仪器、通信系统、雷达系统等,尤其适合跳频无线通信系统。

利用EDA技术中VHDL硬件描述语言,对直接数字频率合成器描述,并在Altera公司开发的EDA软件平台MAX+PLUSⅡ环境下,对VHDL源程序进行编辑、编译、仿真。

2.设计基本要求

1971年,美国学者J.Tierncy、,一种新的频率合成技术——直接数字频率合成(DDS,DirectDigtalSynthesis)技术得到了飞速发展。

DDS技术是一种把一系列数字形式的信号通过DAC转换成模拟形式的信号合成技术,目前使用最广泛的一种DDS方式是利用高速存储器作查找表,然后通过高速DAC输出已经用数字形式存入的正弦波。

DDS技术具有频率切换时间短(<20ns),频率分辨率高(0.01Hz),频率稳定度高,输出信号的频率和相位可以快速程控切换,输出相位可连续,可编程以及灵活性大等优点,它以有别于其他频率合成方法的优越性能和特点成为现代频率合成技术中的姣姣者。

DDS广泛用于接受机本振、信号发生器、仪器、通信系统、雷达系统等,尤其适合跳频无线通信系统。

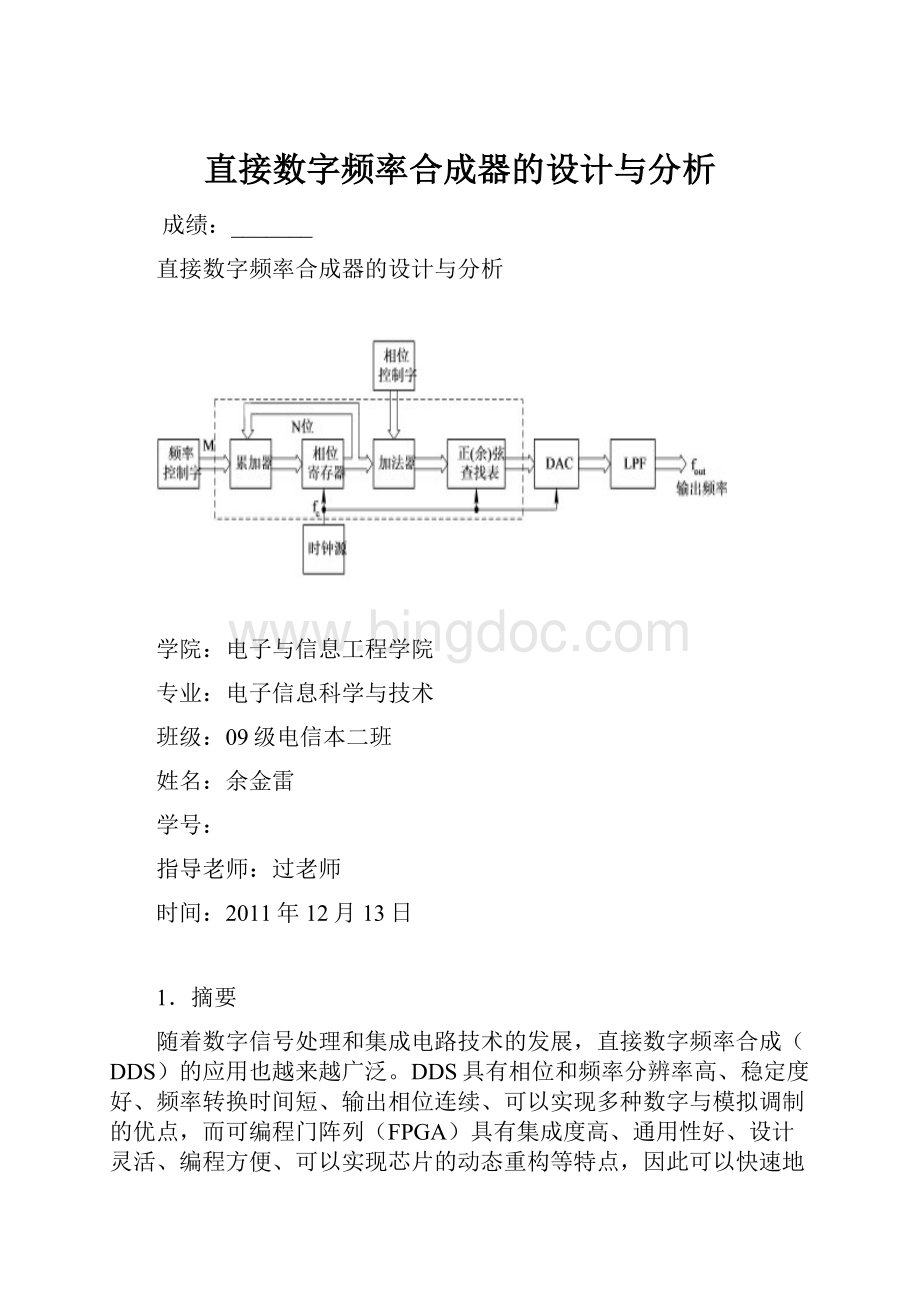

信号发生器由单片机、接口电路、FPGA、低通滤波器、D/A转换等部分组成其组成框图如图2.1所示。

通过键盘送人频率控制字、相位控制字和幅值控制字,使其输出一定频率、相位和幅值的正弦波信号,经过低通滤波器后形成平滑的正弦波。

图2.1信号发生器的组成框图

系统的性能要求:

1、频率范围20Hz~20KHZ,步进20Hz;

2、差0°~359°,步进1°;

3、两路输出正弦波信号,峰峰值分别在0.3V~5V变化;

4、数字显示频率、相位差。

3.设计分析

3.1DDS的工作原理:

下图是DDS的基本原理图,频率控制字M和相位控制字分别控制DDS输出正(余)弦波的频率和相位。

DDS系统的核心是相位累加器,它由一个累加器和一个N位相位寄存器组成。

每来一个时钟脉冲,相位寄存器以步长M增加。

图3.1

相位累加器由N位加法器与N位累加寄存器级联构成,其原理框图如图3.1所示。

每来一个时钟脉冲Fc,N位加法器将频率控制数据K与累加寄存器输出的累加相位数据相加,把相加后的结果Y送至累加寄存器的输入端。

累加寄存器一方面将在上一时钟周期作用后所产生的新的相位数据反馈到加法器的输入端,以使加法器在下一时钟的作用下继续与频率控制数据K相加;另一方面以相加后的结果形成正弦查询表的地址,取出表中与该相位对应的单元中的幅度量化正弦函数值,作为取样地址值送入幅度/相位转换电路(即图2.1中的波形存储器)。

这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换。

波形存储器的输出送到D/A转换器,D/A转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。

相位累加器原理框图

由此可以看出,相位累加器在每一个时钟脉冲输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位。

当相位累加器加满量时就会产生一次溢出,溢出频率就是DDS输出的信号频率。

相位累加器的最大计数长度与正弦查询表中所存储的相位分隔点数相同,在取样频率(由参考时钟频率决定)不变的情况下,由于相位累加器的相位增量不同,将导致一周期内的取样点数不同,输出信号的频率也相应变化。

如果设定累加器的初始相位,则可以对输出信号进行相位控制。

由采样原理可知,如果使用两个相同的频率合成器,并使其参考时钟相同,同时设定相同的频率控制字、不同的初始相位,那么在原理上就可以实现输出两路具有一定相位差的同频信号。

3.2EDA实现的直接数字频率合成器

本设计基于DDS的基本原理,利用Altera公司的FPGA芯片FLEX10系列器件设法将波形采样点的值依次通过数模转换器(MDAC)转换成模拟量输出,可达到预期的目的,具有较高的性价比。

其基本环节由计数器(Counter)、只读存储器(EPROM)、数模转换器(MDAC)和滤波器等组成(同DDS原理)。

具体方案如下:

累加器由加法器和D触发器级联组成。

在时钟脉冲fc的控制下,对输入频率控制字K进行累加,累加满量时产生溢出。

相位累加器的输出对应于该合成周期信号的相位,并且这个相位是周期性的,在0~2

范围内起变化。

相位累加器位数为N,最大输出为2

-1,对应于2

的相位,累加一次就输出一个相应的相位码,通过查表得到正弦信号的幅度,然后经D/A转换及低通滤波器滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。

整个DDS电路的电路结构如下图所示。

3.3移相原理

所谓移相是指两路同频的信号,以其中的一路为参考,另一路相对于该参考作超前或滞后的移动,即称为相位的移动。

两路信号的相位不同,便存在相位差,简称相差。

若我们将一个信号周期看作是360°,则相差的范围就在0°~360°之间。

移相示意图

若输出信号A和B的相位差可调,须保证两路信号同步,故应满足以下条件:

(1)输入到两个频率合成器芯片的参考时钟之间的相位偏移要足够小。

这个相移会导致输出信号之间产生与之成比例的相移。

(2)频率控制字送到频率合成器的数据缓冲区后,还必须通过一个更新时钟才能将数据缓冲区中的数据送到相位累加器,成为有效数据后进行输出。

(3)在第一次传送数据之前必须先使频率合成器复位,以保证其输出的相位是可知的。

因为DDS芯片的相位输出是连续的,所示复位信号可使两个频率合成器的相位累加器复位到COS(0)状态。

新的数据送到相位累加器时,它们之间的相位关系可以得到保持,也可以通过相位控制字来调节两片频率合成器之间的相位差。

因为要求产生两路正弦波,频率和相位可调,且都要以数字的形式进行控制和处理,所以在设计中将分别对部分电路提出几种实现方案并进行分析和论证。

3.4频率合成器方案

频率合成是指对一个标准信号频率经过一系列算术运算,产生具有相同精度和稳定度的大量离散频率的技术。

频率合成有多种实现方法,其中直接数字频率合成技术与传统频率合成技术相比具有难以比拟的优点,如频率切换速度快、分辨率高、频率和相位易于控制等。

因此得到越来越广泛的应用,成为当今现代电子系统及设备中频率源设计的首选。

实现DDS有三种技术方案:

(1)采用高性能DDS单片电路的解决方案:

(2)采用低频正弦波DDS单片电路的解决方案:

(3)自行设计的基于FPGA芯片的解决方案[EDA]:

相位累加器SUM99是决定DDS性能的一个要害部分,小的累加器可以利用ACEX器件的进位链得到快速、高效的电路结构。

然而,由于长的进位链会减少其它逻辑使用的布线资源,同时过长的进位链也会制约整个系统速度的提高。

采用流水线技术可以提高速度,即把在一个时钟内要完成的逻辑操作分成几步较小的操作,并插入几个时钟周期来提高系统的数据吞吐率。

综合考虑后,这一部分决定采用进位链和流水线技术相结合的办法,这样既能保证较高的资源利用率,又能大幅提高系统的性能和速度。

相位/幅度转换电路A/D是DDS电路中另一个要害,设计中面临的主要问题就是资源的开销。

电路通常采用ROM结构,相位累加器的输出是一种数字式锯齿波,通过取它的高若干位作为ROM的地址输入,经查表和运算后,ROM就输出所需波形的量化数据。

正弦查找表ROM的设计中利用MATLAB或C语言编程对正弦函数进行采样,非常方便地得到了正弦函数的采样数据。

在本设计的硬件验证过程中,针对实验开发系统所提供的输入、输出资源的限制及芯片逻辑资源的限制,便于实验的实现,所以采用自行设计的基于FPGA芯片的解决方案能更易实得到实验结果

ROM表的尺寸随着地址位数或数据位数的增加呈指数递增关系,因此,在满足信号性能的前提条件下,如何减少资源的开销就是一个重要问题,实际设计时,我们充分利用了信号周期内的对称性和算术关系来减少EAB的开销。

在实际运用中,我们将着眼点主要放在了节省资源上。

相位/幅度转换电路中的主要问题在于ROM的大小上。

本次设计的DDS主要用于数字视频编码中,因此只需要输出正弦波,考虑了以下的优化方式:

COS波信号对于x=π直线成偶对称,基于此可以将ROM表减至原来的1/2,再利用左半周期内,波形对于点(π/2,0)成奇对称,进一步将ROM表减至最初的1/4,因此,通过一个SIN码表的前1/4周期就可以变换得到SIN和COS的整个周期码表。

这样,就节省了将近3/4的资源。

系统控制电路主要是根据是否需要相位调制(BPSK)及频率调制(BFSK),系统时钟是否需要分频得到所需的基准时钟,频率码的输入方式是串行、并行还是微机接口方式,如何控制输出等具体要求而设计的。

3.5移相方案

要实现两路信号具有确定的相位差,采用数字移相技术,这是目前移相技术的潮流。

数字移相技术的核心是先将模拟信号数字化,移相后再还原成模拟信号。

数字移相主要有两种形式:

一种是先将正弦波信号数字化,并形成一张数据表存入ROM芯片中,此后可通过两片D/A转换芯片在单片机的控制下连续地循环输出该数据表,就可获得两路正弦波信号,当两片D/A转换芯片所获得的数据序列不同时,则转换所得到的两路正弦波信号就存在着相位差。

相位差的值与数据表中数据的总个数及数据地址的偏移量有关。

这种处理方式的实质是将数据地址的偏移量映射为信号间的相位值。

另一种是先将参考信号整形为方波信号,并以此信号为基准,延时产生另一个同频的方波信号,再通过波形变换电路将方波信号还原成正弦波信号。

以延时的长短来决定两信号间的相位值。

这种处理方式的实质是将延时的时间映射为信号间的相位值。

3.6DDS的FPGA实现设计

根据图3.1,并假定相位控制字为0,这时DDS的核心部分相位累加器的FPGA的设计可分为如下几个模块:

相位累加器SUM99、相位寄存器REG1、正弦查找表ROM和输出数据寄存器REG2,其内部组成框图如图3.2所示。

图中,输入信号有时钟输入CLK,使能端EN,复位端RESET,频率控制字K,输出信号为Q。

图3.2

首先利用MATLAB或C语言编程对正弦函数进行采样;然后对采样数据进行二进制转换,其结果作为查找表地址的数值。

用MATLAB语言编写的正弦函数数据采集程序如下:

CLEARTIC;

T=2*PI/1024;

t=[0:

T:

2*pi];

y=255*sin(t);

round(y);

用C语言编写的正弦函数数据采样程序如下:

#include"stdio.h"

#include"math.h"

Main()

{intI;

Floats;

For(i=0;i<1024;i++)

{s=sin(actan

(1)*8*i/1024);

Printf("%d,%d;\n",(int)((s+1)*1023/2));

}

}

两个程序运行之后所得结果是一致的。

4.VHDL源程序以及编译、波形仿真图

4.1相位累加器SUM99的VHDL源程序

--SUM99.VHD

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYSUM99IS

PORT(K:

INSTD_LOGIC_VECTOR(9DOWNTO0);

CLK:

INSTD_LOGIC;

EN:

INSTD_LOGIC;

RESET:

INSTD_LOGIC;

OUT1:

OUTSTD_LOGIC_VECTOR(9DOWNTO0));

ENDENTITYSUM99;

ARCHITECTUREARTOFSUM99IS

SIGNALTEMP:

STD_LOGIC_VECTOR(9DOWNTO0);

BEGIN

PROCESS(CLK,EN,RESET)IS

BEGIN

IFRESET='1'THEN

TEMP<="0000000000";

ELSE

IFCLK'EVENTANDCLK='1'THEN

IFEN='1'THEN

TEMP<=TEMP+K;

ENDIF;

ENDIF;

ENDIF;

OUT1<=TEMP;

ENDPROCESS;

ENDARCHITECTUREART;

相位累加器SUM99编译图

相位累加器SUM99波形仿真图

4.2正弦查找表ROM的VHDL源程序

--ROM.VHD

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYROMIS

PORT(ADDR:

INSTD_LOGIC_VECTOR(9DOWNTO0);

CLK:

INSTD_LOGIC;

OUTP:

OUTSIGNED(8DOWNTO0));

ENDENTITYROM;

ARCHITECTUREARTOFROMIS

BEGIN

PROCESS(CLK)IS

BEGIN

IF(CLK'EVENTANDCLK='1')THEN

CASEADDRIS

WHEN"0000000000"=>OUTP<="000000000";

WHEN"0000000001"=>OUTP<="000000010";

WHEN"0000000010"=>OUTP<="000000011";

WHEN"0000000011"=>OUTP<="000000101";

WHEN"0000000100"=>OUTP<="000000110";

WHEN"0000000101"=>OUTP<="000001000";

WHEN"0000000110"=>OUTP<="000001001";

WHEN"0000000111"=>OUTP<="000001011";

WHEN"0000001000"=>OUTP<="000001101";

WHEN"0000001001"=>OUTP<="000001110";

WHEN"0000001010"=>OUTP<="000010000";

WHEN"01"=>OUTP<="0";

WHEN"10"=>OUTP<="0";

WHEN"11"=>OUTP<="1";

WHEN"00"=>OUTP<="1";

WHEN"01"=>OUTP<="0";

WHEN"10"=>OUTP<="0";

WHEN"11"=>OUTP<="1";

WHEN"00"=>OUTP<="1";

WHEN"01"=>OUTP<="1";

WHEN"10"=>OUTP<="0";

WHEN"11"=>OUTP<="0";

WHEN"00"=>OUTP<="1";

WHEN"01"=>OUTP<="1";

WHEN"10"=>OUTP<="0";

WHEN"11"=>OUTP<="0";

WHEN"00"=>OUTP<="1";

WHEN"01"=>OUTP<="1";

WHEN"10"=>OUTP<="1";

WHEN"11"=>OUTP<="0";

WHEN"00"=>OUTP<="1";

WHEN"01"=>OUTP<="1";

WHEN"10"=>OUTP<="0";

WHEN"11"=>OUTP<="000000000";

WHENOTHERS=>OUTP<="000000000";

ENDCASE;

ENDIF;

ENDPROCESS;

ENDARCHITECTUREART;

正弦查找表ROM编译图

正弦查找表ROM仿真图

4.3相位寄存器REG1的VHDL源程序

--REG1.VHD

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYREG1IS

PORT(D:

INSTD_LOGIC_VECTOR(9DOWNTO0);

CLK:

INSTD_LOGIC;

Q:

OUTSTD_LOGIC_VECTOR(9DOWNTO0));

ENDENTITYREG1

ARCHITECTUREARTOFREG1IS

BEGIN

PROCESS(CLK)IS

BEGIN

IF(CLK'EVENTANDCLK='1')THEN

Q<=D;

ENDIF;

ENDPROCESS;

ENDARCHITECTUREART;

相位寄存器REG1的编译图

相位寄存器REG1的仿真图

4.4相位寄存器REG1的VHDL源程序

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYREG2IS

PORT(D:

INSTD_LOGIC_VECTOR(8DOWNTO0);

CLK:

INSTD_LOGIC;

Q:

OUTSTD_LOGIC_VECTOR(8DOWNTO0));

ENDENTITYREG2;

ARCHITECTUREARTOFREG2IS

BEGIN

PROCESS(CLK)IS

BEGIN

IF(CLK'EVENTANDCLK='1')THEN

Q<=D;

ENDIF;

ENDPROCESS;

ENDARCHITECTUREART;

相位寄存器REG2的编译图

相位寄存器REG1的仿真图

4.5系统的整体组装DDS的VHDL源程序

--DDS.VHD

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYDDSIS

PORT(K:

INSTD_LOGIC_VECTOR(9DOWNTO0);

EN:

INSTD_LOGIC;

RESET:

INSTD_LOGIC;

CLK:

INSTD_LOGIC;

Q:

OUTSTD_LOGIC_VECTOR(8DOWNTO0));

ENDENTITYDDS;

ARCHITECTUREARTOFDDSIS

COMPONENTSUM99IS

PORT(K:

INSTD_LOGIC_VECTOR(9DOWNTO0);

EN:

INSTD_LOGIC;

RESET:

INSTD_LOGIC;

CLK:

INSTD_LOGIC;

OUT1:

OUTSTD_LOGIC_VECTOR(9DOWNTO0));

ENDCOMPONENTSUM99;

COMPONENTREG1IS

PORT(D:

INSTD_LOGIC_