基于VHDL语言实现数字电子钟的设计说明.docx

《基于VHDL语言实现数字电子钟的设计说明.docx》由会员分享,可在线阅读,更多相关《基于VHDL语言实现数字电子钟的设计说明.docx(17页珍藏版)》请在冰点文库上搜索。

基于VHDL语言实现数字电子钟的设计说明

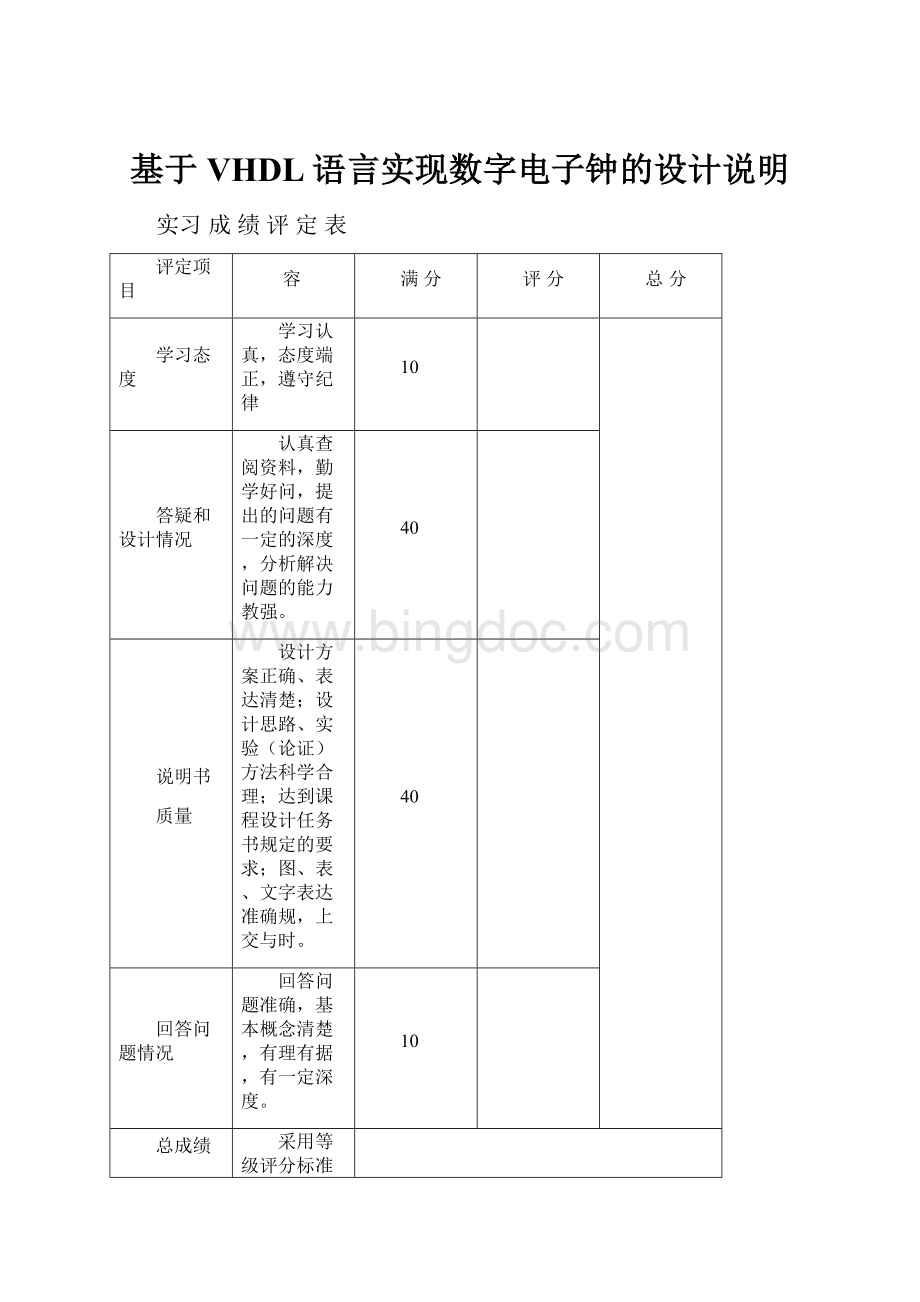

实习成绩评定表

评定项目

容

满分

评分

总分

学习态度

学习认真,态度端正,遵守纪律

10

答疑和设计情况

认真查阅资料,勤学好问,提出的问题有一定的深度,分析解决问题的能力教强。

40

说明书

质量

设计方案正确、表达清楚;设计思路、实验(论证)方法科学合理;达到课程设计任务书规定的要求;图、表、文字表达准确规,上交与时。

40

回答问题情况

回答问题准确,基本概念清楚,有理有据,有一定深度。

10

总成绩

采用等级评分标准,分为优、良、中、与格、不与格五个等级。

指导教师评语:

签名:

年月日

基于VHDL语言实现数字电子钟的设计

[摘要]:

VHDL的英文全名是Very-High-SpeedIntegratedCircuitHardwareDescriptionLanguage,诞生于1982年。

1987年底,VHDL被IEEE和美国国防部确认为标准硬件描述语言。

自IEEE公布了VHDL的标准版本,IEEE-1076(简称87版)之后,各EDA公司相继推出了自己的VHDL设计环境,或宣布自己的设计工具可以和VHDL接口。

此后VHDL在电子设计领域得到了广泛的接受,并逐步取代了原有的非标准的硬件描述语言。

随着基于PLD的EDA技术的发展和应用领域的扩大与深入,EDA技术在电子信息、通信、自动控制与计算机应用等领域的重要性日益突出。

本文详细介绍EDA课程设计任务——数字钟的设计的详细设计过程与结果,并总结出心得体会。

[关键字]:

EDA技术;VHDL语言;数字钟

EDA技术作为现代电子设计技术的核心,它依赖强大的计算机,在EDA工具软件平台上,对以硬件描述语言HDL为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、逻辑简化、逻辑分割、逻辑综合,以与逻辑优化和仿真测试,直至实现既定的电子线路系统功能。

[笔者详细介绍在QUARTUSII软件环境下开发基于VHDL语言数字钟的设计。

一.设计要求:

1、设计容

选用合适的可编程逻辑器件与外围电子元器件,设计一个数字电子钟,利用EDA软件(QUARTUSⅡ)进行编译与仿真,设计输入可采用VHDL硬件描述语言输入法)和原理图输入法,并下载到EDA实验开发系统,连接外围电路,完成实际测试。

2、设计要求

(1)具有时、分、秒计数显示功能。

(2)具有清零的功能,且能够对计时系统的小时、分钟进行调整。

(3)小时为十二小时制。

二.实验目的:

1.通过这次EDA设计中,提高手动能力。

2.深入了解时事时钟的工作原理,以与时事时钟外围硬件设备的组成。

3.掌握多位计数器相连的设计方法。

4.掌握十进制,六进制,二十四进制计数器的设计方法。

5.继续巩固多位共阴极扫描显示数码管的驱动,与编码。

6.掌握扬声器的驱动。

7.LED灯的花样显示。

8.掌握CPLD技术的层次化设计方法

三.实验方案:

数字系统的设计采用自顶向下、由粗到细,逐步分解的设计方法,最顶层电路是指系统的整体要求,最下层是具体的逻辑电路的实现。

自顶向下的设计方法将一个复杂的系统逐渐分解成若干功能模块,从而进行设计描述,并且应用EDA软件平台自动完成各功能模块的逻辑综合与优化,门级电路的布局,再下载到硬件中实现设计。

因此对于数字钟来说首先是时分秒的计数功能,然后能显示,附带功能是清零、调整时分。

通过参考EDA课程设计指导书,现有以下方案:

1.作为顶层文件有输入端口:

时钟信号,清零按键,调时按键,调分按键;输出端口有:

用于接数码管的八段码输出口,扫描用于显示的六个数码管的输出口。

2.底层文件分为:

(1)时间计数模块。

分秒计数模块计数为60计数,时计数模块为12计数。

(2)显示模块。

显示模块由一个六进制计数器模块和一个七段译码器组成。

进制计数器为六选一选择器的选择判断端提供输入信号,六选一选择器的选择输出端分别接秒个位、秒十位、分个位、分十位和时个位、时十位的选通位用来完成动态扫描显示,同时依次输出秒个位、秒十位、分个位、分十位和时个位、时十位数向给译码模块。

(3)报警模块当时间到整点时就报时。

输入有时分秒计数,时钟脉冲。

(4)采用点阵式数码管显示,点阵式数码管是由八行八列的发光二极管组成,对于显示文字比较适合,如采用在显示数字显得太浪费,且价格也相对较高,所以不用此种作为显示.采用LED数码管动态扫描,LED数码管价格适中,对于显示数字最合适,但无法显示图形文字,在显示星期是也只能用数字表示,而且采用动态扫描法与单片机连接时,在编程时比较复杂。

所以也不采用了LED数码管作为显示。

采用LCD液晶显示屏,液晶显示屏的显示功能强大,可显示文字,图形,显示多样,清晰可见,所以在此设计中采用LCD液晶显示屏。

四.实验原理:

1.实验主控系统原理图:

2.模块化设计原理图:

以上为方案原理图,秒计数、分计数模块为60计数,计满后分别产生分脉冲、时脉,用于分计数、时计数。

各计数器同时将计数值送报时模块和送数与六选一选择器模块。

送数与六选一选择器模块依次将秒分时数送往译码模块译码,同时产生扫描信号用于数码管扫描显示。

整点报警在整点时刻将秒脉冲信号送扬声器声音报警。

(1)秒计数模块:

Second模块为秒计数模块。

Clk作为秒脉冲,reset复位,setmin用于调整分钟,接按键,enmin是当秒计数记到59后产生分脉冲,秒计数重新从0开始计数。

Daout为秒计数。

(2)分计数模块:

分计数为分计数模块。

Clk作为分脉冲,接second模块的enmin,reset用于复位,sethour用于调整小时,接按键,enhour是当分计数记到59后产生时脉冲,分计数重新从0开始计数。

Daout为分计数。

(3)时计数模块:

时计数为时计数模块,clk为时脉冲,接minute模块的enhour,reset复位,daout为时计数。

五.硬件要求:

在同一EPLD芯片EPF10K10上集成了如下电路模块:

1.时钟计数:

秒——60进制BCD码计数;

分——60进制BCDD码计数;

时——24进制BCDD码计数;

同时整个计数器有清零,调分,调时功能。

在接近整数时间能提供报时信号。

2.具有驱动8位八段共阴扫描数码管的片选驱动信号输出和八段字形译码输出。

编码和扫描可参照“实验四”。

3.扬生器在整点时有报时驱动信号产生。

六.实验源程序与流程图:

1.实验源程序(VHDL)

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_arith.all;

useieee.std_logic_unsigned.all;

------------------------------------------------------------------------------------------------------------

entitydaclkis

port(Clk:

instd_logic;--时钟输入

Rst:

instd_logic;--复位输入

S1,S2:

instd_logic;--时间调节输入

SPK:

outstd_logic;--扬声器输出

Display:

outstd_logic_vector(7downto0);--八段码管显示输出

SEG_SEL:

bufferstd_logic_vector(2downto0);--八段码管扫描驱动

lam:

outstd_logic_vector(2downto0));

enddaclk;

---------------------------------------------------------------------------------------------------------

architecturebehaveofdaclkis

signalDisp_Temp:

integerrange0to15;

signalDisp_Decode:

std_logic_vector(7downto0);

signalSEC1,SEC10:

integerrange0to9;

signalMIN1,MIN10:

integerrange0to9;

signalHOUR1,HOUR10:

integerrange0to9;

signalClk_Count1:

std_logic_vector(13downto0);

signalClk1Hz:

std_logic;

signalMusic_Count:

std_logic_vector(2downto0);

signalcount:

std_logic_vector(1downto0);

signallamp:

std_logic_vector(2downto0);

begin

process(Clk)--产生1Hz时钟的分频计数器

begin

if(Clk'eventandClk='1')then

if(Clk_Count1<10000)then

Clk_Count1<=Clk_Count1+1;

else

Clk_Count1<="001";

endif;

endif;

endprocess;

Clk1Hz<=Clk_Count1(13);

process(Clk1Hz,Rst)

begin

if(Rst='0')then--系统复位

SEC1<=0;

SEC10<=0;

MIN1<=0;

MIN10<=0;

HOUR1<=0;

HOUR10<=0;

elsif(Clk1Hz'eventandClk1Hz='1')then

if(S1='0')then--调节小时

if(HOUR1=9)then

HOUR1<=0;

HOUR10<=HOUR10+1;

elsif(HOUR10=2andHOUR1=3)then

HOUR1<=0;

HOUR10<=0;

else

HOUR1<=HOUR1+1;

endif;

elsif(S2='0')then--调节分钟

if(MIN1=9)then

MIN1<=0;

if(MIN10=5)then

MIN10<=0;

else

MIN10<=MIN10+1;

endif;

else

MIN1<=MIN1+1;

endif;

elsif(SEC1=9)then

SEC1<=0;

if(SEC10=5)then

SEC10<=0;

if(MIN1=9)then

MIN1<=0;

if(MIN10=5)then

MIN10<=0;

if(HOUR1=9)then

HOUR1<=0;

HOUR10<=HOUR10+1;

elsif(HOUR10=2andHOUR1=3)then

HOUR1<=0;

HOUR10<=0;

else

HOUR1<=HOUR1+1;

endif;

else

MIN10<=MIN10+1;

endif;

else

MIN1<=MIN1+1;

endif;

else

SEC10<=SEC10+1;

endif;

else

SEC1<=SEC1+1;

endif;

endif;

endprocess;

process(Clk)--整点报时

begin

if(Clk'eventandClk='1')then

Music_Count<=Music_Count+1;

if(MIN10=5andMIN1=9andSEC10=5)then

if((SEC1MOD2)=0)then

SPK<=Music_Count

(2);

else

SPK<='0';

endif;

elsif(MIN10=0andMIN1=0andSEC10=0andSEC1=0)then

SPK<=Music_Count

(1);

else

SPK<='0';

endif;

endif;

endprocess;

process(clk1Hz)--LED灯

begin

lam<=lamp;

if(rising_edge(clk1Hz))then

count<=count+1;

if(count<="10")then

if(count="00")then

lamp<="001";

elsif(count="01")then

lamp<="010";

elsif(count="10")then

lamp<="100";

endif;

else

count<="00";

endif;

endif;

endprocess;

process(SEG_SEL)--显示排序

begin

case(SEG_SEL+1)is

when"111"=>Disp_Temp<=HOUR10;

when"110"=>Disp_Temp<=HOUR1;

when"101"=>Disp_Temp<=10;

when"100"=>Disp_Temp<=MIN10;

when"011"=>Disp_Temp<=MIN1;

when"010"=>Disp_Temp<=10;

when"001"=>Disp_Temp<=SEC10;

when"000"=>Disp_Temp<=SEC1;

endcase;

endprocess;

process(Clk)--扫描累加

begin

if(Clk'eventandClk='1')then

SEG_SEL<=SEG_SEL+1;

Display<=Disp_Decode;

endif;

endprocess;

process(Disp_Temp)--显示转换

begin

caseDisp_Tempis

when0=>Disp_Decode<="00111111";

when1=>Disp_Decode<="00000110";

when2=>Disp_Decode<="01011011";

when3=>Disp_Decode<="01001111";

when4=>Disp_Decode<="01100110";

when5=>Disp_Decode<="01101101";

when6=>Disp_Decode<="01111101";

when7=>Disp_Decode<="00000111";

when8=>Disp_Decode<="01111111";

when9=>Disp_Decode<="01101111";

when10=>Disp_Decode<="01000000";

whenothers=>Disp_Decode<="00000000";

endcase;

endprocess;

endbehave;

2.实验流程图:

七.系统的仿真调试;

1.秒计数模块仿真:

2.分计数模块仿真:

3.时计数模块仿真:

4.系统硬件测试:

本次选用cyclone系列EP1C3T144C8芯片。

外部需接2个不同频率的时钟信与几上升沿按键,并接扬声器和不许译码器的数码管。

以上均由EDA试验箱提供。

整个系统的构成的入端口有:

clk1——用于送数与六选一选择器和整点报警的时序脉冲;

Stop——用于整点报时的停止控制;

clk——作为秒脉冲和整点报警的信声音号;

reset——用于各个模块复位;

setmin——调整分钟,接按键;

sethour——调整小时,接按键;

输出端口:

speak——接扬声器,用于报时;

led——接数码管,送字型码;

dp——接数码管的小数点为,隔开时分秒位;

sel——位选扫描信号输出口,接数码管位选接口

下载测试后的效果如下图所示,按复位键后数码管显示0时0分0秒开始计数,分秒时计数都正确。

按动调分键或调小时键后,分位或小时位开始自加,再按键后停止。

当时间到整点时会有十秒报时,按动停止键停止报时,不按此键时自动到十秒后停止报时。

设计结果达到要求。

八.EDA设计心得:

从这次EDA设计中,可以看我们的动手能力还有待提高。

另一方面,我们更加对EDA从实践上更有深刻认识。

从实践中发现问题,分析问题,解决问题在这次设计中很大的体现出来,提高了我们的能力和自信。

同时,成功与团队合作十分不开的。

结束语:

通过此次课程设计,让我对EDA这门技术有了更深的体会,并更好的学会了使用QuartusⅡ软件进行硬件设计。

此次课程设计时基于VHDL语言进行的数字钟设计,在课程设计时,我逐渐掌握了VHDL语言的语句与语法等的使用。

但在学习过程中,也遇到了很多困难,由于刚刚学习EDA不久,所以很多细节容都不是很了解,尤其时VHDL语言的运用。

我先上网找了一些资料和程序,一点点的看,慢慢摸索着学习写语句。

最后在老师和同学的帮助下,终于完成了数字钟的设计。

以后我会利用更多时间来学习EDA技术。

EDA技术有着非常好的发展前景,是进几年电子工业的发展趋向,中国的EDA行业发展十分迅速,有着很大的潜力。

参考文献

[1]国丽,朱维勇.电子技术实验指导书.:

中国科技大学,2000

[2]松,黄继业.EDA技术实用教程.:

科学,2002

[3]家龙,王小海,章安元.集成电子技术基础教程.:

高等教育,2002

[4]宋万杰,罗丰,吴顺君.CPLD技术与其应用.:

电子科技大学,1999

[5]卢杰,赖毅.VHDL与数字电路设计.:

科学,2001

[6]王金明,吉斌.数字系统设计与VerilogHDL.:

电子工业,2002