实验六 BCD七段显示译码器的设计.docx

《实验六 BCD七段显示译码器的设计.docx》由会员分享,可在线阅读,更多相关《实验六 BCD七段显示译码器的设计.docx(13页珍藏版)》请在冰点文库上搜索。

实验六BCD七段显示译码器的设计

浙江大学城市学院 实验报告纸

实验名称 实验六BCD七段显示译码器的设计

指导老师熊凯 成绩___________

专业 自动化 班级0901

姓名高谦一 学号 30902382

一.实验目的

(1)学习利用VHDL语言设计BCD七段显示译码器的方法,掌握BCD七段显示译码器的设计思路;

(2)掌握软件工具的使用方法。

二.实验原理

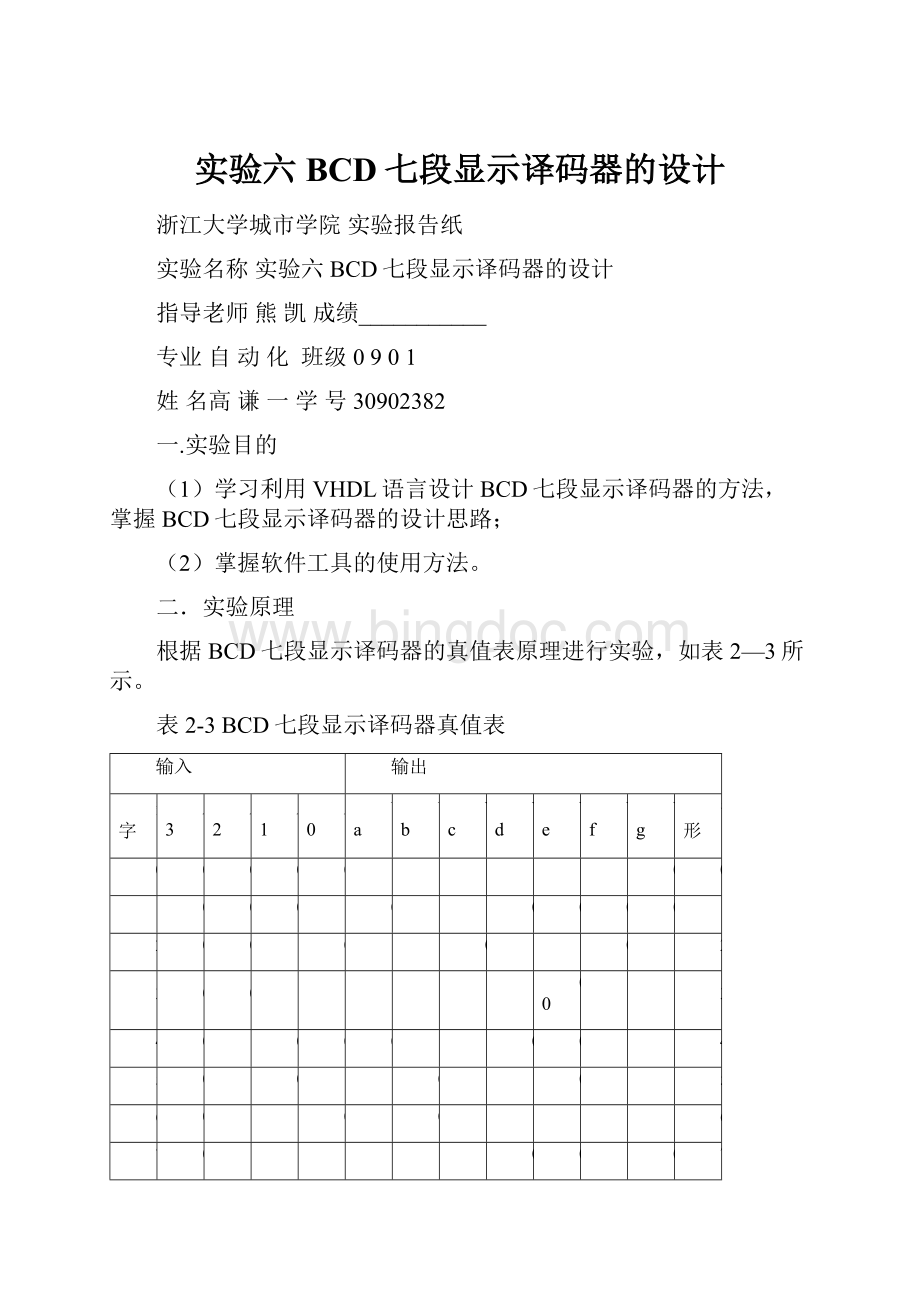

根据BCD七段显示译码器的真值表原理进行实验,如表2—3所示。

表2-3BCD七段显示译码器真值表

输入

输出

数字

A3

A2

A1

A0

Ya

Yb

Yc

Yd

Ye

Yf

Yg

字形

0

0

0

0

0

1

1

1

1

1

1

0

0

1

0

0

0

1

0

1

1

0

0

0

0

1

2

0

0

1

0

1

1

0

1

1

0

1

2

3

0

0

1

1

1

1

1

1

00

1

3

4

0

1

0

0

0

1

1

0

0

1

1

4

5

0

1

0

1

1

0

1

1

0

1

1

5

6

0

1

1

0

1

0

1

1

1

1

1

6

7

0

1

1

1

1

1

1

0

0

1

0

7

8

1

0

0

0

1

1

1

1

1

1

1

8

9

1

0

0

1

1

1

1

1

0

1

1

9

10

1

0

1

0

1

1

1

0

1

1

1

A

11

1

0

1

1

0

0

1

1

1

1

1

B

12

1

1

0

0

1

0

0

1

1

1

0

C

13

1

1

0

1

0

1

1

1

1

0

1

D

14

1

1

1

0

1

0

0

1

1

1

1

E

15

1

1

1

1

1

0

0

0

1

1

1

F

三.实验内容

用VHDL语言设计BCD七段显示译码器,进行编译、波形仿真及器件编程,并自行用VHDL语言设计3线-8线译码器。

四.源程序清单

libraryieee;

useieee.std_logic_1164.all;

entitygaoqianyiis

port(a:

instd_logic_vector(3downto0);

y:

outstd_logic_vector(6downto0));

endgaoqianyi;

architecturezhangofgaoqianyiis

begin

process(a)

begin

caseais

when"0000"=>y<="0111111";--0的BCD七段码

when"0001"=>y<="0000110";--1的BCD七段码

when"0010"=>y<="1011011";--2的BCD七段码

when"0011"=>y<="1001111";--3的BCD七段码

when"0100"=>y<="1100110";--4的BCD七段码

when"0101"=>y<="1101101";--5的BCD七段码

when"0110"=>y<="1111101";--6的BCD七段码

when"0111"=>y<="0100111";--7的BCD七段码

when"1000"=>y<="1111111";--8的BCD七段码

when"1001"=>y<="1101111";--9的BCD七段码

when"1010"=>y<="1110111";--A的BCD七段码

when"1011"=>y<="1111100";--B的BCD七段码

when"1100"=>y<="0111001";--C的BCD七段码

when"1101"=>y<="1011110";--D的BCD七段码

when"1110"=>y<="1111001";--E的BCD七段码

whenothers=>y<="1110001";--F的BCD七段码

endcase;

endprocess;

endzhang;

附加:

3线-8线译码器

表2-43线-8线译码器真值表

输入

输出

S1

S2+S3

A2

A1

A0

Y7

Y6

Y5

Y4

Y3

Y2

Y1

Y0

0

X

X

X

X

1

1

1

1

1

1

1

1

X

1

X

X

X

1

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

1

1

1

0

1

0

0

0

1

1

1

1

1

1

1

0

1

1

0

0

1

0

1

1

1

1

1

0

1

1

1

0

0

1

1

1

1

1

1

0

1

1

1

1

0

1

0

0

1

1

1

0

1

1

1

1

1

0

1

0

1

1

1

0

1

1

1

1

1

1

0

1

1

0

1

0

1

1

1

1

1

1

1

0

1

1

1

0

1

1

1

1

1

1

1

不带使能端

libraryieee;

useieee.std_logic_1164.all;

entitygaoqianyi11is

port(a:

instd_logic_vector(2downto0);

y:

outstd_logic_vector(7downto0));

endgaoqianyi11;

architecturezhangofgaoqianyi11is

begin

withaselect

y<="11111110"when"000",

"11111101"when"001",

"11111011"when"010",

"11110111"when"011",

"11101111"when"100",

"11011111"when"101",

"10111111"when"110",

"01111111"when"111",

"11111111"whenothers;

endzhang;

带使能端

libraryIEEE;

useIEEE.std_logic_1164.all;

entitygaoqianyi111is

port(

A:

instd_logic_vector(2downto0);

S1,S2,S3:

instd_logic;

Y:

outstd_logic_vector(7downto0)

);

endentity;

architecturegaoqianyi111_archofgaoqianyi111is

signals:

std_logic_vector(2downto0);

begin

S<=S1&S2&S3;

process(A,S)

begin

Y<=(others=>'1');

ifS="100"then

caseAis

when"000"=>y<="11111110";

when"001"=>y<="11111101";

when"010"=>y<="11111011";

when"011"=>y<="11110111";

when"100"=>y<="11101111";

when"101"=>y<="11011111";

when"110"=>y<="10111111";

when"111"=>y<="01111111";

whenothers=>NULL;

endcase;

endif;

endprocess;

endarchitecture;

五.实验总结

我学会了利用VHDL语言设计BCD七段显示译码器的方法和自己编写类似的程序。