福州大学数字电子技术基础试题7.docx

《福州大学数字电子技术基础试题7.docx》由会员分享,可在线阅读,更多相关《福州大学数字电子技术基础试题7.docx(10页珍藏版)》请在冰点文库上搜索。

福州大学数字电子技术基础试题7

福州大学数字电子技术基础试题-(7)

一填空:

(每题3分,共30分)

1、CMOS集成电路的优点是()。

2、若一个二进制数为‘-11001’,则它的反码为(),补码为()。

3、BCD8421码100001000对应的十进制数为(),十六进制数F3对应的二进制数为()。

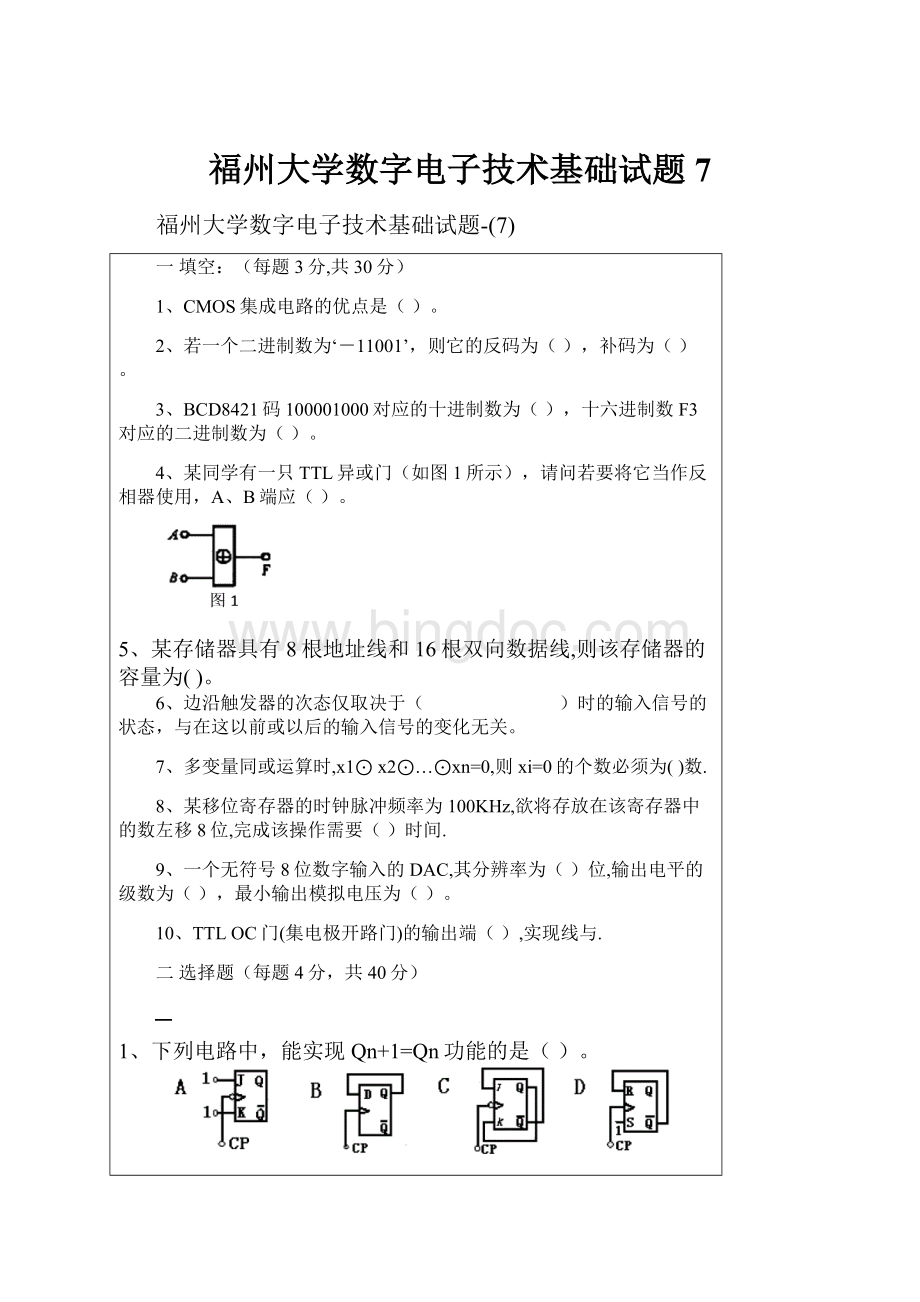

4、某同学有一只TTL异或门(如图1所示),请问若要将它当作反相器使用,A、B端应()。

5、某存储器具有8根地址线和16根双向数据线,则该存储器的容量为()。

6、边沿触发器的次态仅取决于( )时的输入信号的状态,与在这以前或以后的输入信号的变化无关。

7、多变量同或运算时,x1⊙x2⊙…⊙xn=0,则xi=0的个数必须为()数.

8、某移位寄存器的时钟脉冲频率为100KHz,欲将存放在该寄存器中的数左移8位,完成该操作需要()时间.

9、一个无符号8位数字输入的DAC,其分辨率为()位,输出电平的级数为(),最小输出模拟电压为()。

10、TTLOC门(集电极开路门)的输出端(),实现线与.

二选择题(每题4分,共40分)

1、下列电路中,能实现Qn+1=Qn功能的是()。

2、、由TTL门组成的电路如右图所示。

已知它们的输入短路电流IIS为1.5mA,它们的高电平输入电流IIH为0.05mA。

当A为1或0时,G1的输出端电流分

别为()mA。

A6mA、0.2mAB6mA、0.15mA

C4.5mA、0.15mAD4.5mA、0.2mA

3、下图均为TTL电路,试问()电路能实现

的逻辑关系。

共6页第2页

4、下图是一个TTL微分型单稳态触发器。

决定暂稳态时间的主要因素是:

AR、CBR1、C1

CR、C、与非门G1的高电平输出电阻

DR、C、与非门G2的输入端电阻

5、下列说法不正确的是()。

ATTL与非门输入端所接电阻不能太大。

BTTL与非门输出端不能并联使用。

C译码器、计数器、全加器、比较器都是组合逻辑电路。

DN进制计数器可以实现N分频。

6、某二极管ROM电路点阵图如下所示,当A1A0=00时,Y1Y2=()。

AY1Y2=00BY1Y2=01

CY1Y2=10DY1Y2=11

7、若二进制数D的反码为(11101),则D=( )。

A-0010B1101

C0011 D-0011

8、如图所示DAC电路,当输入数字量d3d2d1d0=1001时,输出电压vO为()

A

B

C

D

9、逻辑函数

和F=A⊙B不满足下式()。

A

BY=F⊙0

C

D

10、图示电路是采用同步十进制计数器和与非门构成的()计数器。

A五进制B六进制

C七进制D八进制

共6页第3页

三综合题(共80分,其中1~5题中任选4题,如果全做,按前4题计分)

1、(10分)下图所示电路为发光二极管驱动电路,其中OC门的输出低电平VOL=0.3V,输出低电平时的最大负载电流IOL=12mA;发光二极管的导通电压VD=1.5V,发光时其电流10mA≤ID≤15mA。

试问:

(1)在附图a、b所示电路中,发光二极管各在什么情况下发光?

(2)电阻R1、R2的取值范围。

2、(10分)分析下列图a所示时序电路,要求:

(1)写出电路的驱动方程和状态方程。

(2)画出电路的状态转换图。

(3)如图b所示,画出给定输入下的时序图。

设Q2、Q1初始状态均为0。

(4)叙述电路的逻辑功能。

3、(10分)下图是用TTL门电路接成的微分单稳态触发器。

其中Rd阻值足够的大,保证稳态时VA为高电平;R的阻值很小,保证稳态时VI2为低电平。

Cd的电容量很小,它与Rd组成微分电路。

试分析该电路在给定触发信号Vi作用下的工作过程,画出VA、Vo1、VI2和VO的电压波形图。

4、(10分)试分析下图所示由4位双向移位寄存器74LS194和3-8译码器构成的电路。

共6页第4页

(1)

画出该电路的状态转换图(设起始状态为110)。

74LS138

(2)指出该电路输出端Z产生什么序列。

74LS194

5、(10分)下图中均为CMOS门电路,分析下列电路,写出电路的输出函数表达式。

(以上5题中选作4题,

如果全做,按前4题计分)

6、(20分)已知某同步时序电路的状态表如表a所示,其中X为电路的输入,Z为电路的输出。

(1)试作出该电路的状态转换图。

(2)若用JK触发器实现电路,试写出该电路的激励方程和输出方程。

(3)画出用JK触发器实现的电路图。

(4)若要求Q2、Q1和Z波形如图b所示,则输人信号X应如何设置,画出X的波形图。

7、(20分)组合电路的设计

图b

试用两片4位二进制并行加法器74LS283和必要的门电路组成1位BCD8421码加法器电路。

共6页第5页

附录

1、双向移位寄存器74LS194的功能表

RD

S1

S0

工作状态

0

X

X

置零

1

0

0

保持

1

0

1

右移

1

1

0

左移

1

1

1

并行输入

2、十进制计数器74LS160功能表

CP

RDLDEPET

Q3Q2Q1Q0

×

0×××

0000

10××

D3D2D1D0

×

1101

保持

×

11×0

保持(c=0)

1111

计数

3、三线-八线译码器74LS138功能表

输入

输出

E1

E2+E3

A3

A2

A1

Y0

Y0

Y0

Y0

Y0

Y0

Y0

Y0

0

X

X

X

X

1

1

1

1

1

1

1

1

X

1

X

x

X

1

1

1

1

1

1

1

1

1

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

1

1

0

1

1

1

1

1

1

1

0

0

1

0

1

1

0

1

1

1

1

1

1

0

0

1

1

1

1

1

0

1

1

1

1

1

0

1

0

0

1

1

1

1

0

1

1

1

1

0

1

0

1

1

1

1

1

1

0

1

1

1

0

1

1

0

1

1

1

1

1

1

0

1

1

0

1

1

1

1

1

1

1

1

1

1

0

4、4位全加器74LS283逻辑图

共6页第6页