计数器及数码显示综合设计.docx

《计数器及数码显示综合设计.docx》由会员分享,可在线阅读,更多相关《计数器及数码显示综合设计.docx(18页珍藏版)》请在冰点文库上搜索。

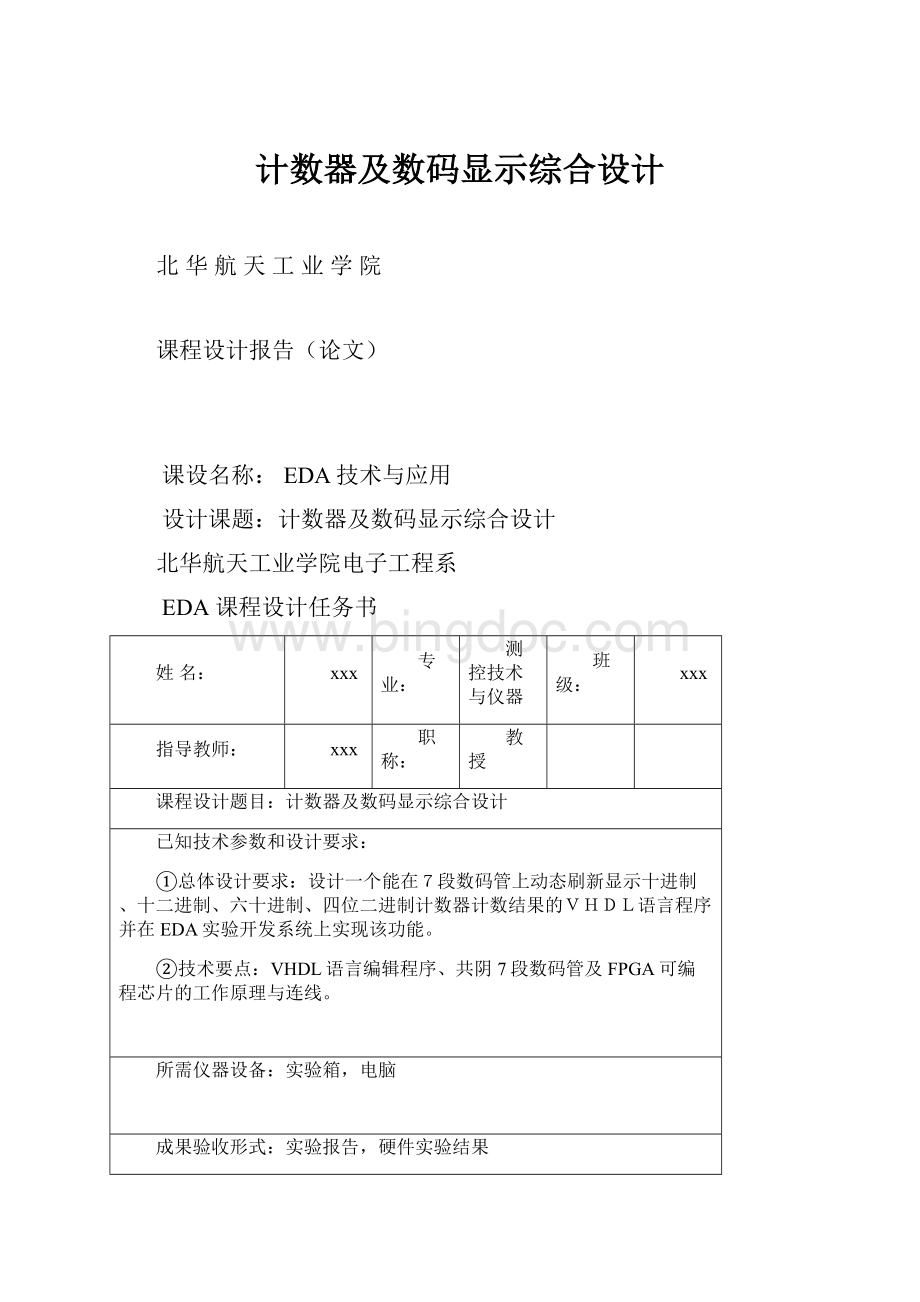

计数器及数码显示综合设计

北华航天工业学院

课程设计报告(论文)

课设名称:

EDA技术与应用

设计课题:

计数器及数码显示综合设计

北华航天工业学院电子工程系

EDA课程设计任务书

姓名:

xxx

专业:

测控技术与仪器

班级:

xxx

指导教师:

xxx

职称:

教授

课程设计题目:

计数器及数码显示综合设计

已知技术参数和设计要求:

①总体设计要求:

设计一个能在7段数码管上动态刷新显示十进制、十二进制、六十进制、四位二进制计数器计数结果的VHDL语言程序并在EDA实验开发系统上实现该功能。

②技术要点:

VHDL语言编辑程序、共阴7段数码管及FPGA可编程芯片的工作原理与连线。

所需仪器设备:

实验箱,电脑

成果验收形式:

实验报告,硬件实验结果

参考文献:

李国洪、胡辉、沈明山等编著《EDA技术与实验》—机械工业出版社出版。

时间

安排

2014年12月14日-15日编辑VHDL语言程序

2014年12月16日硬件调试程序

2014年12月17日实验箱答辩验收

指导教师:

齐建玲教研室主任:

王晓

2014年12月17日

内容摘要

用VHDL语言在MAX+PLUS2环境下

设计一个带使能输入、进位输出及同步清零的十进制计数器。

设计一个带使能输入及同步清零的十二进制计数器。

设计一个带使能输入及同步清零的六十进制加法计数器。

设计一个四位二进制可逆计数器。

设计一个共阴7段数码管控制接口,在时钟信号的控制下,使六位数码管动态刷新显示上述计数器的计数结果。

最后在EDA实验开发系统实验操作。

目录

一、概述1

二、方案设计与论证1

三、单元电路设计与参数计算1

1、十进制计数器1

2、十二进制计数器2

3、六十进制计数器3

4、十六进制可逆计数器4

5、六进制计数器5

6、数据选择器6

7、4-7译码器7

四、顶层文件8

1、截图8

2、程序8

五、安装与调试10

六、心得体会10

1.实验注意事项10

2.收获与体会10

一、概述

用VHDL语言在MAX+PLUS2环境下

设计一个带使能输入、进位输出及同步清零的十进制计数器。

设计一个带使能输入及同步清零的十二进制计数器。

设计一个带使能输入及同步清零的六十进制加法计数器。

设计一个四位二进制可逆计数器。

设计一个共阴7段数码管控制接口,在时钟信号的控制下,使六位数码管动态刷新显示上述计数器的计数结果。

2、方案设计与论证

四个计数器同时开始计数,通过计数器的使能端可以随时控制计数器是否继续工作,通过同步清零端可以随时把任何一个计数器清零重新开始计数。

四位二进制可逆计数器可以随时进行加计数或减计数。

通过六进制计数器扫描数码管和作为对其他4个计数器的选择信号,再通过一个数据选择器选择出计数器的输出信号,通过4-7译码器的输出信号在数码

当时钟信号频率足够大时可以实现六个数码管“同时”显示各计数器的计数结果。

因为人的眼睛分辨不出各数码管的快速跳变。

所以能实现所要求的同步计数的目的。

三、单元电路设计与参数计算

1、十进制计数器

代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYJINZHI10IS

PORT(CLK,en,rst:

INSTD_LOGIC;

ci:

OUTSTD_LOGIC;

dout:

BUFFERSTD_LOGIC_VECTOR(3DOWNTO0));

ENDJINZHI10;

ARCHITECTUREABCOFJINZHI10IS

BEGIN

ci<='1'WHENdout="1001"ANDen='1'ELSE'0';

PROCESS(CLK,en,rst)

BEGIN

IFRISING_EDGE(CLK)THEN

IFrst='1'THENdout<=(OTHERS=>'0');

ELSIFen='1'THEN

IFdout="1001"THENdout<="0000";

ELSEdout<=dout+1;

ENDIF;

ENDIF;

ENDIF;

ENDPROCESS;

ENDABC;

仿真结果:

2、十二进制计数器

代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYJINZHI12IS

PORT(CLK,en,rst:

INSTD_LOGIC;

dout:

BUFFERSTD_LOGIC_VECTOR(3DOWNTO0));

ENDJINZHI12;

ARCHITECTUREABCOFJINZHI12IS

BEGIN

PROCESS(CLK,en,rst)

BEGIN

ifRISING_EDGE(CLK)THEN

ifrst='1'thendout<=(others=>'0');

ELSIFen='1'THEN

IFdout="1011"THENdout<="0000";

ELSEdout<=dout+1;

ENDIF;

ENDIF;

ENDIF;

ENDPROCESS;

ENDABC;

仿真结果

3、六十进制计数器

代码

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYJINZHI60IS

PORT(CLK,en,rst:

INSTD_LOGIC;

OL,OH:

BUFFERSTD_LOGIC_VECTOR(3DOWNTO0));

ENDJINZHI60;

ARCHITECTUREABCOFJINZHI60IS

BEGIN

PROCESS(CLK,en,rst)

BEGIN

IFRISING_EDGE(CLK)THEN

IFrst='1'THENOL<="0000";OH<="0000";

ELSIFen='1'THEN

IFOL="1001"THENOL<="0000";

IFOH="0101"THENOH<="0000";

ELSEOH<=OH+1;

ENDIF;

ELSEOL<=OL+1;

ENDIF;

ENDIF;

ENDIF;

ENDPROCESS;

ENDABC;

仿真结果

4、十六进制可逆计数器

代码

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYKENI16IS

PORT(CLK,JJ,E:

INSTD_LOGIC;

OL,OH:

BUFFERSTD_LOGIC_VECTOR(3DOWNTO0));

ENDKENI16;

ARCHITECTUREABCOFKENI16IS

BEGIN

PROCESS(CLK,JJ,E)

BEGIN

IFRISING_EDGE(CLK)THEN

IFE='1'THEN

IFJJ='1'THEN

IFOL="0101"ANDOH="0001"THENOL<="0000";OH<="0000";

ELSIFOL="1001"THENOL<="0000";OH<=OH+1;

ELSEOL<=OL+1;

ENDIF;

ELSIFJJ='0'THEN

IFOL="0000"ANDOH="0000"THENOL<="0101";OH<="0001";

ELSIFOL="0000"THENOL<="1001";OH<=OH-1;

ELSEOL<=OL-1;

ENDIF;

ENDIF;

ENDIF;

ENDIF;

ENDPROCESS;

ENDABC;

仿真结果

5、六进制计数器

代码

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYJINZHI6IS

PORT(CLK,E:

INSTD_LOGIC;

O:

BUFFERSTD_LOGIC_VECTOR(2DOWNTO0));

ENDJINZHI6;

ARCHITECTUREABCOFJINZHI6IS

BEGIN

PROCESS(CLK,E)

BEGIN

IFRISING_EDGE(CLK)THEN

IFE='1'THEN

IFO="101"THENO<="000";

ELSEO<=O+1;

ENDIF;

ENDIF;

ENDIF;

ENDPROCESS;

ENDABC;

仿真结果

6、数据选择器

代码

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYXUANZEIS

PORT(A,B,C,D,E,F:

INSTD_LOGIC_VECTOR(3DOWNTO0);

I:

INSTD_LOGIC_VECTOR(2DOWNTO0);

O:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDXUANZE;

ARCHITECTUREABCOFXUANZEIS

BEGIN

PROCESS(I)

BEGIN

CASEIIS

WHEN"000"=>O<=A;

WHEN"001"=>O<=B;

WHEN"010"=>O<=C;

WHEN"011"=>O<=D;

WHEN"100"=>O<=E;

WHEN"101"=>O<=F;

WHENOTHERS=>NULL;

ENDCASE;

ENDPROCESS;

ENDABC;

仿真结果

7、4-7译码器

代码

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYYM_47IS

PORT(I:

INSTD_LOGIC_VECTOR(3DOWNTO0);

O:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

ENDYM_47;

ARCHITECTUREABCOFYM_47IS

BEGIN

WITHISELECT

O<="1111110"WHEN"0000",

"0110000"WHEN"0001",

"1101101"WHEN"0010",

"1111001"WHEN"0011",

"0110011"WHEN"0100",

"1011011"WHEN"0101",

"1011111"WHEN"0110",

"1110000"WHEN"0111",

"1111111"WHEN"1000",

"1111011"WHEN"1001",

"1110111"WHEN"1010",

"0011111"WHEN"1011",

"0000000"WHENOTHERS;

ENDABC;

仿真结果

4、顶层文件

1、截图

2、程序

libraryieee;

useieee.std_logic_1164.all;

entityJISHUQIis

port(clk,clk6:

instd_logic;

en:

instd_logic;

rst10,rst12,rst60:

instd_logic;

jj:

instd_logic;

ci10:

outstd_logic;

dout:

outstd_logic_vector(6downto0);

sel:

outstd_logic_vector(2downto0));

endJISHUQI;

architecturebehaveofJISHUQIis

componentJINZHI10

PORT(CLK,En,rst:

INSTD_LOGIC;

Ci:

OUTSTD_LOGIC;

dout:

BUFFERSTD_LOGIC_VECTOR(3DOWNTO0));

endcomponent;

componentJINZHI12

PORT(CLK,en,rst:

INSTD_LOGIC;

dout:

BUFFERSTD_LOGIC_VECTOR(3DOWNTO0));

endcomponent;

componentJINZHI60

PORT(CLK,En,rst:

INSTD_LOGIC;

OL,OH:

BUFFERSTD_LOGIC_VECTOR(3DOWNTO0));

endcomponent;

componentKENI16

PORT(CLK,JJ,E:

INSTD_LOGIC;

OL,OH:

BUFFERSTD_LOGIC_VECTOR(3DOWNTO0));

endcomponent;

componentYM_47

PORT(I:

INSTD_LOGIC_VECTOR(3DOWNTO0);

O:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

endcomponent;

componentJINZHI6

PORT(CLK,E:

INSTD_LOGIC;

O:

BUFFERSTD_LOGIC_VECTOR(2DOWNTO0));

endcomponent;

componentXUANZE

PORT(A,B,C,D,E,F:

INSTD_LOGIC_VECTOR(3DOWNTO0);

I:

INSTD_LOGIC_VECTOR(2DOWNTO0);

O:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

endcomponent;

signaldouta,doutb,doutc,doutd,doute,doutf:

std_logic_vector(3downto0);

signaldouti:

std_logic_vector(2downto0);

signaloutin:

std_logic_vector(3downto0);

begin

u1:

JINZHI10portmap(clk=>clk,en=>en,rst=>rst10,ci=>ci10,dout=>douta);

u2:

JINZHI12portmap(clk=>clk,en=>en,rst=>rst12,dout=>doutb);

u3:

JINZHI60portmap(clk=>clk,en=>en,rst=>rst60,OL=>doutc,OH=>doutd);

u4:

KENI16portmap(clk=>clk,JJ=>JJ,e=>en,ol=>doute,oh=>doutf);

u5:

JINZHI6portmap(clk=>clk6,e=>en,o=>douti);

u6:

XUANZEportmap(a=>douta,b=>doutb,c=>doutc,d=>doutd,e=>doute,f=>doutf,i=>douti,o=>outin);

u7:

YM_47portmap(i=>outin,o=>dout);

sel<=douti;

endbehave;

五、安装与调试

在计算机和试验箱均断电的情况下连接好下载电缆和芯片的各端口之间的连线,接下来先给试验箱供电然后打开计算机找到MAX+plus2软件将先前已编辑好的的程序下载到芯片上。

调整时钟信号的频率直到7段数码管能实现所求的功能。

6、心得体会

1.实验注意事项

①不能再带电情况下拔插下载电缆。

②连接好下载电缆后应先接通实验箱的电源,再接通计算机的电源。

③测试完毕后应先断开计算机的电源再断开试验箱的电源最后拔下下载电缆的两个插头。

2.收获与体会

①掌握了十进制、十二进制、六十进制、十六进制计数器的设计方法。

②掌握多位计数器相连的设计方法。

③掌握了CPLD技术的层次化结构化设计方法。

④通过同一设计小组的几个同学分做不同模块然后将不同模块合起来联试,培养了大家的分工与合作的团队意识,同时加深对层次化设计理念的理解。

电子工程系EDA课程设计成绩评定表

专业:

测控技术与仪器班级:

B12241学号:

38姓名:

白冬雪田尉均

课题名称

计数器及数码显示综合设计

设计任务与要求

①总体设计要求:

设计一个能在7段数码管上动态刷新显示十进制、十二进制、六十进制、四位二进制计数器计数结果的VHDL语言程序并在EDA实验开发系统上实现该功能。

②技术要点:

VHDL语言编辑程序、共阴7段数码管及FPGA可编程芯片的工作原理与连线。

指导教师评语

建议成绩:

指导教师:

课程小组评定

评定成绩:

课程负责人:

2014年12月17日忽略此处..