基于FPGA的VHDL语言m序列生成详解+源码.docx

《基于FPGA的VHDL语言m序列生成详解+源码.docx》由会员分享,可在线阅读,更多相关《基于FPGA的VHDL语言m序列生成详解+源码.docx(17页珍藏版)》请在冰点文库上搜索。

基于FPGA的VHDL语言m序列生成详解+源码

说明

可控m序列产生器我分成四个小模块来做,M,M1,M2,M3分别对应为:

m序列产生器、控制器、码长选择器、码速率选择器。

一、M:

m序列产生器

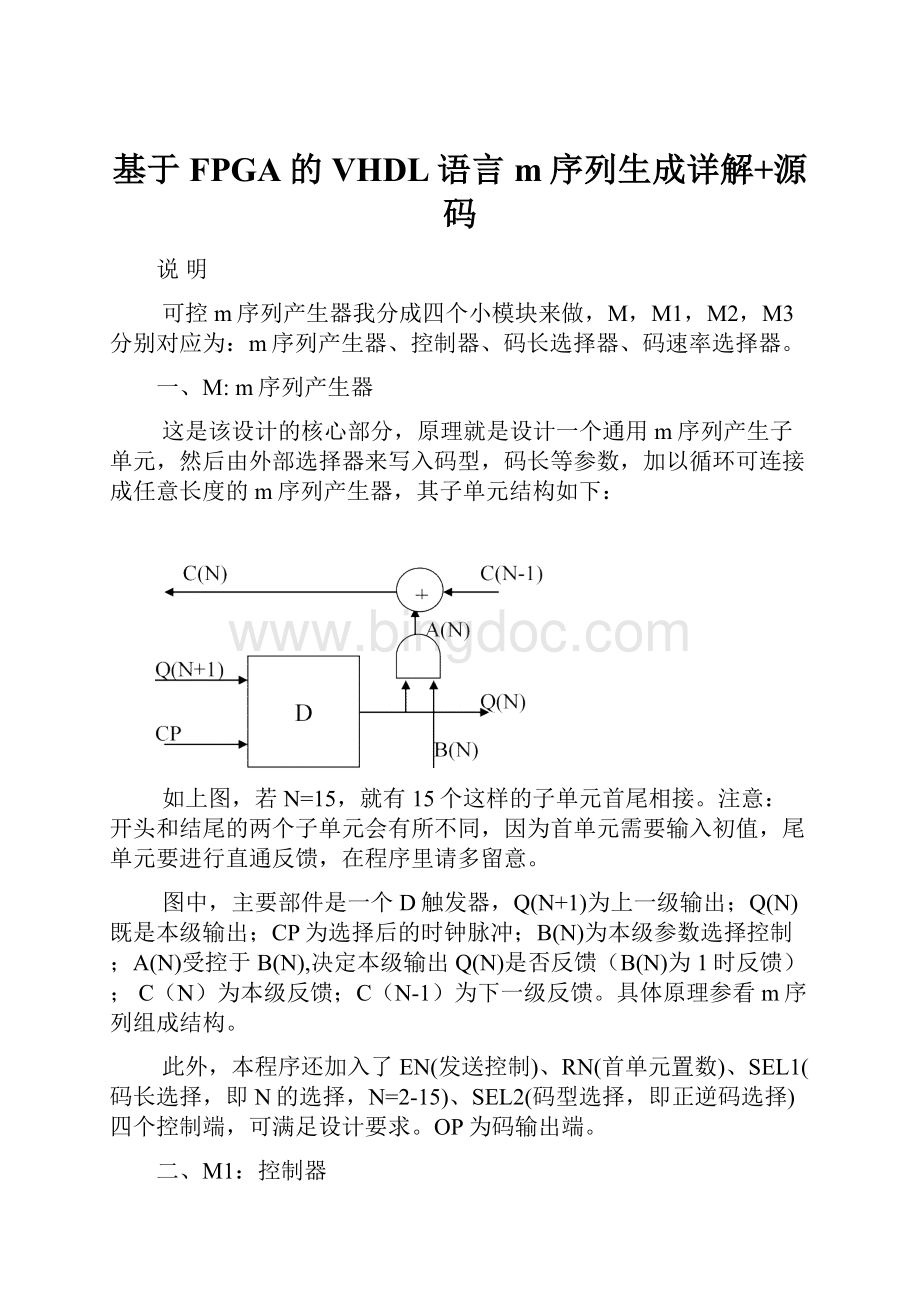

这是该设计的核心部分,原理就是设计一个通用m序列产生子单元,然后由外部选择器来写入码型,码长等参数,加以循环可连接成任意长度的m序列产生器,其子单元结构如下:

如上图,若N=15,就有15个这样的子单元首尾相接。

注意:

开头和结尾的两个子单元会有所不同,因为首单元需要输入初值,尾单元要进行直通反馈,在程序里请多留意。

图中,主要部件是一个D触发器,Q(N+1)为上一级输出;Q(N)既是本级输出;CP为选择后的时钟脉冲;B(N)为本级参数选择控制;A(N)受控于B(N),决定本级输出Q(N)是否反馈(B(N)为1时反馈);C(N)为本级反馈;C(N-1)为下一级反馈。

具体原理参看m序列组成结构。

此外,本程序还加入了EN(发送控制)、RN(首单元置数)、SEL1(码长选择,即N的选择,N=2-15)、SEL2(码型选择,即正逆码选择)四个控制端,可满足设计要求。

OP为码输出端。

二、M1:

控制器

控制器主要是将外部的序列发送控制信号STA转换为EN和RN两个控制信号。

其中,EN与STA的波形基本一致,只是它与CP进行了同步处理;RN在EN为‘1’的头一个脉冲周期里置高电平,以达到为序列发生器的首端置数的目的。

如果不清楚的话可以看一下它的模拟波形。

(注意:

STA要采用自锁定开关,高电平有效)

三、M2:

码长选择

序列的码长选择既是N值的选择,码长=2**N-1。

核心就是一个计数器,可从2计到15。

按一次PUSH就可以自动加一(注意:

按键建议采用自弹跳按键,如过需要软件清除按键震颤的话,我再做发给你),没有0,1两个状态。

如果需要的话还可以扩展7段数码管的接口,以显示N值。

四、M3:

码速率选择器

码的传输速率是靠CP来控制的,CP的频率就等于码元速率。

这段程序包含一个倍频器,一个5分频的分频器,可把5MHZ的脉冲源CLK扩展成1MHZ和10MHZ。

FSEL1、FSLE2、FSEL3分别在选择1、5、10MHZ时为高电平,其余两个为低,建议采用3选1单刀单掷开关。

M1--------------------------------------------------

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCTRLIS

PORT(

CP,STA:

INSTD_LOGIC;

EN,RN:

OUTSTD_LOGIC

);

ENDCTRL;

ARCHITECTUREaOFCTRLIS

SIGNALQ1,Q2:

STD_LOGIC;

BEGIN

PROCESS(CP)

BEGIN

IFCP’eventANDCP=’1’THEN

Q2<=Q1;

Q1<=STA;

ENDIF;

ENDPROCESS;

EN<=Q1;

RN<=Q1ANDNOTQ2;

ENDa;

M2-------------------------------------------------

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCOUNTERIS

PORT(

PUSH,EN,RST:

INSTD_LOGIC;

SEL1:

OUTSTD_LOGIC_VECTOR(3DOWNTO0)

);

ENDCOUNTER;

ARCHITECTUREaOFCOUNTERIS

SIGNALB,C:

STD_LOGIC;

SIGNALQN:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

PROCESS(PUSH,C)

BEGIN

IFEN=’0’THEN

IFC=’1’THEN

QN<=”0010”;

ELSEIFPUSH’EVENTANDPUSH=’1’THEN

QN<=QN+1;

ENDIF;

ELSE

QN<=QN;

ENDIF;

ENDPROCESS;

B<=’1’WHENQN=”0000”ELSE

‘0’;

C<=BORRST;

SEL1<=QN;

ENDa;

M3-----------------------------------

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYFPIS

PORT(

CLK,FSEL1,FSEL2,FSEL3:

INSTD_LOGIC;

CP:

OUTSTD_LOGIC

);

ENDFP;

ARCHITECTUREaOFFPIS

SIGNALQ1,Q2,Q3,RST:

STD_LOGIC;

SIGNALM1,M5,M10:

STD_LOGIC;

SIGNALQN:

STD_LOGIC_VECTOR(2DOWNTO0);

BEGIN

BP1:

BLOCK

BEGIN

PROCESS(CLK,Q1)

BEGIN

IFQ1=’1’THEN

Q1<=’0’

ELSEIFCLK’EVENTANDCLK=’1’THEN

Q1<=’1’;

ENDIF;

ENDPROCESS;

ENDBLOCKBP1;

BP2:

BLOCK

BEGIN

PROCESS(CLK,Q2)

BEGIN

IFQ2=’1’THEN

Q2<=’0’

ELSEIFCLK’EVENTANDCLK=’0’THEN

Q2<=’1’;

ENDIF;

ENDPROCESS;

ENDBLOCKBP2;

FP:

BLOCK

BEGIN

PROCESS(CLK,RST)

BEGIN

IFRST=’1’THEN

QN<=”000”;

ELSEIFCLK’EVENTANDCLK=’1’THEN

QN<=QN+1;

ENDIF;

ENDPROCESS;

ENDBLOCKFP;

Q3<=Q1ORQ2;

RST<=’1’WHENQN=”101”ELSE

‘0’;

M1<=QN

(2)ANDFSEL1;

M2<=CLKANDFSEL2;

M3<=Q3ANDFSEL3;

CP<=M1ORM2ORM3;

ENDa;

M----------------------------------------

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYPN1IS

PORT(

CP,SEL2,EN,RN:

INSTD_LOGIC;

SEL1:

INSTD_LOGIC_VECTOR(3DOWNTO0);

OP:

OUTSTD_LOGIC

);

ENDPN1;

ARCHITECTUREaOFPN1IS

SIGNALQ,A,B,C:

STD_LOGIC_VECTOR(14DOWNTO0);

SIGNALSEL:

STD_LOGIC_VECTOR(4DOWNTO0);

BEGIN

SEL<=SEL1&SEL2;

PROCESS(CP,SEL)

BEGIN

IFCP'eventANDCP='1'THEN

IFEN='0'THEN

Q<="0000";

OP<=Q(0);

ELSE

Q(14)<=C(14)ORRN;

B<="0000";

CASESELIS

WHEN"11111"=>

C(0)<=Q(0);

B

(1)<='1';

FORIIN1TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(0);

WHEN"11110"=>

C(0)<=Q(0);

B(14)<='1';

FORIIN1TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(0);

WHEN"11101"=>

C

(1)<=Q

(1);

B

(2)<='1';

B(7)<='1';

B(11)<='1';

FORIIN2TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q

(1);

WHEN"11100"=>

C

(1)<=Q

(1);

B(5)<='1';

B(9)<='1';

B(14)<='1';

FORIIN2TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q

(1);

WHEN"11011"=>

C

(2)<=Q

(2);

B(3)<='1';

B(5)<='1';

B(6)<='1';

FORIIN3TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q

(2);

WHEN"11010"=>

C

(2)<=Q

(2);

B(11)<='1';

B(12)<='1';

B(14)<='1';

FORIIN3TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q

(2);

WHEN"11001"=>

C(3)<=Q(3);

B(4)<='1';

B(7)<='1';

B(9)<='1';

FORIIN4TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(3);

WHEN"11000"=>

C(3)<=Q(3);

B(9)<='1';

B(11)<='1';

B(14)<='1';

FORIIN4TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(3);

WHEN"10111"=>

C(4)<=Q(4);

B(6)<='1';

FORIIN5TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(4);

WHEN"10110"=>

C(4)<=Q(4);

B(13)<='1';

FORIIN5TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(4);

WHEN"10101"=>

C(5)<=Q(5);

B(8)<='1';

FORIIN6TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(5);

WHEN"10100"=>

C(5)<=Q(5);

B(12)<='1';

FORIIN6TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(5);

WHEN"10011"=>

C(6)<=Q(6);

B(10)<='1';

FORIIN7TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(6);

WHEN"10010"=>

C(6)<=Q(6);

B(11)<='1';

FORIIN7TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(6);

WHEN"10001"=>

C(7)<=Q(7);

B(9)<='1';

B(10)<='1';

B(11)<='1';

FORIIN8TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(7);

WHEN"10000"=>

C(7)<=Q(7);

B(11)<='1';

B(12)<='1';

B(13)<='1';

FORIIN8TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(7);

WHEN"01111"=>

C(8)<=Q(8);

B(11)<='1';

FORIIN9TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(8);

WHEN"01110"=>

C(8)<=Q(8);

B(12)<='1';

FORIIN9TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(8);

WHEN"01101"=>

C(9)<=Q(9);

B(10)<='1';

FORIIN10TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(9);

WHEN"01100"=>

C(9)<=Q(9);

B(14)<='1';

FORIIN10TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(9);

WHEN"01011"=>

C(10)<=Q(10);

B(12)<='1';

FORIIN11TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(10);

WHEN"01010"=>

C(10)<=Q(10);

B(13)<='1';

FORIIN11TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(10);

WHEN"01001"=>

C(11)<=Q(11);

B(12)<='1';

FORIIN12TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(11);

WHEN"01000"=>

C(11)<=Q(11);

B(14)<='1';

FORIIN12TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(11);

WHEN"00111"=>

C(12)<=Q(12);

B(13)<='1';

FORIIN13TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(12);

WHEN"00110"=>

C(12)<=Q(12);

B(14)<='1';

FORIIN13TO14LOOP

Q(I-1)<=Q(I);

A(I)<=Q(I)ANDB(I);

C(I)<=C(I-1)XORA(I);

ENDLOOP;

OP<=Q(12);

WHENOTHERS=>

C(13)<=Q(13);

B(14)<='1';

Q(13)<=Q(14);

A(14)<=Q(14)ANDB(14);

C(14)<=C(13)XORA(14);

OP<=Q(13);

ENDCASE;

ENDIf;

ENDIF;

ENDPROCESS;

ENDa;