数字逻辑实验报告36558.docx

《数字逻辑实验报告36558.docx》由会员分享,可在线阅读,更多相关《数字逻辑实验报告36558.docx(10页珍藏版)》请在冰点文库上搜索。

数字逻辑实验报告36558

武汉理工大学

院校:

计算机科学与技术学院

专业:

计算机科学与技术

学生姓名:

干M旭

班级:

Y1606学号0121610870113

2017年月日

实验一:

一位全加器

实验目的:

1.掌握组合逻辑电路的设计方法;

2.熟悉Vivado2014集成开发环境和Verilog编程语言;

3.掌握1位全加器电路的设计与实现。

试验工具:

1.Basys3FPGA开发板

2.Vivado2014集成开发环境和Verilog编程语言。

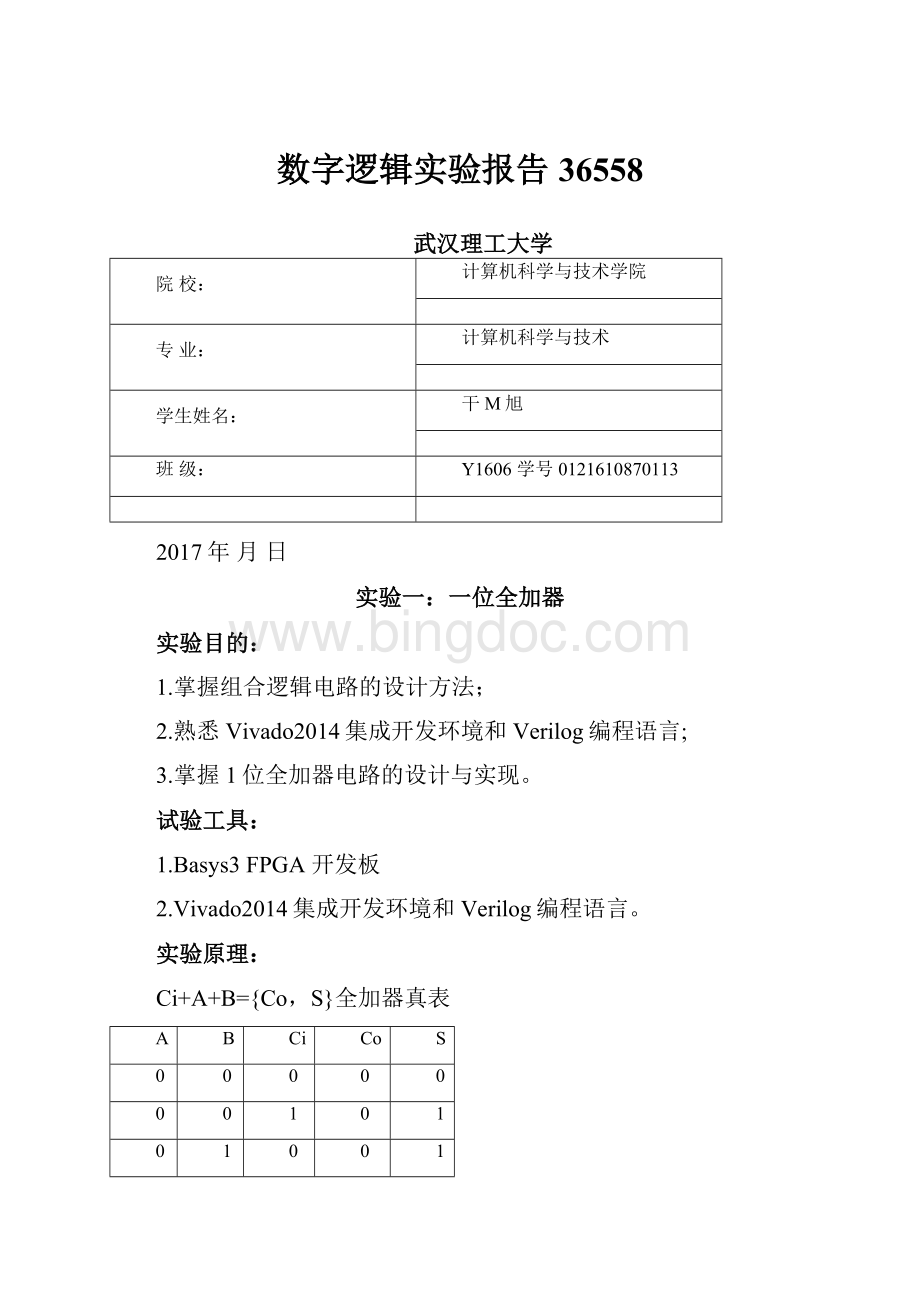

实验原理:

Ci+A+B={Co,S}全加器真表

A

B

Ci

Co

S

0

0

0

0

0

0

0

1

0

1

0

1

0

0

1

0

1

1

1

0

1

0

0

0

1

1

0

1

1

0

1

1

0

1

0

全加器逻辑表达式

S=AWBC+\Ci

Co=A.B+(A㊉B).Ci全加器电路图

I:

L11

实验步骤:

(一)新建工程:

1、打开Vivado2014.2开发工具,可通过桌面快捷方式或开始菜单中XilinxDesign

Tools->Vivado2014.2下的Vivado2014.2打开软件;

2、单击上述界面中CreateNewProject图标,弹出新建工程向导。

3、输入工程名称、选择工程存储路径,并勾选Createprojectsubdirectory选项,为工程在

指定存储路径下建立独立的文件夹。

设置完成后,点击Next。

注意:

工程名称和存储路径中

不能出现中文和空格,建议工程名称以字母、数字、下划线来组成

4、选择RTLProject一项,并勾选Donotspecifysourcesatthistime,为了跳过在新建

工程的过程中添加设计源文件。

5、根据使用的FPGA开发平台,选择对应的FPGA目标器件。

(在本手册中,以Xilinx大学计

划开发板DigilentBasys3为例,FPGA采用Artix-7XC7A35T-1CPG236-C的器件,即Family和Subfamily均为Artix-7,圭寸装形式(Package)为CPG236,速度等级(Speedgrade)为-1,温度等级(TempGrade)为C)。

点击Next。

6、确认相关信息与设计所用的的FPGA器件信息是否一致,一致请点击Finish,不一致,请

返回上一步修改。

7、得到如下的空白Vivado工程界面,完成空白工程新建。

(二)设计文件输入:

8、点击FlowNavigator下的ProjectManager->AddSources或中间Sources中的对话框打开设计文件导入添加对话框。

9、选择第二项AddorCreateDesignSources,用来添加或新建Verilog源文件。

10、如果有现有的V文件,可以通过AddFiles一项添加。

在这里,我们要新建文件,所以选择CreateFile一项。

11、在CreateSourceFile中输入FileName,这里为full_adder,点击OK。

注:

名称中不可出现中文和空格。

12、新建的设计文件(此处为full_adder.v)即存在于Sources中的DesignSources中。

打开该文件,输入相应的设计代码。

根据已知的电路图得到以下verilog代码:

module

fulladder(inoutx,inputy,inputz,

outputs,outputc,

);

wirew1,w2,w3;

xor(w1,x,y);

and(w2,x,y);

xor(s,w1,z);

and(w3,w1,z);

or(c,w3,w2);

endmodule

13、点击FlowNavigator中Synthesis中的RunSynthesis,对工程进行综合

14、综合完成之后,选择OpenSynthesizedDesign,打开综合结果

15、在layout中选择IOplanning一项。

16、在右下方的选项卡中切换到I/Oports一栏,并在对应的信号后,输入对应的FPGA管脚标

号,c,s,x,y,z的管脚分别设为E19,U19,V16,V17和w16(也可根据下方的引脚分配图1

自行选择)并指定I/Ostd电压为“LVCMOS33

17、完成之后,点击左上方工具栏中的保存按钮,工程提示新建XDC文件或选择工程中已

有的XDC文件。

点击OK完成约束过程。

(三)工程实现

18、在FlowNavigator中点击ProgramandDebug下的GenerateBitstream选项,工程会

自动完成综合、实现、Bit文件生成过程,完成之后,可点击OpenImplementedDesign来查看工程实现结果。

19、将basys3板用miniusb线连上电脑,打开basys3上的电源开关,在FlowNavigator中展开HardwareManager,点击OpenNewTarget)在FlowNavigator中展开HardwareManager,点击OpenNewTarget)

20、拨动开关键,测试LED灯的亮灭是否与全加器的逻辑功能相符。

试验现象:

将basys3板用miniusb线连上电脑,打开basys3上的电源开关

拨动开关1,LED1亮;拨动开关2,LED灯1灭,灯2亮;拨

动开关3,LED灯1亮,LED灯2灭,LED灯3亮。

实验结论:

通过对比开关控制下灯的熄灭与否和真值表,得出结论,全加

器的输入与输出与实际相符,实验步骤无误

实验二:

一位BCD码转余三码

试验内容:

电路

实验目的:

1.掌握组合逻辑电路的设计方法;

2.熟悉Vivado2014集成开发环境和Verilog编程语言;

3.掌握BCD码转余三码电路的设计与实现。

实验工具:

1.Basys3FPGA开发板,69套。

2.Vivado2014集成开发环境Verilog编程语言。

实验原理:

(1)功能描述:

将10个BCD码(0000——1001)转成余3码

(0011——1100),BCD的输入为ABCD,输出为WXYZ,

对应的真值表为:

ft

B

c

D

w

X

T

z

0

D

fl

0

0

0

L

1

LI

D

c

L

u

1

u

u

□

D

1

J

0

1

Q

1

□

0

1

1

0

1

訂

Q

1

0

U

u

J

:

1

0

1

0

1

1

c

0

0

1

1

1

0

0

1

□

1

I

L

1

c

L

0

1

D

r

D

1

0

I

1

1

0

Q

L

1

1

Q

Q

(2)布尔表达式

d=彷(10,11,12,13,14,15)

W=ABCD+ABCD+ABCD+ABCD+ABCD

X=ABCD+ABCD+ABCD+ABCD+ABCD

Y=ABCD+ABCD+ABCD+ABCD+ABCD

Z=ABCD+ABCD+ABCD+ABCD+ABCD

化简如下:

(3)逻辑电路图

NOTI

if■

X1

T

O2

O1

input

b,

inputc,

set_propertyPACKa3E_FIH[百叭_戸呃临i]

inpufta,

tet_propcrtyPAniA.GE_FI]TT16[e^t_poEtsb]

scl_pxQt?

EjrtyFAH{盘:

E_FIHV_Ci.Bcl_ports_]

output址』

set.propertyFAniAGE^FHVI7[get_ports刃

ouitpiityj

set_propErtyPAHi盘&E_門HV19[get_portst]

DlltptLtz

set_propertyFAWCEgFIH匸?

[巳#__『。

巩£x]

);

set_|jruptrtyPA*K?

.SE_FINE19[gel_puiLs/]

wxre3(1j.h?

.x3^x*,ylwl,T;

set_propertyPACKAGE_PIIT716[gct_portsz]

notno七

setpropertyIOST/JLARDLVCNOS33[getports&]

ndnot2*jt2,Tj:

set_propcrtyIOSTANDAE®LVC?

ffOS?

3Cset.portsfc]

Tkotn&t3Q,DI:

set_proptrtyIOSTANDABD1VCM0S33[gel_portsc]

axtd=9a3.1ImI,E,T):

set_property1OSIASDAHBLVCH0S33Ljet_portsd]

ar:

rleKd2xl,T);

setpropertyIOST/JDARDIVCNOSSSLretportsw]

aikde_ni3現xi2);

set_proptTtyIOiTANDAE®LVCMOSi3rgel_portsi]

Slid3J1I1+tjrl,C,D):

sel_|jrororlgJD):

setjroperty1OSIANDARDLVCJKJS33Lsel^portsz]

oror21#.A.ml?

1;

*r3k3,w43:

«r©r1Xjyl);

^■ndmodule

(2)操作符级别的Verilog代码和约束文件分别如下:

sel_propertyset_prcpertyscI_propertyse1_propcrtyset_propertyset_propertyie[_pruptrtyse1_propcrty

FACKAG?

_PIK¥1_

P*CEACI_PIN¥16

FACK^?

_PI«716FACKAGLFU'vr

PACKiGi_PIK719

PACIACI_PIBU19

PACKAG5_PIti519

PACKAGK.Pir716

[get_portsa][get_portEb][gcL_pvrtsc][get_portsd][get_portst][get_pseipropertyIOSTMlMDL7CMjS35_getpartsaset..propertyrDSTAIDARDLTCIDSS^Ce*tjiortib

se(_pruptily匕英抽玉王DL7:

lt:

S3c

lget_porla

sel_pr<*p.ge1_p&rtsdsetproperty12STAHL77IjS33^getportsw

"et_pmpertyI?

S7AIDAEDI.7CM-S37

.get_portcx

iel-pi'optrlyI二工抽證恥L/rM'SSJl_pailayse1_propcrtyI3S7AOEDL'OSS3z^get.portsz

实验现象:

成功完成BCD码转余三码,与预期现象相符。

实验结论:

通过对实验现象的分析,得出代码与门电路图的结合很好的印证了真值表。