飞思卡尔第二章.docx

《飞思卡尔第二章.docx》由会员分享,可在线阅读,更多相关《飞思卡尔第二章.docx(53页珍藏版)》请在冰点文库上搜索。

飞思卡尔第二章

第二章相关常用寄存器介绍

2.1输入输出控制寄存器

1.端口A、B数据寄存器(PTAD、PTBD)

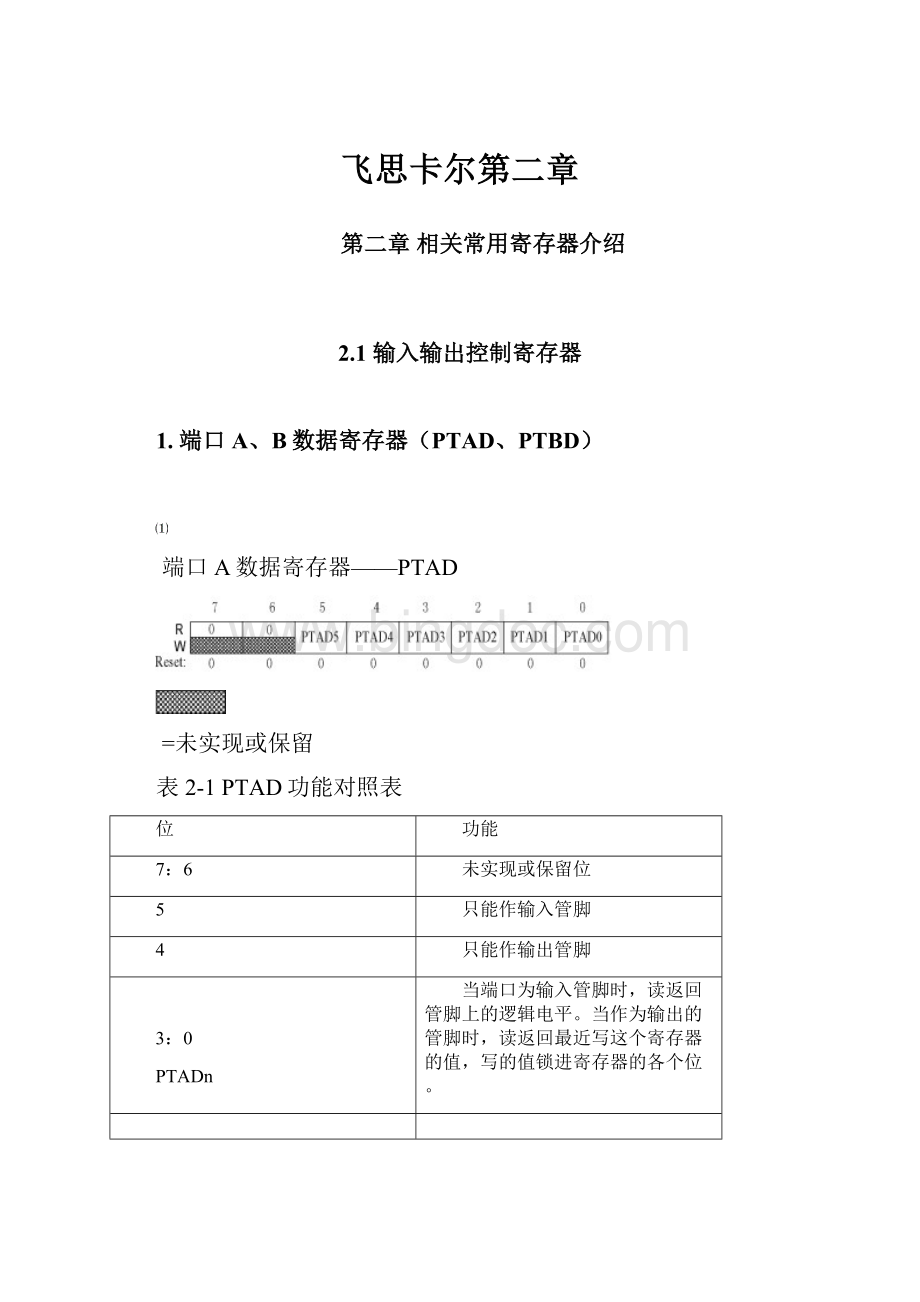

端口A数据寄存器——PTAD

=未实现或保留

表2-1PTAD功能对照表

位

功能

7:

6

未实现或保留位

5

只能作输入管脚

4

只能作输出管脚

3:

0

PTADn

当端口为输入管脚时,读返回管脚上的逻辑电平。

当作为输出的管脚时,读返回最近写这个寄存器的值,写的值锁进寄存器的各个位。

端口B数据寄存器——PTBD

表2-2PTBD功能对照表

位

功能

7:

0

PTBDn

当端口为输入管脚时,读返回管脚上的逻辑电平。

当作为输出的管脚时,读返回最近写这个寄存器的值,写的值锁进寄存器的各个位。

2.端口A、B数据方向寄存器(PTADD、PTBDD)

端口A数据方向寄存器——PTADD

表2-3PTADD功能对照表

位

功能

5:

4

PTA5只能作输入管脚,PTA4只能作输出管脚

3:

0

PTADDn

1——使能为输出管脚

0——使能为输入管脚

端口B数据方向寄存器——PTBDD

表2-4PTBDD功能对照表

位

功能

7:

0

PTBDDn

1—使能为输出管脚

0—使能为输入管脚

3.端口A、B内部上拉使能寄存器(PTAPE、PTBPE)

端口A内部上拉使能寄存器——PTAPE

表2-5PTAPE功能对照表

位

功能

5:

0

PTAPEn

0—屏蔽端口A第n位的内部上拉功能。

1—使能端口A第n位的内部上拉功能。

PTAPE4对只能作为输出口的PTA4管脚没有影响。

端口B内部上拉使能寄存器——PTBPE

表2-6PTBPE功能对照表

位

功能

7:

0

0—屏蔽端口B第n位的内部上拉功能。

1—使能端口B第n位的内部上拉功能。

2.2键盘中断寄存器

1.KBI状态和控制寄存器(KBISC)

表2-7KBISC寄存器功能对照表

位

功能

7:

4

未用到寄存器位,读总为0。

3

KBF

键盘中断标志——KBF指示一个键盘中断是否被检测到。

对KBF写操作没有影响。

0—没有检测到键盘中断

1—检测到键盘中断

2

KBACK

键盘应答——写1到KBACK是标志清除机制的一部分,KBACK读时总为0。

1

KBIE

键盘中断使能——KBIE确定一个键盘中断是否允许请求。

0—键盘中断请求没有使能

1—键盘中断请求使能

0

KBIMOD

键盘检测模式——KBMOD(与BKEDG位一起)控制键盘中断管脚的检测模式。

0—键盘只检测边沿

1—键盘检测边沿和电平

2.KBI管脚使能寄存器(KBIPE)

表2-8KBIPE寄存器功能对照表

位

功能

7:

0

KBIPEn

键盘管脚使能——每个KBIPEn位使能对应的键盘中断管脚

0—管脚没有使能键盘中断功能

1—管脚使能键盘中断功能

3.KBI沿选择寄存器(KBIES)

表2-9KBIES寄存器功能对照表

位

功能

7:

0

KBEDGn

键盘沿选择——每个KBEDGn位选择相应管脚的下降沿/低电平或者上升沿/高电平功能

0—下降沿/低电平(触发中断)

1—上升沿/高电平(触发中断)

2.3定时器寄存器

1.八位定时模块——MTIM

MTIM状态与控制寄存器——MTIMSC

表2-10MTIMSC寄存器功能对照表

位

功能

7

TOF

定时器溢出标志——当计数器计数到与辅助寄存器MTIMMOD数值相等,并翻转到0时,该只读溢出标志TOF会被置“1”。

该溢出标志的清除方法有三种:

1〉当TOF为“1”时,读MTIMSC,并给TOF重新写入“0”;

2〉

3〉写“1”给TRST;

4〉

5〉给辅助寄存器MTIMMOD写入任何数值。

6

TOIE

溢出中断允许——如果该位设置为“1”,则当TOF置位时会产生中断。

当TOF为“1”时不要设置该允许位,一般的做法是先清除TOF,然后再设置TOIE。

即使该位没有设置,还是可以通过软件查询TOF的方法使用定时器的。

5

TRST

定时器复位设置——该位只能写入,读出总为0,而且写0没有影响,写1时导致计数器为0x00,同时TOF也清零。

4

TSTP

定时器停止设置——当该位置“1”,会使计数器停止计数,计数数值保持不变,当清除该位时,计数器从当前数值继续计数。

3:

0

未使用,读出总为0

MTIM时钟配置寄存器——MTIMCLK

表2-11MTIMCLK寄存器功能对照表

位

功能

7:

6

未使用,读出总为0

5:

4

CLKS

计数器时钟源选择——通过该两位设置,在四种时钟源中选择其一,改变时钟源时不会影响计数器计数,时钟源切换后,计数器会在新的时钟下继续计数。

00—选择总线时钟(BUSCLK);

01—固定频率时钟(XCLK);

10—外部时钟TCLK的下降沿;

11—外部时钟TCLK的上升沿。

3:

0

PS

时钟预分频器——该4位设置计数器输入时钟的预分频数,改变分频数不影响计数器计数,分频数切换后,计数器会在新的分频数下计数。

0000—分频数为1;0001—分频数为2;0010—分频数为4;

0011—分频数为8;0100—分频数为16;0101—分频数为32;

0110—分频数为64;0111—分频数为128;

大于等于1000—分频数为256。

MTIM计数器——MTIMCNT

该计数器为只读,写入任何数值对其没有影响,复位时为0x00。

MTIM模寄存器——MTIMMOD

该8位可读写的寄存器保存的数值是计数器计数的最大值,当计数器计数到该最大值时会翻转到0,同时设置TOF标志。

如果给该寄存器写入数值0x00,会导致计数器成为一个没有约束的自由运行的计数器,给MTIMMOD写入数值回导致计数器回0x00,而且溢出标志TOF也会清零。

MTIMMOD复位时为0x00。

2.十六位定时模块——TPM

TPM状态与控制寄存器——TPMSC

表2-12TPMSC寄存器功能对照表

位

功能

7

TOF

定时器溢出标志——当计数器计数到模寄存器数值并翻转到0x0000时,该标志置1。

当定时器设置为中间对齐的PWM(CPWM)工作模式时,计数器计数到模寄存器数值并开始减1时,该溢出标志置1。

清除该标志分成两步,先读TPMSC,然后对TOF写0,如在这两步之间有其它定时器溢出,则清除动作取消。

复位时清除TOF,对TOF写1没有影响。

6

TOIE

定时器中断允许——该读/写位控制定时器的溢出中断。

当TOIE设置为1时,如果TOF为1会产生中断。

TOIE为0时,还是可以通过软件查询TOF的方法使用定时器的。

5

CPWMS

中间对齐PWM模式选择位——如果该位为0,定时器工作在加法计数器方式,此时计数器的独立通道可以工作在输入捕捉、输出比较和沿对齐PWM模式。

该位设置为1,将使得定时器工作在加/减计数器方式,而且所有通道都必须工作在中间对齐的PWM模式下。

该位复位时为0。

4:

3

CLKS[B:

A]

定时器时钟源选择位——该2位的设置可能停止定时器,也可能选择3种时钟源之一作为定时器的输入。

00—没有时钟输入,定时器停止;01—总线时钟BUSCLK;

10—固定系统时钟XCLK;11—外部输入时钟TPMCLK。

2:

0

PS[2:

0]

时钟预分频设置——该3位设置定时器的分频器,对应关系如下:

000—1分频;001—2分频;010—4分频;011—8分频;

100—16分频;101—32分频;110—64分频;111—128分频。

TPM计数器——TPMCNTH:

TPMCNTL

TPM计时寄存器高位TPMCNTH:

TPM计时寄存器低位TPMCNTL:

这是两个只读的8位寄存器,而且读取任何一个寄存器都会将这两个寄存器数值保存在某个缓冲中,直到另一个寄存器也被读取,至于哪个寄存器先被读取并不重要。

该自动缓冲机制通过以下3种方法可以重新进入准备状态:

1〉MCU复位;2〉对计数器TPMCNTH或TPMCNTL写入任何数值;3〉对状态和控制寄存器TPMSC写入任何数值。

定时器模寄存器——TPMMODH:

TPMMODL

TPM模寄存器高位TPMMODH:

TPM模寄存器低位TPMMODL:

该可读/写寄存器定义了计数器的最大数值,当计数器计数到与模寄存器数值相等时,对于加法计数器(CPWMS=0)则翻转到0x0000,对于加/减计数器(CPWMS=1),计数器开始递减。

此时溢出标志TOF会被置1。

对模寄存器的某个8位写入数值时会禁止TOF设置,同时也禁止了中断,直到另一个8位寄存器写入新值。

复位时0x0000,此时如果启动定时器则计数器成为“自由计数器”。

对模寄存器的更新操作最好在定时器溢出中断中进行,这样比较容易保证在新的溢出之前,两个8位的寄存器数值更新已经完成。

另外一个好的习惯就是在对模寄存器第一次写入数值前,先复位主计数器,以保证第一次溢出不会太快。

定时器通道n(n为0或1)对应的状态与控制寄存器——TPMCnSC

表2-13TPMCnSC寄存器功能对照表

位

功能

7

CHnF

通道n的中断标志——如果通道n设置为输入捕捉,当外部管脚出现有效边沿,则该中断标志。

当通道n设置为输出比较或是边沿对齐的PWM工作模式,当TPM计数器数值与通道n辅助寄存器数值一致时。

对于中间对齐的PWM工作模式来说,该标志一般不使用,因为在一个周期中,脉冲有效的两个沿都会设置该标志(有两次比较匹配事件)。

如果通道n对应的中断被允许(CHnIE=1),则标志CHnF置1时会产生中断。

清除CHnF标志分两步,先读取TPMCnSC,然后对CHnF写0。

在这两步之间如果有事件发生,需要设置CHnF,则清除标志的动作取消。

对该标志写1没有影响。

6(CHnIE)

通道n中断允许——置1该控制位将允许通道n的中断。

5:

4

MSnB:

MSnA

通道工作模式选择控制位,MSnB决定对应的通道是否设置为PWM模式,而MSnA决定通道在不是PWM模式时,是输入捕捉还是输出比较。

更详细用法参见表2-14。

3:

2

ELSnB:

ELSnA

沿/电平选择控制位——设置通道对应的外部管脚工作模式,具体用法参见表2-14。

该控制位的设置需要参考其它三个控制位[CPWMS:

MSnB:

MSnA],对于输入捕捉而言,该控制选择上升沿还是下降沿,而对于输出比较而言,该控制选择比较匹配时,外部管脚被驱动成高电平还是低电平,对于PWM而言,该控制决定了脉宽有效期间对应外部管脚的电平状态。

设置该两位为[0:

0]时使得通道对应的外部管脚为通用I/O,该特性可用于临时取消输入捕捉功能,或者是通道设置成不需要外部管脚的软件定时器时,将对应的管脚作为通用I/O使用。

对于TPMCH0被设置成外部脉冲输入管脚时,通道0对应的该控制位必须设置成[0:

0]。

1:

0

未使用的保留位。

表2-14通道模式对照表

CPWMS

MSnB:

MSnA

ELSnB:

ELSnA

模式

功能

x

xx

00

通道未使用外部管脚,可能是管脚作为TPM的外部时钟输入或者是将管脚作为通用I/O使用。

0

00

01

10

11

输入捕捉

仅上升沿捕捉

仅下降沿捕捉

上升沿或下降沿都捕捉

01

00

01

10

11

输出比较

仅软件比较,无管脚输出

比较匹配时,外部管脚翻转

比较匹配时,外部管脚清0

比较匹配时,外部管脚置1

1x

10

x1

边沿对齐PWM

脉宽有效期间高电平(比较匹配时,外部管脚清0)

脉宽有效期间低电平(比较匹配时,外部管脚置1)

1

xx

10

x1

中间对齐PWM

脉宽有效期间高电平(比较匹配时,外部管脚清0)

脉宽有效期间低电平(比较匹配时,外部管脚置1)

2个独立通道对应的定时器通道数值寄存器——TPMCnVH:

TPMCnVL

定时器通道数值寄存器高位TPMCnVH:

定时器通道数值寄存器高位TPMCnVL:

这些可读/写寄存器用于在输入捕捉模式中保存捕捉的计数器数值,在输出比较和PWM模式中保存与主计数器比较的数值。

复位时这些辅助寄存器被清零。

对这些8位的寄存器读/写采用了自动锁定机制,以保证每次都能读/写一个完整的16位的数值。

该锁定机制对组成16位数值的2个8位寄存器的读/写顺序没有要求,也就是说可以先读/写高8位,也可以先读/写低8位,直到另一个寄存器被读/写,自动解除锁定,也可以通过写TMPCnSC寄存器随时解除锁定状态。

2.4A/D转换寄存器

1.配置寄存器(ADCCFG)

表2-15ADCCFG寄存器功能对照表

位

功能

7

ADLPC

低功耗配置——ADLPC用于控制连续逼近转换器的速度和功耗配置。

在这要求更高采样率时优化功耗。

0—高速配置

1—低功耗配置,减小功耗的同时牺牲最大时钟速度。

6:

5

ADIV

时钟分频选择——ADIV可选择ADC使用的时钟信号分频产生ADCK信号

00—clock分频因子1

01—clock÷2分频因子2

10—clock÷4分频因子4

11—clock÷8分频因子8

4

ADLSMP

采样时间配置——ADLSMP在长和短的采样时间之间选择。

调整采样周期,高阻输入能更精确的采样,低阻输入提高转换速度。

如果不要求高的转换速率,长的采样时间也能在使能连续转换时减小整个电源功耗。

0—短的采样时间

1—长的采样时间

3:

2

MODE

转换模式选择——MODE用于在10位和8位运行之间选择。

00—8位转换(N=8)

01—保留

10—10位转换(N=10)

11—保留

1:

0

ADICLK

输入时钟选择——ADICLK四种输入时钟源选择其一,以产生内部时钟输入至时钟分频器ClockDivide。

00—总线时钟

01—总线时钟除以2

10—副时钟(ALTCLK)MC9S08QG8/4MCU器件中没有使用副时钟ALTCLK

11—异步时钟(ADACK)

2.管脚使能控制寄存器1(APCTL1)

表2-17APCTL1寄存器功能对照表

位

功能

7

ADPC7

管脚控制——ADPC7用于控制通道AD7关联的管脚。

0—使能AD7管脚和I/O控制。

1—屏蔽管脚I/O控制,只有AD7输入功能。

6

ADPC6

管脚控制——ADPC6用于控制通道AD7关联的管脚。

0—使能AD6管脚和I/O控制。

1—屏蔽该管脚I/O控制,只有AD6输入功能。

5

ADPC5

管脚控制——ADPC5用于控制通道AD5关联的管脚。

0—使能AD5管脚和I/O控制。

1—屏蔽该管脚I/O控制,只有AD5输入功能。

4

ADPC4

管脚控制——ADPC4用于控制通道AD7关联的管脚。

0—使能AD4管脚和I/O控制。

1—屏蔽该管脚I/O控制,只有AD4输入功能。

3

ADPC3

管脚控制——ADPC3用于控制通道AD3关联的管脚。

0—使能AD3管脚和I/O控制。

1—屏蔽该管脚I/O控制,只有AD3输入功能。

2

ADPC2

管脚控制——ADPC2用于控制通道AD2关联的管脚。

0—使能AD2管脚和I/O控制。

1—屏蔽该管脚I/O控制,只有AD2输入功能。

1

ADPC1

管脚控制——ADPC1用于控制通道AD1关联的管脚。

0—使能AD1管脚和I/O控制。

1—屏蔽该管脚I/O控制,只有AD1输入功能。

0

ADPC0

管脚控制——ADPC0用于控制通道AD0关联的管脚。

0—使能AD0管脚和I/O控制。

1—屏蔽该管脚I/O控制,只有AD0输入功能。

3.状态控制寄存器(ADCSC1)

表2-18ADCSC1寄存器功能对照表

位

功能

7

COCO

转换结束——COCO只读标志位

1、当比较器被屏蔽(ACFE=0)时,在每次转换结束的时候被设置1。

2、当使用比较器(ACFE=1)时,只有在比较结果为真时,COCO标志在转换结束时被设置1,否则为0。

3、ADCSC1被写或者ADCRL数字结果寄存器被读,此位1被清除。

0—转换没有结束

1—转换结束

6

AIEN

中断使能——AIEN用于转换结束申请中断。

当AIEN=1为高时,COCO=1声明申请中断。

0—屏蔽转换结束申请中断

1—使能转换结束申请中断

5

ADCO

连续转换使能——ADCO用于使能连续转换。

写ADCS1寄存器软件触发;ADHWT产生硬件触发。

0—当选择软件触发运行转换或选择硬件触发运行转换时,进行一次转换。

1—当选择软件触发运行转换或选择硬件触发运行转换时,连续转换。

4-0

ADCH

输入通道选择——ADCH

00000:

INAD000100:

INAD4内部通道自动连接参考电压

00001:

INAD100101:

INAD511101:

VREFH(VDD)

00010:

INAD200110:

INAD611110:

VREFL(VSS)

00011:

INAD300111:

INAD7

*11111:

全为1时,隔离所有的输入通道信号及输入源,转换器子系统关闭,ADC处于低功耗状态。

另:

其他数字组合为保留通道为未知值。

4.状态和控制寄存器(ADCSC2)

表2-19ADCSC2寄存器功能对照表

位

功能

7

ADACT

转换有效性——ADACT指示正在进行中的一个转换状态。

在一个转换开始时,ADACT=1;当一个转换已完成或取消时ADACT=0。

0—转换不在进行中

1—转换在进行中

6

ADTRG

选择转换触发——ADTRG用于ADC选择开始转换的触发类型。

可选择软件触发和硬件触发两种触发类型。

0—选择软件触发,当选择软件触发,写ADCSC1(给寄存器赋初值)。

1—选择硬件触发,当选择硬件触发,引发ADHWT事件。

5

ACFE

比较器使能——ACFE用于启动比较功能.

0—屏蔽比较功能,默认状态屏蔽比较器。

1—使能比较功能,启动比较器。

4

ACFGT

比较器功能使能——ACFGT用于配置比较器在监测的输入转换结果大于等于或小于比较值时被触发比较功能。

默认被监测的转换结果小于比较值时触发。

0—当输入小于比较数字电平时触发。

1—当输入大于或等于比较数字电平时触发。

5.数据结果寄存器(ADCRH、ADCRL)

数据结果高位寄存器ADCRH:

数据结果低位寄存器ADCRL:

用于储存转换结果,属于只读寄存器,ADCRH在10位转换结果的情况下使用,用于储存转换结果的高两位。

6.比较值寄存器(ADCCVH、ADCCVL)

比较值高位寄存器ADCCVH:

比较值低位寄存器ADCCVL:

7.实时中断寄存器(SRTISC)

表2-20SRTISC寄存器功能对照表

位

功能

7

RTIF

实时中断标志——这个只读状态位指示周期唤醒定时器时间溢出

0—周期唤醒定时器还未时间溢出

1—周期唤醒定时器已经时间溢出

6

RTIACK

实时中断应答——这个只写位用来应答实时中断请求(写1清除RTIF).写0没有意义和影响.读总是返回0

5

RTICLKS

实时中断时钟选择——这个读/写位选择实时中断的时钟源

0—实时中断请求时钟源为内部1kHz振荡器

1—实时中断请求时钟源为外部时钟

4

RTIE

实时中断使能——这个读/写位使能实时中断

0—屏蔽实时中断

1—使能实时中断

2:

0

RTIS

选择实时中断延迟——这些读/写位选择RTI的周期.参看表2-21

表2-21实时中断周期表

RTIS2:

RTIS1:

RTIS0

使用内部1kHz时钟源

(*1*2)

使用外部时钟源

Period=text(*3)

0:

0:

0

屏蔽RTI

DisableRTI

0:

0:

1

8ms

text×256

0:

1:

0

32ms

text×1024

0:

1:

1

64ms

text×2048

1:

0:

0

128ms

text×4096

1:

0:

1

256ms

text×8192

1:

1:

0

512ms

text×16384

1:

1:

1

1.024s

text×32768

列中所示值基于tRTI=1ms

初始的RTI时间溢出周期比规定时间少一个1kHz时钟周期

text是外部晶体频率的周期

2.5异步串行通信SCI寄存器

1.SCI波特率寄存器(SCIBDH,SCIBDL)

SCI波特率高位寄存器SCIBDH:

SCI波特率低位寄存器SCIBDL:

波特率的计算公式是:

Baudrate=Busclk/(16*BR)

这里Baudrate是指波特率,它的单位是bit/sec;Busclk是指总线时钟频率,它的默认值是4MHz;BR是指由[BR12:

BR0]计算出的十进制的分频值,它的范围是0-8191。

2.SCI控制寄存器1(SCIC1)

表2-22SCIC1寄存器功能对照表

位

功能

7

LOOPS

0—正常操作,RxD和TxD使用不同的管脚。

1—循环模式或单线模式,发送器输出内部连接于接收器输入。

6

SCISWAI

0—在等待模式下,SCI时钟继续运动,因而SCI可以作为唤醒CPU中断的源。

1—当CPU处于等待模式时,SCI时钟停止。

5

RSRC

接收器源选择——只有LOOPS位被设置为1,该位才有意义或有效。

当LOOPS=1时,接收器输入与发送器输出内部连接。

RSRC的作用是确定此连接是否与TxD管脚连接。

0—此时LOOPS=1,RSRC=0选择内部回送模式,TxD管脚不与发送器输出和接收器输入连接。

1—此时LOOPS=1,RSRC=1为单线SCI模式,TxD管脚与发送器输出和接收器输入连接。

4

M

0—正常,起始