vhdleda序列信号发生器与检测器设计.docx

《vhdleda序列信号发生器与检测器设计.docx》由会员分享,可在线阅读,更多相关《vhdleda序列信号发生器与检测器设计.docx(12页珍藏版)》请在冰点文库上搜索。

vhdleda序列信号发生器与检测器设计

实验三序列信号发生器与检测器设计

1、实验目的

1.学习一般有限状态机的设计;

2.利用状态机实现串行序列的输出与序列的检测。

3.继续学习优化设计。

2、内容与要求

利用状态机设计实现实现串行序列的输出与序列的检测,具体要求:

1.先设计序列发生器产生序列;

2.再设计一个序列信号检测器,若系统检测到串行序列11010则输出为“1”,否则输出为“0”,并将检测到的11010数目显示出来;

3.对所设计的电路进行波形仿真和硬件测试;

4.整个工程采用顶层文件+底层模块的原理图或文本的设计思路。

3、设计思路/原理图

“1”,没有检测到则输出“0”,并且将检测到的信号的显示出来。

为简化设计,整个工程采用顶层文件+底层模块的设计方法。

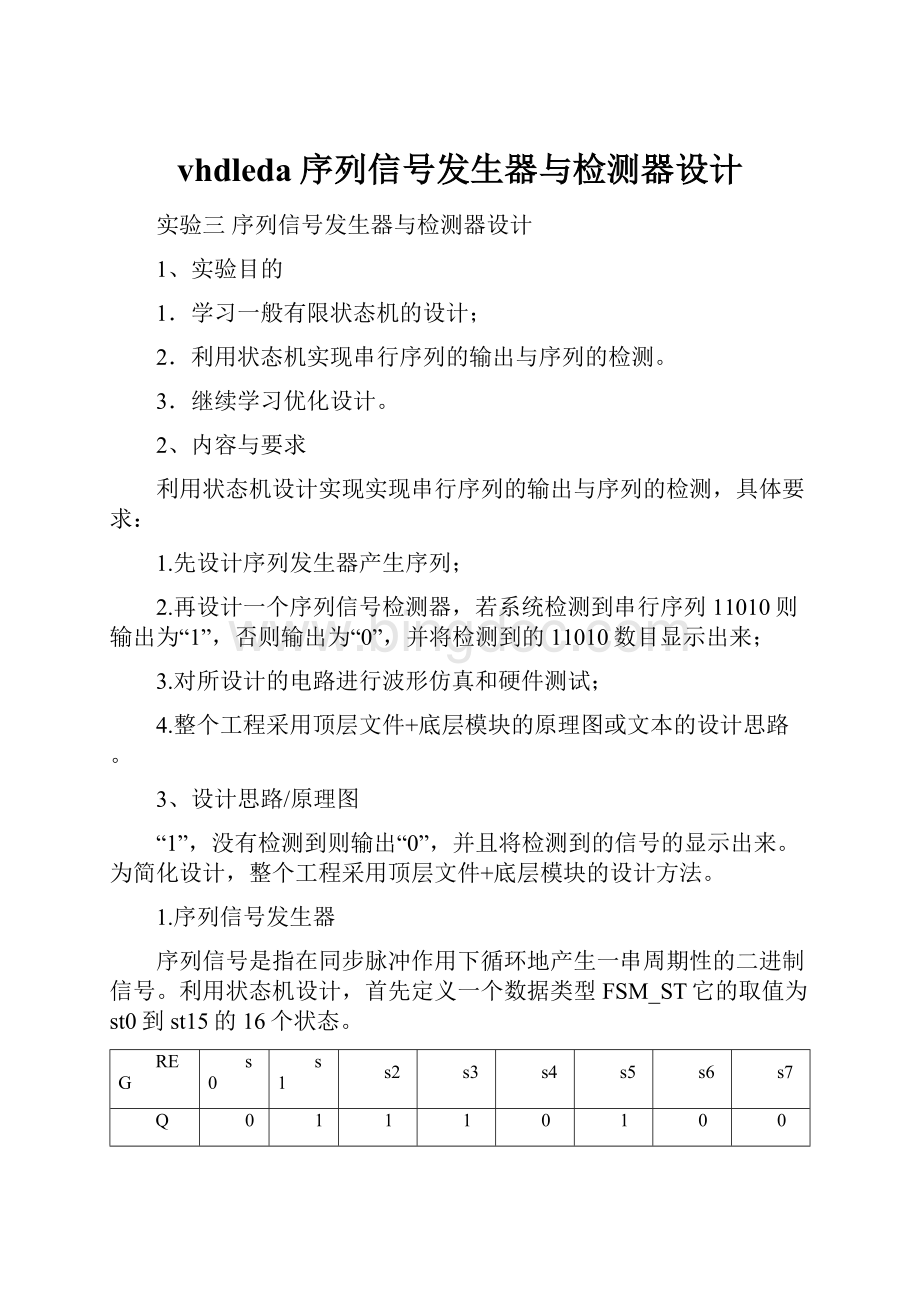

1.序列信号发生器

序列信号是指在同步脉冲作用下循环地产生一串周期性的二进制信号。

利用状态机设计,首先定义一个数据类型FSM_ST它的取值为st0到st15的16个状态。

REG

s0

s1

s2

s3

s4

s5

s6

s7

Q

0

1

1

1

0

1

0

0

REG

s8

s9

s10

s11

s12

s13

s14

s15

Q

1

1

0

1

1

0

1

0

2、序列检测器

序列检测器设计的关键在于正确码的收到必须是连续的,这就要求检测器必须记住前一次的正确码及序列,直到在连续的检测中收到的每一位码都与预置码相同。

在此,必须利用状态转移图。

定义预置信号D=“11010”,电路需要分别不间断记忆:

初始状态、1、11、110、1101、11010共六种状态,状态转移图:

3、计数模块

利用序列检测器产生的信号(1和0)作为计数器模块的时钟信号,产生的信号0、1变化,形成类似的CLK信号,实现计数模块计数。

计数模块设计可采用前面的实验二设计。

4.顶层设计

为简化设计,顶层设计采用原理图输入法设计,直接将模块进行连接。

4、实验程序(陈杰独立编写)

序列信号发生器:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYC_OUTIS

PORT(CLK,RST:

INSTD_LOGIC;

CO:

OUTSTD_LOGIC);

ENDC_OUT;

ARCHITECTUREbehavOFC_OUTIS

TYPEFSM_STIS(s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13,s14,s15);

SIGNALREG:

FSM_ST;

SIGNALQ:

STD_LOGIC;

BEGIN

PROCESS(CLK,RST)

BEGIN

IFRST='1'THENREG<=s0;Q<='0';

ELSIFCLK'EVENTANDCLK='1'THEN

CASEREGIS

WHENs0=>Q<='0';REG<=s1;

WHENs1=>Q<='1';REG<=s2;

WHENs2=>Q<='1';REG<=s3;

WHENs3=>Q<='1';REG<=s4;

WHENs4=>Q<='0';REG<=s5;

WHENs5=>Q<='1';REG<=s6;

WHENs6=>Q<='0';REG<=s7;

WHENs7=>Q<='0';REG<=s8;

WHENs8=>Q<='1';REG<=s9;

WHENs9=>Q<='1';REG<=s10;

WHENs10=>Q<='0';REG<=s11;

WHENs11=>Q<='1';REG<=s12;

WHENs12=>Q<='1';REG<=s13;

WHENs13=>Q<='0';REG<=s14;

WHENs14=>Q<='1';REG<=s15;

WHENs15=>Q<='0';REG<=s0;

WHENOTHERS=>REG<=s0;Q<='0';

ENDCASE;

ENDIF;

ENDPROCESS;

CO<=Q;

ENDbehav;

转化成可调用的元件:

序列信号检测器:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYSCHKIS

PORT(DIN,CLK,CLR:

INSTD_LOGIC;

SS:

OUTSTD_LOGIC);

ENDSCHK;

ARCHITECTUREbehavOFSCHKIS

SIGNALQ:

INTEGERRANGE0TO5;

SIGNALD:

STD_LOGIC_VECTOR(4DOWNTO0);

BEGIN

D<="11010";

PROCESS(CLK,CLR)

BEGIN

IFCLR='1'THENQ<=0;

ELSIFCLK'EVENTANDCLK='1'THEN

CASEQIS

WHEN0=>IFDIN=D(4)THENQ<=1;ELSEQ<=0;ENDIF;

WHEN1=>IFDIN=D(3)THENQ<=2;ELSEQ<=0;ENDIF;

WHEN2=>IFDIN=D

(2)THENQ<=3;ELSEQ<=2;ENDIF;

WHEN3=>IFDIN=D

(1)THENQ<=4;ELSEQ<=0;ENDIF;

WHEN4=>IFDIN=D(0)THENQ<=5;ELSEQ<=2;ENDIF;

WHENOTHERS=>Q<=0;

ENDCASE;

ENDIF;

ENDPROCESS;

PROCESS(Q)

BEGIN

IFQ=5THENSS<=‘1’;

ELSESS<=‘0’;

ENDIF;

ENDPROCESS;

ENDbehav;

转化成可调用的元件:

计数模块

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCOUNTIS

PORT(CLK,EN,RST:

INSTD_LOGIC;

Q1:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

Q2:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

COUT:

OUTSTD_LOGIC);

ENDENTITYCOUNT;

ARCHITECTUREONEOFCOUNTIS

BEGIN

PROCESS(CLK,EN,RST)

VARIABLECQI:

STD_LOGIC_VECTOR(7DOWNTO0);

BEGIN

IFRST='1'THENCQI:

=(OTHERS=>'0');

ELSIFCLK'EVENTANDCLK='1'THEN

IFEN='1'THEN

IFCQI<153THEN

IFCQI(3DOWNTO0)=9THENCQI:

=CQI+7;--高位进位

ELSECQI:

=CQI+1;

ENDIF;

ELSECQI:

=(OTHERS=>'0');

ENDIF;

ENDIF;

ENDIF;

IFCQI=153THENCOUT<='1';

ELSECOUT<='0';

ENDIF;

Q1<=CQI(3DOWNTO0);

Q2<=CQI(7DOWNTO4);

ENDPROCESSCOUNT;

ENDARCHITECTUREONE;

转化成可调用的元件:

顶层文件(原理图法):

第二种方法(任意序列,任意检测):

实验程序如下:

libraryieee;

useieee.std_logic_1164.all;

entityjiance11010is

port(datain,clk:

instd_logic;

t:

instd_logic_vector(4downto0);

q:

outstd_logic;

cq:

outstd_logic_vector(4downto0));

endjiance11010;

architecturert1ofjiance11010is

signalreg:

std_logic_vector(4downto0);

begin

process(clk)

variablet1:

std_logic_vector(4downto0);

begin

ifclk'eventandclk='1'then

reg(0)<=datain;

reg(4downto1)<=reg(3downto0);

endif;

t1:

=t;

ifreg=t1thenq<='1';

elseq<='0';

cq<=reg;

endif;

endprocess;

endrt1;

基于实验发现序列一个一个输入比较麻烦所以设计如下任意十六位循环系列:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYjcIS

PORT(CLK,CLR,RESET:

INSTD_LOGIC;

B:

instd_logic_vector(15downto0);

q:

outstd_logic);

ENDENTITY;

ARCHITECTUREONEOFjcIS

SIGNALA:

STD_LOGIC;

BEGIN

PROCESS(CLK,CLR)

VARIABLEN:

INTEGERRANGE16DOWNTO1;

BEGIN

IFRESET='1'THENN:

=1;

ELSIFCLK'EVENTANDCLK='1'

THENCASENIS

WHEN1=>A<=B(0);N:

=N+1;

WHEN2=>A<=B

(1);N:

=N+1;

WHEN3=>A<=B

(2);N:

=N+1;

WHEN4=>A<=B(3);N:

=N+1;

WHEN5=>A<=B(4);N:

=N+1;

WHEN6=>A<=B(5);N:

=N+1;

WHEN7=>A<=B(6);N:

=N+1;

WHEN8=>A<=B(7);N:

=N+1;

WHEN9=>A<=B(8);N:

=N+1;

WHEN10=>A<=B(9);N:

=N+1;

WHEN11=>A<=B(10);N:

=N+1;

WHEN12=>A<=B(11);N:

=N+1;

WHEN13=>A<=B(12);N:

=N+1;

WHEN14=>A<=B(13);N:

=N+1;

WHEN15=>A<=B(14);N:

=N+1;

WHEN16=>A<=B(15);N:

=1;

WHENOTHERS=>NULL;

ENDCASE;

ENDIF;

Q<=A;

ENDPROCESS;

ENDARCHITECTURE;

五、实验步骤

1.建立工作库文件夹和编辑模块设计文件

(1)在D盘下建立一个文件夹保存工程文件;

(2)打开QuartusII,建立新的VHDL文件,在设计有顶层和底层文件时,

在打开的页面下输入模块设计程序。

并且生成可调用文件,输入完程序之后逐个编译,注意必须先设为顶层文件,逐个编译无错之后将模块转换为可调用元件。

顶层原理图设计和工程编译,新建原理图文件,调用模块文件连接电路,完成顶层设计。

新建工程并对工程进行全程编译。

4.系统仿真

(1)建立新的波形文件;

(2)在波形编辑器窗口添加节点,通过Edit->EndTime来设定仿真结束时间,点击save保存;

(3)通过Tools下的SimulatorTools项进行仿真,然后观察和分析输出波形。

六、实验仿真波形图如下:

A

程序I仿真波形:

1.根据aq右移变化可以看出

2.A点可以看出,检测器检测串行信号11010,若检测到11010信号,ss则输出“1”;没有检测到,ss则输出“0”;

程序II仿真波形:

AB

CDE

1、由cq输出和datain不难看出,datain输入就是序列的输入,从而实现了任意模的输入。

2、由ABCDE五点可以发现当t为不同序列时,程序检测的的系列也不同。

程序可以检测不同的输入序列t。

从而实现了不同系列的检测。

程序III仿真波形:

(1)

(2)

从仿真图

(1)可知,当B输入不同序列时,产生的序列也不同

从仿真图

(2)可知,当B输入一个序列时,输出q无限循环右移输出这个序列

5.引脚锁定和下载测试

1、引脚锁定

在Assigments菜单中选择Pins,打开界面后,在Location栏空白处双击鼠标,依次加入端口,引脚设置参照实验书。

确定好引脚后,保存这些信息,然后再进行编译。

七、硬件测试

程序一、根据电路设计,。

测试结果与电路设计功能符合,证明设计是正确的,稳定的。

程序二:

先设定一个检测序列,然后当给一个手动脉冲时,给一个信号。

当连续输入的信号为检测序列时,接q的LED发亮,其他情况不发亮。

改变检测序列,连续输入原来序列,LED等不亮。

硬件测试和程序设计结果相同。

八、实验小结

通过本次实验我学会了利用状态机实现串行序列发生器和检测器的设计,关键是在画出状态图后设计时序进程和组合进程,例如在设计序列发生器时,源程序首先用一个进程对CLK输入脉冲个数进行统计,统计结果存放信号CNT中。

然后用另一个进程根据输入脉冲的统计结果,控制序列信号的输出,当第0个CLK脉冲到来时,输出ZOUT=“1”,当第1个CLK脉冲到来时,ZOUT=“1”,当第2个CLK脉冲到来时,ZOUT=“0”;以此类推,每十六个脉冲为一次循环使输出序列信号为“”。

在设计任意输入任意序列检测时,充分利用软件的特性,只要思路方向正确,也不是什么很复杂的问题。

EDA重在思考,发现,和不断的探索。

九、实验心得

本次实验的目的在于学习一般有限状态机的设计。

状态机包括时序逻辑部分(存储部分)和组合逻辑部分(控制部分),其内部和输出经过一可预测的状态序列。

因此设计状态机一般先根据具体问题明确控制输入、条件转换,再画出状态图,做出状态列表。

利用VHDL设计状态机一般包括时序进程和组合进程两个主要部分常常使用CASE语句,条件的转换则可用CASE中的IF语句。