Verilog HDL 6位数码管扫描驱动汇总.docx

《Verilog HDL 6位数码管扫描驱动汇总.docx》由会员分享,可在线阅读,更多相关《Verilog HDL 6位数码管扫描驱动汇总.docx(11页珍藏版)》请在冰点文库上搜索。

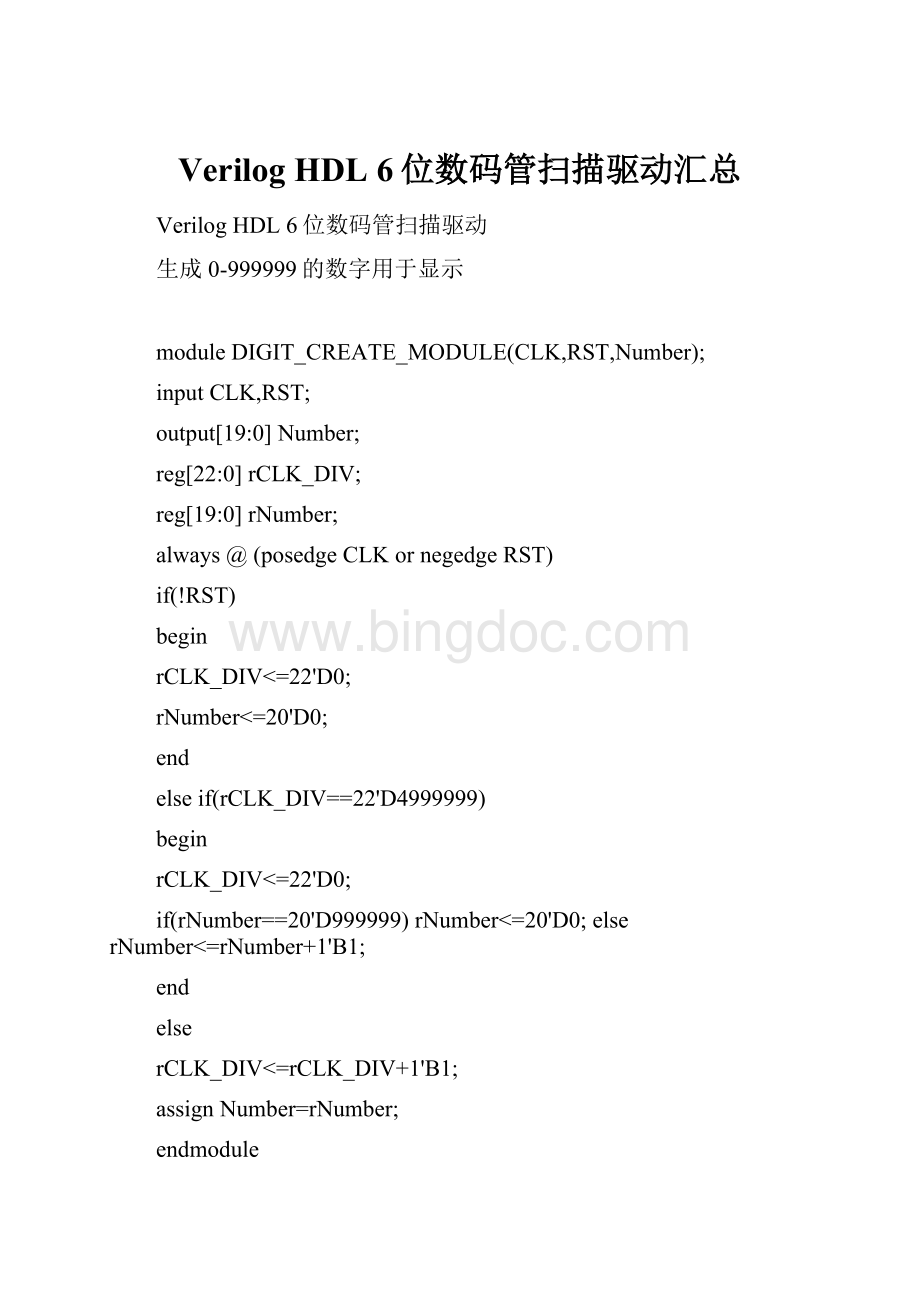

VerilogHDL6位数码管扫描驱动汇总

VerilogHDL6位数码管扫描驱动

生成0-999999的数字用于显示

moduleDIGIT_CREATE_MODULE(CLK,RST,Number);

inputCLK,RST;

output[19:

0]Number;

reg[22:

0]rCLK_DIV;

reg[19:

0]rNumber;

always@(posedgeCLKornegedgeRST)

if(!

RST)

begin

rCLK_DIV<=22'D0;

rNumber<=20'D0;

end

elseif(rCLK_DIV==22'D4999999)

begin

rCLK_DIV<=22'D0;

if(rNumber==20'D999999)rNumber<=20'D0;elserNumber<=rNumber+1'B1;

end

else

rCLK_DIV<=rCLK_DIV+1'B1;

assignNumber=rNumber;

endmodule

数码管驱动

moduleDIGIT_MODULE(CLK,RST,DIG,SEL,BCD0,BCD1,BCD2,BCD3,BCD4,BCD5);

inputCLK,RST;

output[7:

0]DIG;

output[5:

0]SEL;

input[3:

0]BCD0,BCD1,BCD2,BCD3,BCD4,BCD5;

parameterN0=8'B11000000,N1=8'b11111001,N2=8'b10100100,N3=8'b10110000,N4=8'b10011001,

N5=8'B10010010,N6=8'b10000010,N7=8'b11111000,N8=8'b10000000,N9=8'b10010000;

reg[7:

0]rD0,rD1,rD2,rD3,rD4,rD5;

always@(posedgeCLKornegedgeRST)

if(!

RST)

begin

rD0<=N0;

rD1<=N0;

rD2<=N0;

rD3<=N0;

rD4<=N0;

rD5<=N0;

end

else

begin

case(BCD0)

4'D0:

rD0<=N0;

4'D1:

rD0<=N1;

4'D2:

rD0<=N2;

4'D3:

rD0<=N3;

4'D4:

rD0<=N4;

4'D5:

rD0<=N5;

4'D6:

rD0<=N6;

4'D7:

rD0<=N7;

4'D8:

rD0<=N8;

4'D9:

rD0<=N9;

default:

rD0<=N0;

endcase;

case(BCD1)

4'D0:

rD1<=N0;

4'D1:

rD1<=N1;

4'D2:

rD1<=N2;

4'D3:

rD1<=N3;

4'D4:

rD1<=N4;

4'D5:

rD1<=N5;

4'D6:

rD1<=N6;

4'D7:

rD1<=N7;

4'D8:

rD1<=N8;

4'D9:

rD1<=N9;

default:

rD1<=N0;

endcase;

case(BCD2)

4'D0:

rD2<=N0;

4'D1:

rD2<=N1;

4'D2:

rD2<=N2;

4'D3:

rD2<=N3;

4'D4:

rD2<=N4;

4'D5:

rD2<=N5;

4'D6:

rD2<=N6;

4'D7:

rD2<=N7;

4'D8:

rD2<=N8;

4'D9:

rD2<=N9;

default:

rD2<=N0;

endcase;

case(BCD3)

4'D0:

rD3<=N0;

4'D1:

rD3<=N1;

4'D2:

rD3<=N2;

4'D3:

rD3<=N3;

4'D4:

rD3<=N4;

4'D5:

rD3<=N5;

4'D6:

rD3<=N6;

4'D7:

rD3<=N7;

4'D8:

rD3<=N8;

4'D9:

rD3<=N9;

default:

rD3<=N0;

endcase;

case(BCD4)

4'D0:

rD4<=N0;

4'D1:

rD4<=N1;

4'D2:

rD4<=N2;

4'D3:

rD4<=N3;

4'D4:

rD4<=N4;

4'D5:

rD4<=N5;

4'D6:

rD4<=N6;

4'D7:

rD4<=N7;

4'D8:

rD4<=N8;

4'D9:

rD4<=N9;

default:

rD4<=N0;

endcase;

case(BCD5)

4'D0:

rD5<=N0;

4'D1:

rD5<=N1;

4'D2:

rD5<=N2;

4'D3:

rD5<=N3;

4'D4:

rD5<=N4;

4'D5:

rD5<=N5;

4'D6:

rD5<=N6;

4'D7:

rD5<=N7;

4'D8:

rD5<=N8;

4'D9:

rD5<=N9;

default:

rD5<=N0;

endcase;

end

reg[11:

0]rCLK_DIV;

always@(negedgeCLKornegedgeRST)

if(!

RST)

rCLK_DIV<=12'D0;

elseif(rCLK_DIV==12'D3599)

rCLK_DIV<=12'D0;

else

rCLK_DIV<=rCLK_DIV+1'B1;

reg[5:

0]rSEL;

reg[7:

0]rDIG;

always@(negedgeCLKornegedgeRST)

if(!

RST)

begin

rSEL<=6'B111111;

rDIG<=N0;

end

elseif(rCLK_DIV==12'D0)

begin

rSEL<=6'B111110;

rDIG<=rD5;

end

elseif(rCLK_DIV==12'D600)

begin

rSEL<=6'B111101;

rDIG<=rD4;

end

elseif(rCLK_DIV==12'D1200)

begin

rSEL<=6'B111011;

rDIG<=rD3;

end

elseif(rCLK_DIV==12'D1800)

begin

rSEL<=6'B110111;

rDIG<=rD2;

end

elseif(rCLK_DIV==12'D2400)

begin

rSEL<=6'B101111;

rDIG<=rD1;

end

elseif(rCLK_DIV==12'D3000)

begin

rSEL<=6'B011111;

rDIG<=rD0;

end

assignDIG=rDIG;

assignSEL=rSEL;

endmodule

20bit二进制转BCD码

moduleBIN_TO_BCD_MODULE(BIN,BCD0,BCD1,BCD2,BCD3,BCD4,BCD5);

parameterBIT_WIDTH=20;

input[BIT_WIDTH-1:

0]BIN;

output[3:

0]BCD0,BCD1,BCD2,BCD3,BCD4,BCD5;

function[3:

0]LSA3;

input[3:

0]IN;

case(IN)

4'B0000:

LSA3=4'B0000;

4'B0001:

LSA3=4'B0001;

4'B0010:

LSA3=4'B0010;

4'B0011:

LSA3=4'B0011;

4'B0100:

LSA3=4'B0100;

4'B0101:

LSA3=4'B1000;

4'B0110:

LSA3=4'B1001;

4'B0111:

LSA3=4'B1010;

4'B1000:

LSA3=4'B1011;

4'B1001:

LSA3=4'B1100;

default:

LSA3=4'B0000;

endcase

endfunction

wire[3:

0]wA[1:

BIT_WIDTH-3];

wire[3:

0]wB[1:

BIT_WIDTH-3];

assignwA[1]={1'B0,BIN[BIT_WIDTH-1:

BIT_WIDTH-3]};

assignwB[1]=LSA3(wA[1]);

genvargB;

generatefor(gB=2;gB<=BIT_WIDTH-3;gB=gB+1)

begin:

CA

assignwA[gB]={wB[gB-1][2:

0],BIN[BIT_WIDTH-gB-2]};

assignwB[gB]=LSA3(wA[gB]);

end

endgenerate

wire[3:

0]wC[1:

BIT_WIDTH-6];

wire[3:

0]wD[1:

BIT_WIDTH-6];

assignwC[1]={1'B0,wB[1][3],wB[2][3],wB[3][3]};

assignwD[1]=LSA3(wC[1]);

genvargD;

generatefor(gD=2;gD<=BIT_WIDTH-6;gD=gD+1)

begin:

CB

assignwC[gD]={wD[gD-1][2:

0],wB[gD+2][3]};

assignwD[gD]=LSA3(wC[gD]);

end

endgenerate

wire[3:

0]wE[1:

BIT_WIDTH-9];

wire[3:

0]wF[1:

BIT_WIDTH-9];

assignwE[1]={1'B0,wD[1][3],wD[2][3],wD[3][3]};

assignwF[1]=LSA3(wE[1]);

genvargF;

generatefor(gF=2;gF<=BIT_WIDTH-9;gF=gF+1)

begin:

CC

assignwE[gF]={wF[gF-1][2:

0],wD[gF+2][3]};

assignwF[gF]=LSA3(wE[gF]);

end

endgenerate

wire[3:

0]wG[1:

BIT_WIDTH-12];

wire[3:

0]wH[1:

BIT_WIDTH-12];

assignwG[1]={1'B0,wF[1][3],wF[2][3],wF[3][3]};

assignwH[1]=LSA3(wG[1]);

genvargH;

generatefor(gH=2;gH<=BIT_WIDTH-12;gH=gH+1)

begin:

CD

assignwG[gH]={wH[gH-1][2:

0],wF[gH+2][3]};

assignwH[gH]=LSA3(wG[gH]);

end

endgenerate

wire[3:

0]wI[1:

BIT_WIDTH-15];

wire[3:

0]wJ[1:

BIT_WIDTH-15];

assignwI[1]={1'B0,wH[1][3],wH[2][3],wH[3][3]};

assignwJ[1]=LSA3(wI[1]);

genvargJ;

generatefor(gJ=2;gJ<=BIT_WIDTH-15;gJ=gJ+1)

begin:

CE

assignwI[gJ]={wJ[gJ-1][2:

0],wH[gJ+2][3]};

assignwJ[gJ]=LSA3(wI[gJ]);

end

endgenerate

wire[3:

0]wK[1:

BIT_WIDTH-18];

wire[3:

0]wL[1:

BIT_WIDTH-18];

assignwK[1]={1'B0,wJ[1][3],wJ[2][3],wJ[3][3]};

assignwL[1]=LSA3(wK[1]);

genvargL;

generatefor(gL=2;gL<=BIT_WIDTH-18;gL=gL+1)

begin:

CF

assignwK[gL]={wL[gL-1][2:

0],wJ[gL+2][3]};

assignwL[gL]=LSA3(wK[gL]);

end

endgenerate

assignBCD0={wB[BIT_WIDTH-3][2:

0],BIN[0]};

assignBCD1={wD[BIT_WIDTH-6][2:

0],wB[BIT_WIDTH-3][3]};

assignBCD2={wF[BIT_WIDTH-9][2:

0],wD[BIT_WIDTH-6][3]};

assignBCD3={wH[BIT_WIDTH-12][2:

0],wF[BIT_WIDTH-9][3]};

assignBCD4={wJ[BIT_WIDTH-15][2:

0],wH[BIT_WIDTH-12][3]};

assignBCD5={wL[BIT_WIDTH-18][2:

0],wJ[BIT_WIDTH-15][3]};

endmodule