触发器和时序逻辑电路测试题.doc

《触发器和时序逻辑电路测试题.doc》由会员分享,可在线阅读,更多相关《触发器和时序逻辑电路测试题.doc(4页珍藏版)》请在冰点文库上搜索。

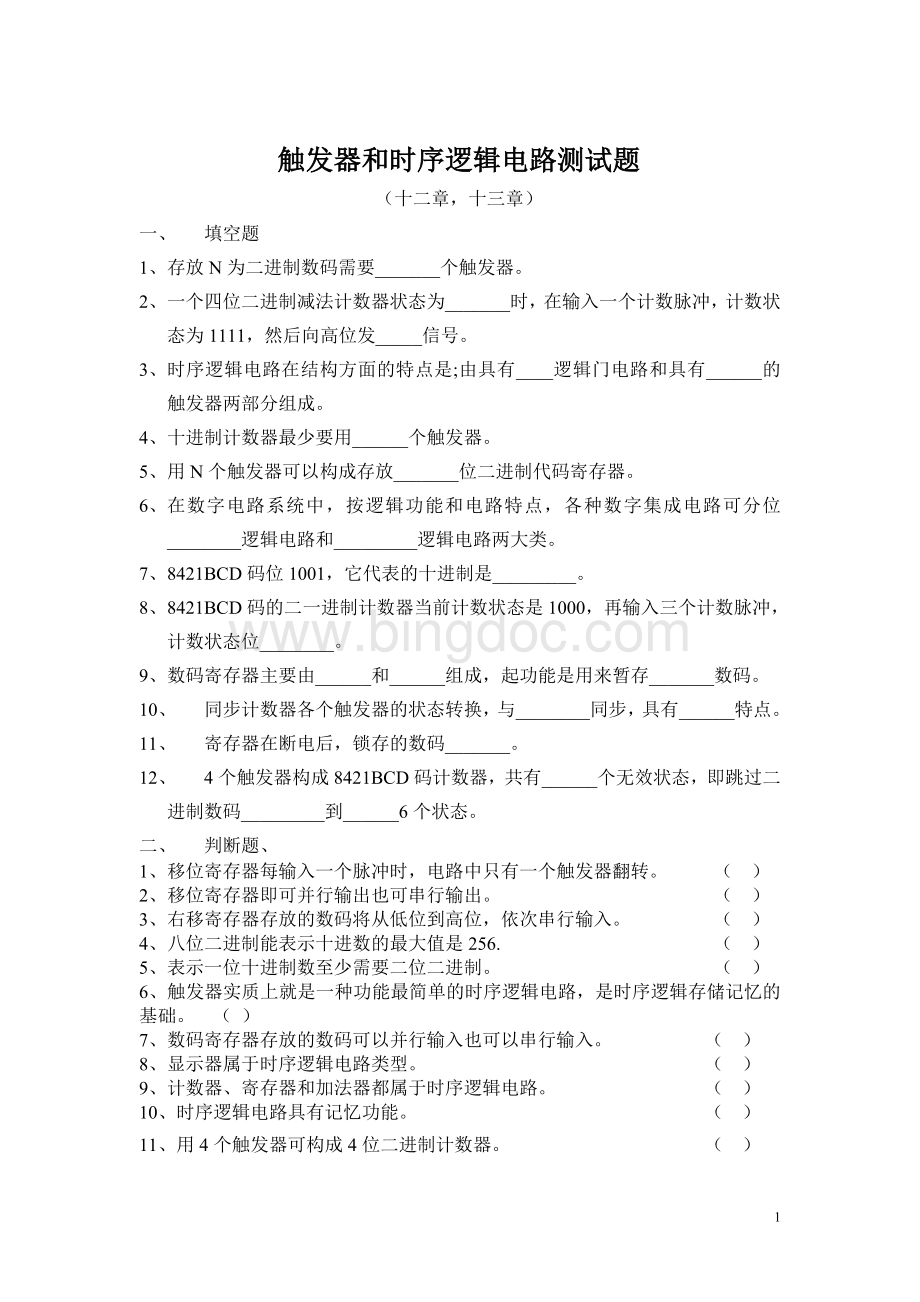

触发器和时序逻辑电路测试题

(十二章,十三章)

一、填空题

1、存放N为二进制数码需要_______个触发器。

2、一个四位二进制减法计数器状态为_______时,在输入一个计数脉冲,计数状态为1111,然后向高位发_____信号。

3、时序逻辑电路在结构方面的特点是;由具有____逻辑门电路和具有______的触发器两部分组成。

4、十进制计数器最少要用______个触发器。

5、用N个触发器可以构成存放_______位二进制代码寄存器。

6、在数字电路系统中,按逻辑功能和电路特点,各种数字集成电路可分位________逻辑电路和_________逻辑电路两大类。

7、8421BCD码位1001,它代表的十进制是_________。

8、8421BCD码的二一进制计数器当前计数状态是1000,再输入三个计数脉冲,计数状态位________。

9、数码寄存器主要由______和______组成,起功能是用来暂存_______数码。

10、同步计数器各个触发器的状态转换,与________同步,具有______特点。

11、寄存器在断电后,锁存的数码_______。

12、4个触发器构成8421BCD码计数器,共有______个无效状态,即跳过二进制数码_________到______6个状态。

二、判断题、

1、移位寄存器每输入一个脉冲时,电路中只有一个触发器翻转。

()

2、移位寄存器即可并行输出也可串行输出。

()

3、右移寄存器存放的数码将从低位到高位,依次串行输入。

()

4、八位二进制能表示十进数的最大值是256.()

5、表示一位十进制数至少需要二位二进制。

()

6、触发器实质上就是一种功能最简单的时序逻辑电路,是时序逻辑存储记忆的基础。

()

7、数码寄存器存放的数码可以并行输入也可以串行输入。

()

8、显示器属于时序逻辑电路类型。

()

9、计数器、寄存器和加法器都属于时序逻辑电路。

()

10、时序逻辑电路具有记忆功能。

()

11、用4个触发器可构成4位二进制计数器。

()

12、同步时序电路由组合电路和触发器两部分组成。

()

13、组合电路不含有记忆功能的器件。

()

14、时序电路不含有记忆功能的器件。

()

15、同步时序电路具有统一的时钟CP控制。

()

16、异步时序电路的各级触发器类型不同。

()

17、时序逻辑电路与组合逻辑电路的最大区别在于,它具有存储和记忆功能。

()

三、选择题

1.下列逻辑电路中为时序逻辑电路的是。

A.变量译码器B.加法器C.数码寄存器D.数据选择器

2.同步时序电路和异步时序电路比较,其差异在于后者。

A.没有触发器B.没有统一的时钟脉冲控制

C.没有稳定状态D.输出只与内部状态有关

3.若要设计一个脉冲序列为1101001110的序列脉冲发生器,应选用个触发器。

A.2B.3C.4D.10

4、对于T触发器,若原态Qn=0,欲使新态Qn+1=1,应使输入T=( )。

A.0 B.1 C.Q D.

5、对于D触发器,欲使Qn+1=Qn,应使输入D=( )。

A.0 B.1 C.Q D.

6、对于JK触发器,若J=K,则可完成( )触发器的逻辑功能。

A.RS B.D C.T D.Tˊ

7、下列触发器中,克服了空翻现象的有( )。

A.边沿D触发器 B.基本RS触发器 C.同步RS触发器 D.主从JK触发器

8、同步计数器和异步计数器比较,同步计数器的优点是( )。

A.工作速度高 B.触发器利用率高 C.电路简单 D.不受时钟CP控制。

9、N个触发器可以构成最大模值为( )的计数器。

A.N B.2N C.N2 D.2N

10、一位8421BCD码计数器至少需要( )个触发器。

A.3 B.4 C.5 D.10

11、采用串行输入/串行输出的8位移位寄存器,时需经( )个脉冲后,8位数码才能全部移出寄存器中。

A.7 B.8 C.15 D.16

四、分析题

1:

触发器和门电路的区别。

2、时序逻辑电路的组成和逻辑功能。

3、分析图P7-1所示时序电路的逻辑功能,设初始状态为Q=0,

4、分析如图P7-3时序逻辑电路的功能,设触发器初始状态为0,试写出:

画出状态转换图时序图和波形图

图P7-3

3题参考答案

解:

(1)D触发器的特性方程:

将各触发器的驱动方程代入,即得电路的状态方程:

(2)计算、列状态表:

(3)画状态图、时序图:

(4)电路功能:

由状态图可以看出,在时钟脉冲CP的作用下,电路的8个状态按递减规律循环变化,即:

000→111→110→101→100→011→010→001→000→…电路具有递减计数功能,是一个3位二进制异步减法计数器。

4