STM32FProgrammingManual.docx

《STM32FProgrammingManual.docx》由会员分享,可在线阅读,更多相关《STM32FProgrammingManual.docx(26页珍藏版)》请在冰点文库上搜索。

STM32FProgrammingManual

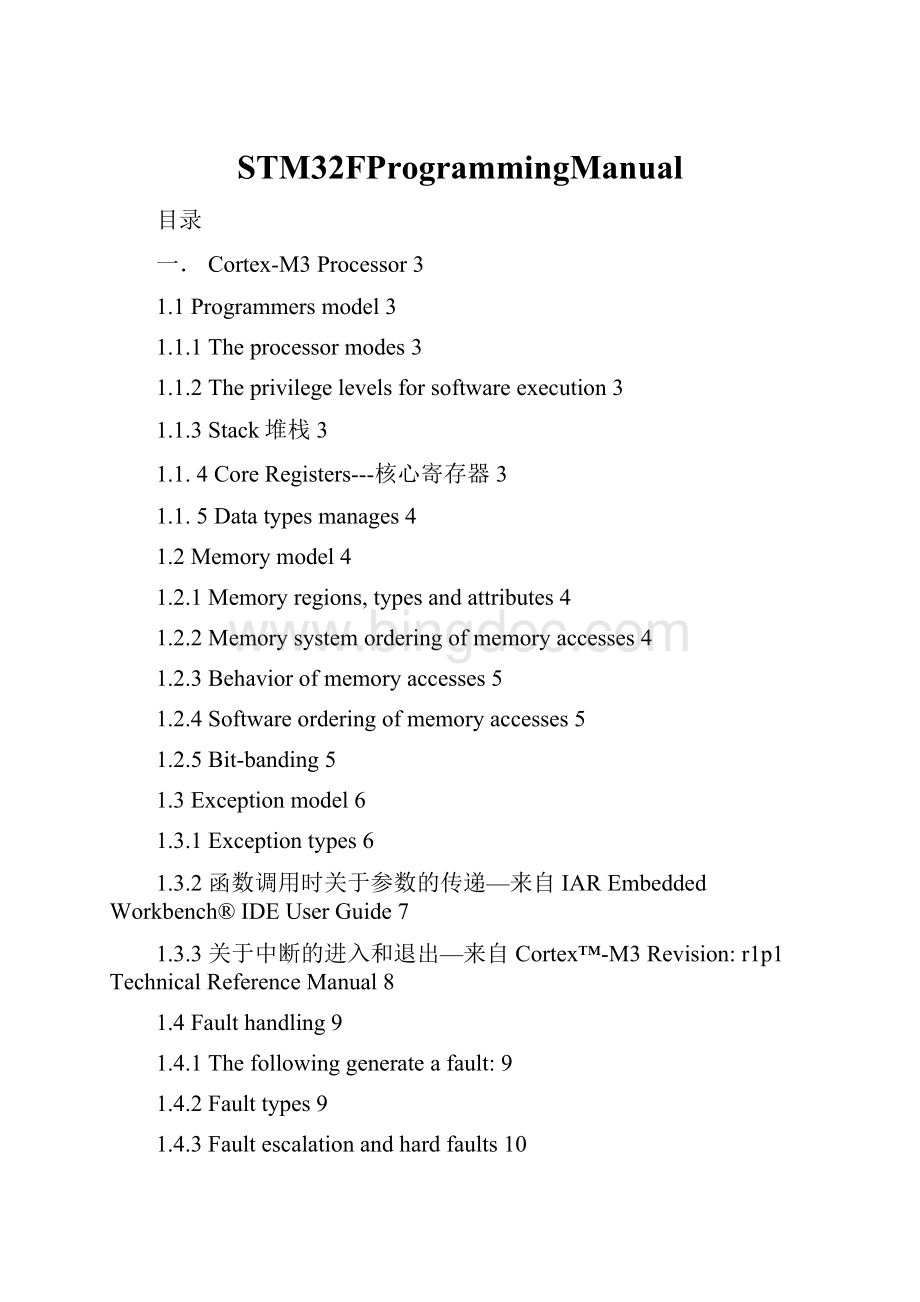

目录

一.Cortex-M3Processor3

1.1Programmersmodel3

1.1.1Theprocessormodes3

1.1.2Theprivilegelevelsforsoftwareexecution3

1.1.3Stack堆栈3

1.1.4CoreRegisters---核心寄存器3

1.1.5Datatypesmanages4

1.2Memorymodel4

1.2.1Memoryregions,typesandattributes4

1.2.2Memorysystemorderingofmemoryaccesses4

1.2.3Behaviorofmemoryaccesses5

1.2.4Softwareorderingofmemoryaccesses5

1.2.5Bit-banding5

1.3Exceptionmodel6

1.3.1Exceptiontypes6

1.3.2函数调用时关于参数的传递—来自IAREmbeddedWorkbench®IDEUserGuide7

1.3.3关于中断的进入和退出—来自Cortex™-M3Revision:

r1p1TechnicalReferenceManual8

1.4Faulthandling9

1.4.1Thefollowinggenerateafault:

9

1.4.2Faulttypes9

1.4.3Faultescalationandhardfaults10

1.5软件中断实现总结10

1.6等级控制11

二.Coreperipherals13

2.1STM32coreperipheralregisterregions13

2.2MemoryProtectionUnit-----MPU13

2.2.1MPUaccesspermissionattributes13

2.2.2MPUmismatch13

2.2.3UpdatinganMPUregion14

2.2.4MPUdesignhintsandtips----MPU使用关键和注意点—重要14

2.3Nestedvectoredinterruptcontroller(NVIC)15

2.3.1TheCMSISmappingoftheCortex-M3NVICregisters15

2.3.2详细寄存器15

2.3.3Level-sensitiveandpulseinterrupts16

2.3.4NVICdesignhintsandtips16

4.4Systemcontrolblock(SCB)16

4.4.1整体16

4.4.2寄存器介绍:

17

4.4.3Systemcontrolblockdesignhintsandtips18

4.5SysTicktimer(STK)18

4.5.1寄存器18

4.5.2SysTickdesignhintsandtips18

一.Cortex-M3Processor

1.1Programmersmodel

1.1.1Theprocessormodes

Threadmode---线程模式

Handlermode---管理模式

1.1.2Theprivilegelevelsforsoftwareexecution

Unprivileged----非特权层

Privileged--------特权层

线程模式下,由CONTROLregister控制软件的执行是否在特权层。

管理模式下,永远都是特权层。

为了能够在线程模式下执行特权软件,可以在非特权层使用SVC指令进行管理调用,并在exceptionhandler中设置CONTROLregister。

1.1.3Stack堆栈

使用满递减堆栈。

Whentheprocessorpushesanewitemontothestack,it

decrementsthestackpointerandthenwritestheitemtothenewmemorylocation.

有两个堆栈,themainstackandtheprocessstack,每个堆栈都有一个堆栈只针对独立备份。

线程模式下,由CONTROLregister控制使用哪个堆栈。

管理模式下,永远使用themainstack。

1.1.4CoreRegisters---核心寄存器

Name

Required

privilege

Description

R0-R12

Either

32bits通用寄存器用于数据操作

MSP

Privileged

SP,R13,复位值处于thread模式,使用MSP,MSP的复位值为thevaluefromaddress0x00000000

PSP

Either

LR

Either

LinkRegister,R14,subroutines,functioncalls,andexceptions的返回信息。

复位值0xFFFFFFFF.

PC

Either

ProgramCounter,R15。

Bit[0]一直为0,因为取指令必须是半指令对其。

复位值为复位向量,即thevaluefromaddress0x00000004

PSR

Privileged

ProgramStatusRegister

CombinesAPSR,IPSR,EPSR,使用指令MSR/MRS

APSR

Either

ApplicationProgramStatusRegister,标志位NZCVQ

IPSR

Privileged

InterruptProgramStatusRegister,theexceptiontypenumberofthecurrentInterruptServiceRoutine--【0-83】

EPSR

Privileged

ExecutionProgramStatusRegister

PRIMASK

Privileged

Prioritymaskregister:

禁止所有可配置优先权的异常的执行

FAULTMASK

Privileged

Faultmaskregister:

禁止所有除了NMI的异常的执行

BASEPRI

Privileged

Baseprioritymaskregister:

theminimumpriorityforexceptionprocessing.禁止所有优先级等于或小于BASEPRI异常的执行.

CONTROL

Privileged

Bit1:

ASPSEL:

Activestackpointerselection

Bit0:

TPL:

Threadmodeprivilegelevel

1.1.5Datatypesmanages

Supportsthefollowingdatatypes:

–32-bitwords–16-bithalfwords–8-bitbytes

supports64-bitdatatransferinstructions.

Allmemoryaccesses(datamemory,instructionmemoryandPrivatePeripheralBus(PPB))aslittle-endian.

1.2Memorymodel

1.2.1Memoryregions,typesandattributes

Thememorymapsplitsthememorymapintoregions.Eachregionhasadefinedmemory

type,andsomeregionshaveadditionalmemoryattributes.

Thememorytypesare:

Normal

Device

Strongly-ordered

ThedifferentorderingrequirementsforDeviceandStrongly-orderedmemorymeanthatthememorysystemcanbufferawritetoDevicememory,butmustnotbufferawritetostronglyorderedmemory.

Theadditionalmemoryattributesinclude:

ExecuteNever(XN)

1.2.2Memorysystemorderingofmemoryaccesses

Normally,ifcorrectprogramexecutiondependsontwomemoryaccessescompletinginprogramorder,softwaremustinsertamemorybarrierinstructionbetweenthememoryaccessinstructions,

1.2.3Behaviorofmemoryaccesses

1.2.4Softwareorderingofmemoryaccesses

DMB:

TheDataMemoryBarrier(DMB)instructionensuresthatoutstandingmemorytransactionscompletebeforesubsequentmemorytransactions.

DSB:

TheDataSynchronizationBarrier(DSB)instructionensuresthatoutstandingmemorytransactionscompletebeforesubsequentinstructionsexecute.

ISB:

TheInstructionSynchronizationBarrier(ISB)ensuresthattheeffectofallcompletedmemorytransactionsisrecognizablebysubsequentinstructions.

Usememorybarrierinstructionsin,forexample:

Vectortable.

Self-modifyingcode.

Memorymapswitching.

Dynamicexceptionprioritychange.

Usingasemaphoreinmulti-mastersystem.

1.2.5Bit-banding

Abit-bandregionmapseachwordinabit-bandaliasregiontoasinglebitinthebit-band

region.Thebit-bandregionsoccupythelowest1MBoftheSRAMandperipheralmemory

regions.

Thememorymaphastwo32MBaliasregionsthatmaptotwo1MBbit-bandregions:

1.3Exceptionmodel

1.3.1Exceptiontypes

Exception

Number

IRQ

number

Exception

type

Priority

1

---

Reset

-3

2

-14

NMI

-2

3

-13

Hardfault

-1

4

-12

Memorymanagement

Configurable

5

-11

Busfault

Configurable

6

-10

Usagefault

Configurable

11

-5

SVCall

Configurable

14

-2

PendSV

Configurable

15

-1

SysTick

Configurable

16-83

0-67

Interrupt(IRQ)

Configurable

SVCall:

Asupervisorcall(SVC)isanexceptionthatistriggeredbytheSVCinstruction.InanOSenvironment,applicationscanuseSVCinstructionstoaccessOSkernelfunctionsanddevicedrivers.

PendSV:

PendSVisaninterrupt-drivenrequestforsystem-levelservice.InanOSenvironment,usePendSVforcontextswitchingwhennootherexceptionisactive.

1.Tosimplifythesoftwarelayer,theCMSISonlyusesIRQnumbersandthereforeusesnegativevaluesforexceptionsotherthaninterrupts.TheIPSRreturnstheExceptionnumber。

Prioty:

除了Reset-3,NMI-2,Hardfault-1,之外,其它的异常可以配置为0及其以上。

2.堆栈变化---

从上往下递减。

堆栈指针指向压入堆栈的最后一项。

中断进入时:

1.执行stacking动作。

压入一个八个字的堆栈帧。

Stackingframe:

R0-R3,R12

Returnaddress

PSR

LR

2.Stacking执行完毕后,执行中断代码,并且将EXC_RETURN的值存入LR。

其中含有中断发生前的操作模式以及指向堆栈帧的堆栈指针(MSPORPSP)。

中断返回时:

中断返回指令只能在handler中执行,如果在thread中执行的话,EXC_RETURN将当做常规的地址,从而会引起HardFaultException或者MemManagefault。

1.执行一条指令将EXC_RETURN值装入PC

APOPinstructionthatincludesthePC;

ABXinstructionwithanyregister.;

AnLDRorLDMinstructionwiththePCasthedestination;

2.执行完第一步后就能指示处理器完成中断,处理器开始中断返回序列。

1.3.2函数调用时关于参数的传递—来自IAREmbeddedWorkbench®IDEUserGuide

Registerparameters

传递参数的寄存器:

R0–R3

参数传递从左到右依次进行。

当寄存器不够时,参数按照相反的顺序(从右到左)传进堆栈。

Thestackshouldbealignedto8atfunctionentry.

Registersusedforreturningvalues

能够返回值的寄存器为:

R0andR0:

R1.

Returnaddresshandling

Afunctionwritteninassemblerlanguageshould,whenfinished,returntothecallerbyjumpingtotheaddresspointedtobytheregisterLR.

Atfunctionentry,non-scratchregistersandtheLRregistercanbepushedwithoneinstruction.Atfunctionexit,alltheseregisterscanbepoppedwithoneinstruction.ThereturnaddresscanbepoppeddirectlytoPC.Thefollowingexampleshowswhatthiscanlooklike:

PUSH{R4-R6,LR}/*Functionentry.*/.

.

POP{R4-R6,PC}/*Functionexit.*/

OnARMCortex-M,aninterruptserviceroutineentersandreturnsinthesamewayasanormalfunction,whichmeansnospecialkeywordsarerequired。

Theintrinsicfunctions__get_CPSRand__set_CPSRarenotavailablewhenyoucompileforARMCortex-M.

vectortable

Thevectortableisimplementedasanarray.Itshouldalwayshavethename__vector_table,becausecmainreferstothatsymbolandC-SPYlooksforthatsymbolwhendeterminingwherethevectortableislocated.

1.3.3关于中断的进入和退出—来自Cortex™-M3Revision:

r1p1TechnicalReferenceManual

进入:

Stacking

Whentheprocessorinvokesanexception,itautomaticallypushesthefollowingeightregisterstotheSPinthefollowingorder。

TheSPisdecrementedbyeightwordsbythecompletionofthestackpush.AfterreturningfromtheISR,theprocessorautomaticallypopstheeightregistersfromthestack.InterruptreturnispassedasadatafieldintheLR。

StepsthattheprocessortakesbeforeitentersanISR:

ThelastinstructionofanISRloadsthePCwithvalue0xFFFFFFFXthatwasLRonexceptionentry.ThisindicatestotheprocessorthattheISRiscomplete,andtheprocessorinitiatestheexceptionexitsequence.

Exceptionexitsteps

1.4Faulthandling

1.4.1Thefollowinggenerateafault:

●Abuserroron:

–Aninstructionfetchorvectortableload

–Adataaccess

●Aninternally-detectederrorsuchasanundefinedinstructionoranattempttochange

statewithaBXinstruction

●AttemptingtoexecuteaninstructionfromamemoryregionmarkedasNon-ExecutableXN).

1.4.2Faulttypes

Tableshowsthetypesoffault,thehandlerusedforthefault,thecorrespondingfault

statusregister,andtheregisterbitthatindicatesthatthefaulthasoccurred.

1.4.3Faultescalationandhardfaults

故障扩展

Insomesituations,afaultwithconfigurablepriorityistreatedasahardfault.Thisiscalled

priorityescalation,andthefaultisdescribedasescalatedtohardfault.Escalationtohard

faultoccurswhen:

●Afaulthandlercausesthesamekindoffaultastheoneitisservicing.Thisescalationtohardfaultoccursbecauseafaulthandlercannotpreemptitselfbecauseitmusthavethesamepriorityasthecurrentprioritylevel.

●Afaulthandlercausesafaultwiththesameorlowerpriorityasthefaultitisservicing.Thisisbecausethehandlerforthenewfaultcannotpreemptth