数字钟第六次实验设计0083075Word格式.docx

《数字钟第六次实验设计0083075Word格式.docx》由会员分享,可在线阅读,更多相关《数字钟第六次实验设计0083075Word格式.docx(15页珍藏版)》请在冰点文库上搜索。

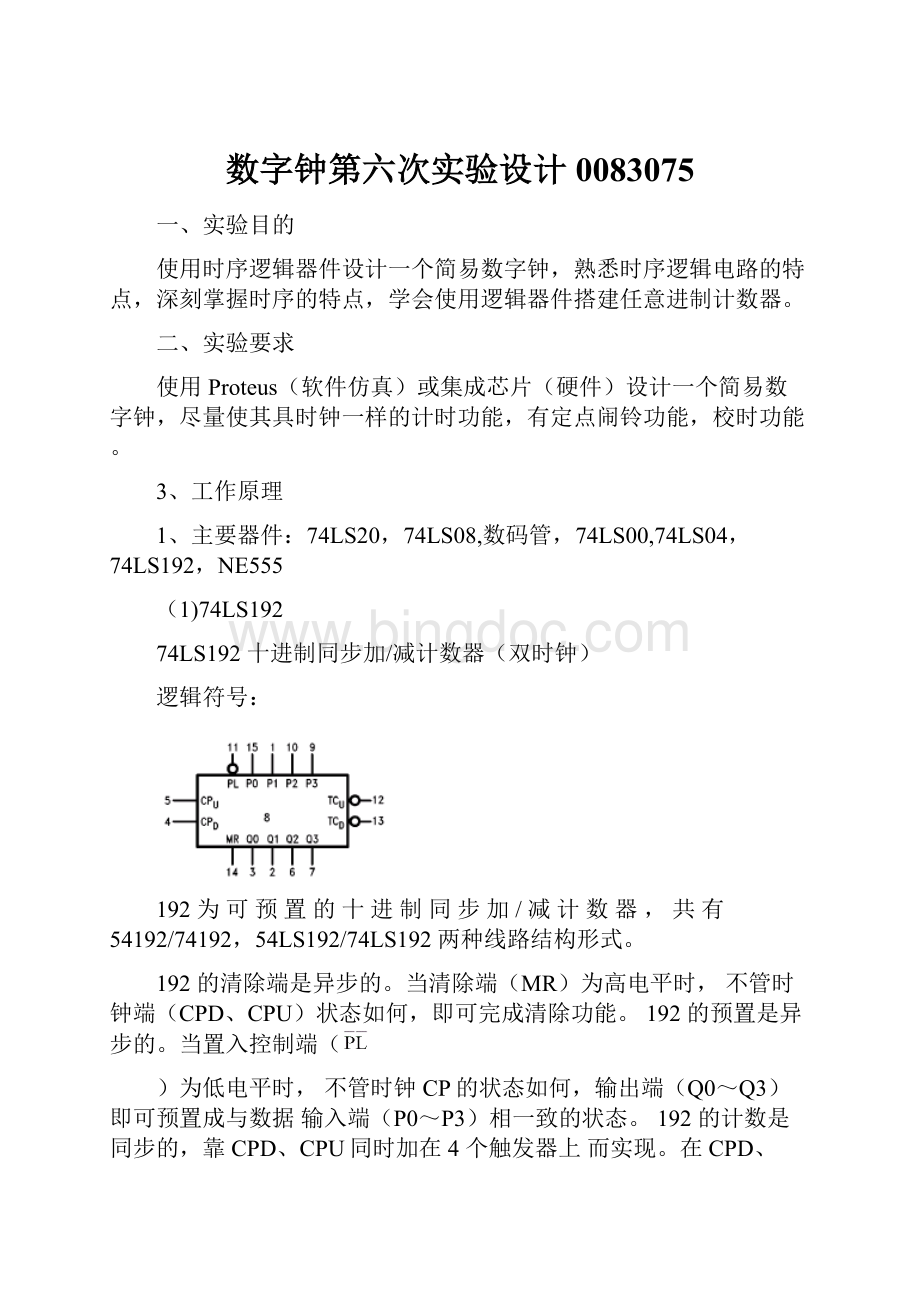

当清除端(MR)为高电平时,不管时钟端(CPD、CPU)状态如何,即可完成清除功能。

192的预置是异步的。

当置入控制端(

)为低电平时,不管时钟CP的状态如何,输出端(Q0~Q3)即可预置成与数据输入端(P0~P3)相一致的状态。

192的计数是同步的,靠CPD、CPU同时加在4个触发器上而实现。

在CPD、CPU上升沿作用下Q0~Q3同时变化,从而消除了异步计数器中出现的计数尖峰。

当进行加计数或减计数时可分别利用CPD或CPU,此时另一个时钟应为高电平。

当计数上溢出时,进位输出端(

)输出一个低电平脉冲,其宽度为CPU低电平部分的低电平脉冲;

当计数下溢出时,错位输出端(

)输出一个低电平脉冲,其宽度为CPD低电平部分的低电平脉冲。

当把

和

U分别连接后一级的CPD、CPU,即可进行级联。

双列直插封装:

引出端符号

错位输出端(低电平有效)

进位输出端(低电平有效)

CPD减计数时钟输入端(上升沿有效)

CPU加计数时钟输入端(上升沿有效)

MR异步清除端

P0~P3并行数据输入端

异步并行置入控制端(低电平有效)

Q0~Q3输出端

(2)74LS00四2输入与非门

1A-4A,1B-4B输入端

1Y-4Y输出端

双列直插封装:

功能表:

输入

输出

A

B

Y

1

(3)74LS04六反向器

引出端符号1A-6A

输入端1Y-6Y输出端

逻辑功能:

(4)NE555

NE555的特点有:

1.只需简单的电阻器、电容器,即可完成特定的振荡延时作用。

其延时范围极广,可由几微秒至几小时之久。

2.它的操作电源电压范围极大,可与TTL,CMOS等逻辑电路配合,也就是它的输出准位及输入触发准位,均能与这些逻辑系列的高、低态组合。

3.其输出端的供给电流大,可直接推动多种自动控制的负载。

4.它的计时精确度高、温度稳定度佳,且价格便宜。

5.静态电流最大值VCC=5V,RL=∞=6mAVCC=15V,RL=∞=15mA

NE555引脚位功能配置说明下:

Pin1(接地)-地线(或共同接地),通常被连接到电路共同接地。

Pin2(触发点)-这个脚位是触发NE555使其启动它的时间周期。

触发信号上缘电压须大于2/3VCC,下缘须低于1/3VCC。

Pin3(输出)-当时间周期开始555的输出输出脚位,移至比电源电压少1.7伏的高电位。

周期的结束输出回到O伏左右的低电位。

于高电位时的最大输出电流大约200mA。

Pin4(重置)-一个低逻辑电位送至这个脚位时会重置定时器和使输出回到一个低电位。

它通常被接到正电源或忽略不用。

Pin5(控制)-这个接脚准许由外部电压改变触发和闸限电压。

当计时器经营在稳定或振荡的运作方式下,这输入能用来改变或调整输出频率。

Pin6(重置锁定)-Pin6重置锁定并使输出呈低态。

当这个接脚的电压从1/3VCC电压以下移至2/3VCC以上时启动这个动作。

Pin7(放电)-这个接脚和主要的输出接脚有相同的电流输出能力,当输出为ON时为LOW,对地为低阻抗,当输出为OFF时为HIGH,对地为高阻抗。

Pin8(V+)-这是555个计时器IC的正电源电压端。

供应电压的范围是+4.5伏特(最小值)至+16伏特(最大值)。

2.总电路图:

该电路实现了时间计数功能,校时功能,以及闹铃功能。

如图1示

图1简易数字钟电路

3、分电路分析:

(1)1HZ脉冲和300HZ产生部分电路及原理:

图2555脉冲产生电路

通过NE555组成时钟脉冲方波发生器如图2示,其输出脉冲为:

其中1HZ脉冲驱动秒计数,300HZ驱动闹钟时的喇叭发声。

(2)时间计数部分

秒钟部分采用74LS192组成60进制计数器,如图3:

图3秒钟60进制计数原理图

即:

U2以10进制计数,每当U2计数到0的时候U1加1,U1则以6进制计数,每当U1计数到0时,图4的U4进1,分钟加1。

分钟计数部分跟秒钟计数一样,采用60进制计数,如图4:

当U4计数到0时向U5进1,U5计数器加1;

U5以6进制计数,当计数到0时向时位进位,U6计数器加1,小时加1.

小时位为24进制计数,U7、U6以24进制计数,当其计数到23时,低位再向它进位1次,就变成00。

如图5示:

图4分钟60进制计数原理图

图5小时24进制计数原理图

(3)显示时间部分:

本实验使用6位BCD码数码管,较七段数码管简单,省略了译码电路。

如图6示:

图6数码管显示电路

(4)清零部分

图7清零电路部分

Q0端接到各个计数器的

端,当按下开关后,给各个计数器的

一个低电平,使各个计数器输出预先制定的值,即初值0,实现了所有数码管清零功能。

如图7、图8示。

图8各数码管均置零

(5)校时部

当开关SW1断开时,FQ0进位信号顺利通过两个与非门正常计数,当开关闭合后,进位信号对11脚输出无影响,手动按下按钮开关产生一个低电平,通过与非门11脚输出一个低电平,放开后,11脚变为高电平,将11脚连接到小时低位或分钟地位脉冲输入端,产生进位信号,计数器加1,实现手动加数,也就是手动校时。

如图9示。

图9校时部分电路

(6)闹钟部分

本实验设定7点29为闹铃开始时间,响铃一分钟,电路如图10示,此处使用4输入与非门将设定的小时、分钟高电平信号按逻辑连接到一起,控制与非门U11的打开与关闭,当时间计数到设定的时间时,U11的10脚为高电平,与非门打开,300HZ的脉冲信号从9脚输入,通过一个三极管控制着喇叭发声。

图10闹钟部分电路

(7)总体仿真图

(a)

(b)

(c)

(d)

(e)

图11总体仿真图

四、总结

在此次的数字钟设计过程中,我们更进一步地熟悉了芯片的结构及掌握了各芯片的工作原理和其具体的使用方法。

也锻炼了自己独立思考问题的能力和通过查看相关资料来解决问题的习惯。

虽然这只是一次简单的课程设计,但通过这次课程设计我们了解了课程设计的一般步骤,和设计中应注意的问题,同时我们也掌握了做设计的基本流程,为我们以后进行更复杂的设计奠定了坚实的基础。

我们清楚的知道了电路中各个芯片能够完成什么样的功能,使用芯片时应该注意那些要点。

同一个电路可以用那些芯片实现,各个芯片实现同一个功能的区别。

另外,我们设计要从市场需求出发,既要有强大的功能,又要在价格方面比同等档次的便宜。

同时对普通计数器如何构成n进制计数器有了更深的了解和掌握,对自我的实际操作能力也有了很高的提升。

在这次设计过程中,我也对word、protel等软件有了更进一步的了解,这使我在以后的工作中更加得心应手。

五、指导教师评语及成绩

评语:

成绩:

指导教师签名:

廖汉程

批阅日期:

20年月日