外文翻译-中英文对照avr单片机.docx

《外文翻译-中英文对照avr单片机.docx》由会员分享,可在线阅读,更多相关《外文翻译-中英文对照avr单片机.docx(29页珍藏版)》请在冰点文库上搜索。

AVRCPUCore

IntroductionThissectiondiscussestheAVRcorearchitectureingeneral.Themainfunctionofthe

CPUcoreistoensurecorrectprogramexecution.TheCPUmustthereforebeableto

accessmemories,performcalculations,controlperipherals,andhandleinterrupts.

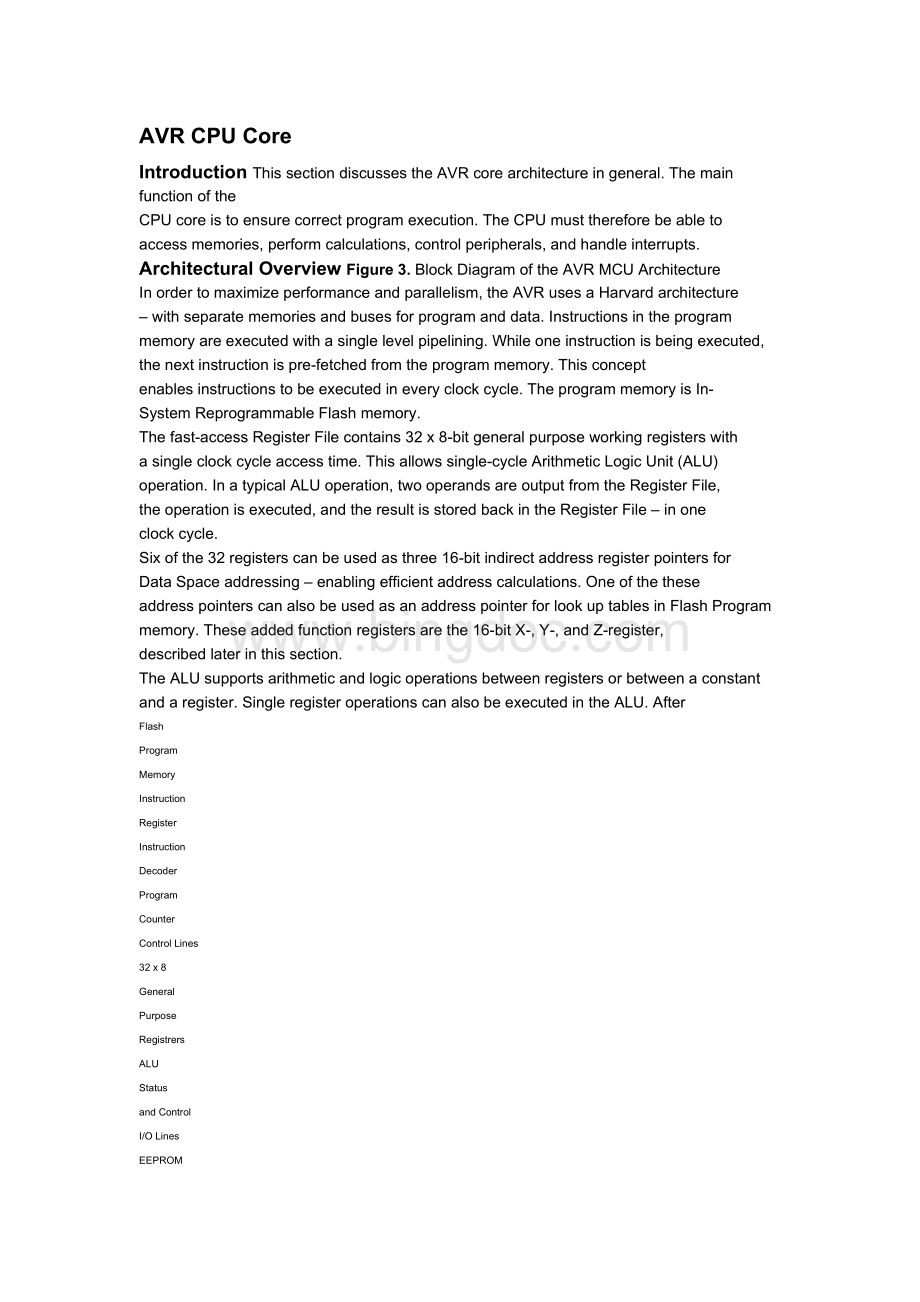

ArchitecturalOverviewFigure3.BlockDiagramoftheAVRMCUArchitecture

Inordertomaximizeperformanceandparallelism,theAVRusesaHarvardarchitecture

–withseparatememoriesandbusesforprogramanddata.Instructionsintheprogram

memoryareexecutedwithasinglelevelpipelining.Whileoneinstructionisbeingexecuted,

thenextinstructionispre-fetchedfromtheprogrammemory.Thisconcept

enablesinstructionstobeexecutedineveryclockcycle.TheprogrammemoryisIn-

SystemReprogrammableFlashmemory.

Thefast-accessRegisterFilecontains32x8-bitgeneralpurposeworkingregisterswith

asingleclockcycleaccesstime.Thisallowssingle-cycleArithmeticLogicUnit(ALU)

operation.InatypicalALUoperation,twooperandsareoutputfromtheRegisterFile,

theoperationisexecuted,andtheresultisstoredbackintheRegisterFile–inone

clockcycle.

Sixofthe32registerscanbeusedasthree16-bitindirectaddressregisterpointersfor

DataSpaceaddressing–enablingefficientaddresscalculations.Oneofthethese

addresspointerscanalsobeusedasanaddresspointerforlookuptablesinFlashProgram

memory.Theseaddedfunctionregistersarethe16-bitX-,Y-,andZ-register,

describedlaterinthissection.

TheALUsupportsarithmeticandlogicoperationsbetweenregistersorbetweenaconstant

andaregister.SingleregisteroperationscanalsobeexecutedintheALU.After

Flash

Program

Memory

Instruction

Register

Instruction

Decoder

Program

Counter

ControlLines

32x8

General

Purpose

Registrers

ALU

Status

andControl

I/OLines

EEPROM

DataBus8-bit

Data

SRAM

DirectAddressing

IndirectAddressing

Interrupt

Unit

SPI

Unit

Watchdog

Timer

Analog

Comparator

I/OModule2

I/OModule1

I/OModulen

9

ATmega16(L)

2466N–AVR–10/06

anarithmeticoperation,theStatusRegisterisupdatedtoreflectinformationaboutthe

resultoftheoperation.

Programflowisprovidedbyconditionalandunconditionaljumpandcallinstructions,

abletodirectlyaddressthewholeaddressspace.MostAVRinstructionshaveasingle

16-bitwordformat.Everyprogrammemoryaddresscontainsa16-or32-bitinstruction.

ProgramFlashmemoryspaceisdividedintwosections,theBootprogramsectionand

theApplicationProgramsection.BothsectionshavededicatedLockbitsforwriteand

read/writeprotection.TheSPMinstructionthatwritesintotheApplicationFlashmemory

sectionmustresideintheBootProgramsection.

Duringinterruptsandsubroutinecalls,thereturnaddressProgramCounter(PC)is

storedontheStack.TheStackiseffectivelyallocatedinthegeneraldataSRAM,and

consequentlytheStacksizeisonlylimitedbythetotalSRAMsizeandtheusageofthe

SRAM.AlluserprogramsmustinitializetheSPintheresetroutine(beforesubroutines

orinterruptsareexecuted).TheStackPointerSPisread/writeaccessibleintheI/O

space.ThedataSRAMcaneasilybeaccessedthroughthefivedifferentaddressing

modessupportedintheAVRarchitecture.

ThememoryspacesintheAVRarchitecturearealllinearandregularmemorymaps.

AflexibleinterruptmodulehasitscontrolregistersintheI/Ospacewithanadditional

globalinterruptenablebitintheStatusRegister.Allinterruptshaveaseparateinterrupt

vectorintheinterruptvectortable.Theinterruptshavepriorityinaccordancewiththeir

interruptvectorposition.Thelowertheinterruptvectoraddress,thehigherthepriority.

TheI/Omemoryspacecontains64addressesforCPUperipheralfunctionsasControl

Registers,SPI,andotherI/Ofunctions.TheI/OMemorycanbeaccesseddirectly,oras

theDataSpacelocationsfollowingthoseoftheRegisterFile,$20-$5F.

ALU–ArithmeticLogic

Unit

Thehigh-performanceAVRALUoperatesindirectconnectionwithallthe32general

purposeworkingregisters.Withinasingleclockcycle,arithmeticoperationsbetween

generalpurposeregistersorbetweenaregisterandanimmediateareexecuted.The

ALUoperationsaredividedintothreemaincategories–arithmetic,logical,andbit-functions.

Someimplementationsofthearchitecturealsoprovideapowerfulmultiplier

supportingbothsigned/unsignedmultiplicationandfractionalformat.Seethe“Instruction

Set”sectionforadetaileddescription.

StatusRegisterTheStatusRegistercontainsinformationabouttheresultofthemostrecentlyexecuted

arithmeticinstruction.Thisinformationcanbeusedforalteringprogramflowinorderto

performconditionaloperations.NotethattheStatusRegisterisupdatedafterallALU

operations,asspecifiedintheInstructionSetReference.Thiswillinmanycases

removetheneedforusingthededicatedcompareinstructions,resultinginfasterand

morecompactcode.

TheStatusRegisterisnotautomaticallystoredwhenenteringaninterruptroutineand

restoredwhenreturningfromaninterrupt.Thismustbehandledbysoftware.

TheAVRStatusRegister–SREG–isdefinedas:

Bit76543210

ITHSVNZCSREG

Read/WriteR/WR/WR/WR/WR/WR/WR/WR/W

InitialValue00000000

10ATmega16(L)

2466N–AVR–10/06

•Bit7–I:

GlobalInterruptEnable

TheGlobalInterruptEnablebitmustbesetfortheinterruptstobeenabled.Theindividual

interruptenablecontrolisthenperformedinseparatecontrolregisters.IftheGlobal

InterruptEnableRegisteriscleared,noneoftheinterruptsareenabledindependentof

theindividualinterruptenablesettings.TheI-bitisclearedbyhardwareafteraninterrupt

hasoccurred,andissetbytheRETIinstructiontoenablesubsequentinterrupts.TheIbit

canalsobesetandclearedbytheapplicationwiththeSEIandCLIinstructions,as

describedintheinstructionsetreference.

•Bit6–T:

BitCopyStorage

TheBitCopyinstructionsBLD(BitLoaD)andBST(BitSTore)usetheT-bitassourceor

destinationfortheoperatedbit.AbitfromaregisterintheRegisterFilecanbecopied

intoTbytheBSTinstruction,andabitinTcanbecopiedintoabitinaregisterinthe

RegisterFilebytheBLDinstruction.

•Bit5–H:

HalfCarryFlag

TheHalfCarryFlagHindicatesaHalfCarryinsomearithmeticoperations.HalfCarryis

usefulinBCDarithmetic.Seethe“InstructionSetDescription”fordetailedinformation.

•Bit4–S:

SignBit,S=N⊕V

TheS-bitisalwaysanexclusiveorbetweentheNegativeFlagNandtheTwo’sComplement

OverflowFlagV.Seethe“InstructionSetDescription”fordetailedinformation.

•Bit3–V:

Two’sComplementOverflowFlag

TheTwo’sComplementOverflowFlagVsupportstwo’scomplementarithmetics.See

the“InstructionSetDescription”fordetailedinformation.

•Bit2–N:

NegativeFlag

TheNegativeFlagNindicatesanegativeresultinanarithmeticorlogicoperation.See

the“InstructionSetDescription”fordetailedinformation.

•Bit1–Z:

ZeroFlag

TheZeroFlagZindicatesazeroresultinanarithmeticorlogicoperation.Seethe

“InstructionSetDescription”fordetailedinformation.

•Bit0–C:

CarryFlag

TheCarryFlagCindicatesacarryinanarithmeticorlogicoperation.Seethe“Instruction

SetDescription”fordetailedinformation.

11

ATmega16(L)

2466N–AVR–10/06

GeneralPurpose

RegisterFile

TheRegisterFileisoptimizedfortheAVREnhancedRISCinstructionset.Inorderto

achievetherequiredperformanceandflexibility,thefollowinginput/outputschemesare

supportedbytheRegisterFile:

•One8-bitoutputoperandandone8-bitresultinput

•Two8-bitoutputoperandsandone8-bitresultinput

•Two8-bitoutputoperandsandone16-bitresultinput

•One16-bitoutputoperandandone16-bitresultinput

Figure4showsthestructureofthe32generalpurposeworkingregistersintheCPU.

Figure4.AVRCPUGeneralPurposeWorkingRegisters

MostoftheinstructionsoperatingontheRegisterFilehavedirectaccesstoallregisters,

andmostofthemaresinglecycleinstructions.

AsshowninFigure4,eachregisterisalsoassignedadatamemoryaddress,mapping

themdirectlyintothefirst32locationsoftheuserDataSpace.Althoughnotbeingphysically

implementedasSRAMlocations,thismemoryorganizationprovidesgreat

flexibilityinaccessoftheregisters,astheX-,Y-,andZ-pointerRegisterscanbesetto

indexanyregisterinthefile.

70Addr.

R0$00

R1$01

R2$02

…

R13$0D

GeneralR14$0E

PurposeR15$0F

WorkingR16$10

RegistersR17$11

…

R26$1AX-registerLowByte

R27$1BX-registerHighByte

R28$1CY-registerLowByte

R29$1DY-registerHighByte

R30$1EZ-registerLowByte

R31$1FZ-registerHighByte

12ATmega16(L)

2466N–AVR–10/06

TheX-register,Y-registerand

Z-register

TheregistersR26..R31havesomeaddedfunctionstotheirgeneralpurposeusage.

Theseregistersare16-bitaddresspointersforindirectaddressingoftheDataSpace.

ThethreeindirectaddressregistersX,Y,andZaredefinedasdescribedinFigure5.

Figure5.TheX-,Y-,andZ-registers

Inthedifferentaddressingmodestheseaddressregistershavefunctionsasfixeddisplacement,

automaticincrement,andautomaticdecrement(seetheInstructionSet

Referencefordetails).

StackPointerTheStackismainlyusedforstoringtemporarydata,forstoringlocalvariablesandfor

storingreturnaddressesafterinterruptsandsubroutinecalls.TheStackPointerRegister

alwayspointstothetopoftheStack.NotethattheStackisimplementedasgrowing

fromhighermemorylocationstolowermemorylocations.ThisimpliesthataStac