FPGA实验报告.docx

《FPGA实验报告.docx》由会员分享,可在线阅读,更多相关《FPGA实验报告.docx(23页珍藏版)》请在冰点文库上搜索。

FPGA实验报告

目录

实验一分频器

实验三ADC0809模数转换实验

实验二七段数码管扫描显示

实验四双向移位寄存器

实验一分频器

一、实验目的

1.学习分频器的设计,进一步了解、熟悉和掌握FPGA开发软件Quartus II的使用方法

2.学习Verilog HDL和VHDL的编程方法

3.学会使用Vector Wave功能仿真

4.掌握使用多种方法分配管脚

二、实验内容

编写一个分频器的Verilog 代码和VHDL代码并仿真,编译下载验证

三、实验原理

在数字电路中, 时钟信号的分频是很常见的电路。

分频器除了可以对时钟信号频率做除以二的计算外,分频器同时很类似涟波计数器。

涟波计数器是计数器的一种,它属于异步设计。

因为触发器并非皆由同一个时钟信号同步操作,所以它非常节省电路面积。

本实验要设一个带选择的分频时钟,SEL[1:

0]用于选择是几分频。

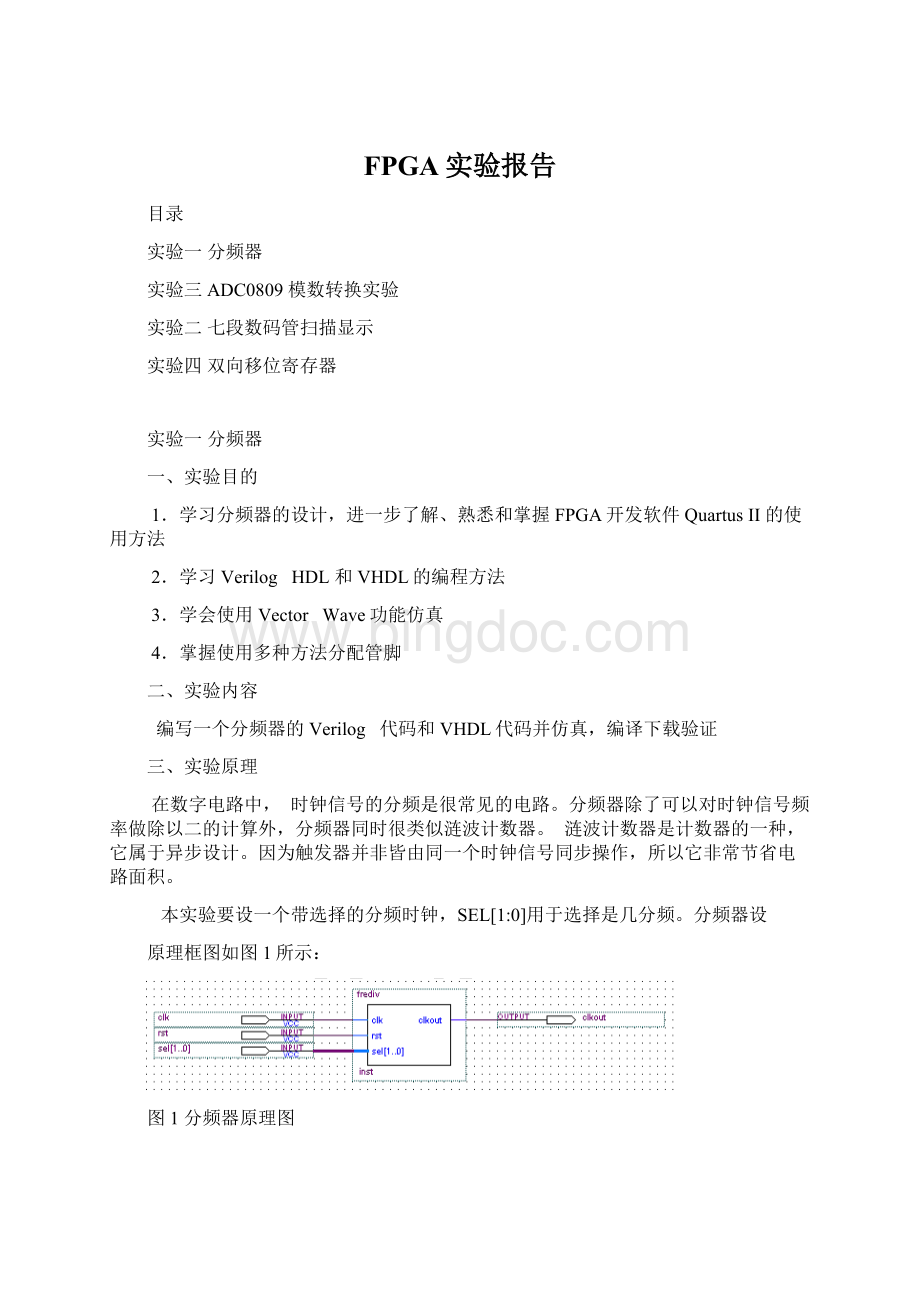

分频器设

原理框图如图1所示:

图1分频器原理图

从原理图中可见,核心板的时钟是50MHz,通过sel[1:

0]选择分频数,00:

不分频;01:

12.5M分频;10:

25M四分频;11:

50M分频。

采用SW1‐SW2设置分频值,SW3复位。

LED1为时钟的输出,通过调整SW1、SW2,可以得到不同的闪烁频率。

引脚分配情况如表1所示

表1引脚分布情况

四、实验步骤

1.新建工程,取名为frediv,如下图2所示。

图2新建工程

2.新建VHDL设计文件,选择“File|New” ,在New对话框中选择Device Design Files

下的VHDL File,单击OK,完成新建设计文件。

3.在新建设计文件中输入VHDL程序。

4.生成“Symbol”文件,新建“Block Diagram/Schematic File”文件,在文件中添加刚刚生成的“Symbol”以及输入输出管脚,最后完整的系统顶层模块图如图3所示。

图3 顶层模块图

5.保存文件,使用qsf或者tcl进行管脚分配(相应的文件在本工程里面都可以找到)。

6.对该工程文件进行全程编译处理,若在编译过程中发现错误,则找出并更正错误,直至编译成功为止。

7.新建“Vector Waveform File”文件进行波形仿真。

8.下载完成后,观察实验结果。

五、VHDL程序

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity frediv is

port

(

clk :

in std_logic;

rst :

in std_logic;

sel :

in std_logic_vector(1 downto 0);

clkout:

out std_logic

);

end frediv;

architecture rt1 of frediv is

begin

process(rst,clk)

variable cn1,cn2,cn3:

integer range 0 to 50000000;

begin

if rst = '1' then

clkout <= '0';

elsif clk'event and clk = '1' then

if sel = "01" then

if cn1 = 12499999 then

cn1 :

= 0;

else

cn1 :

= cn1 + 1;

if cn1 <= 6249999 then

clkout <= '1';

else

clkout <= '0';

end if;

end if;

elsif sel = "10" then

if cn2 = 24999999 then

cn2 :

= 0;

else

cn2 :

= cn2 + 1;

if cn2 <= 12499999 then

clkout <= '1';

else

clkout <= '0';

end if;

end if;

elsif sel = "11" then

if cn3 = 49999999 then

cn3 :

= 0;

else

cn3 :

= cn3 + 1;

if cn3 <= 24999999 then

clkout <= '1';

else

clkout <= '0';

end if;

end if;

else

clkout <= clk;

end if;

end if;

end process;

end rt1;

实验二七段数码管扫描显示

一、实验目的

1.学习动态扫描显示的原理,进一步了解、熟悉和掌握FPGA开发软件Quartus II的使用方法

2.学习Verilog HDL和VHDL的编程方法

3.学会使用Vector Wave功能仿真

4.掌握使用多种方法分配管脚

二、实验内容

利用动态扫描的方式设计一个在8个数码管上面分别显示1,3,5,7….的程序

三、实验环境

硬件:

EP2C35实验箱、USB ByteBlaster 下载电缆

软件:

Altera Quartus II 9.0 集成开发环境

四、实验原理

一般来说,多个数码管的连接并不是把每个数码管都独立的与可编程逻辑器件连接,而是把所有的LED管的输入连在一起。

如图1所示。

其中每个数码管的8个段:

a、b、c、d、e、f、g、h(h是小数点),都分别连到SEG_D0~SEG_D7,8个数码管分别由8个选通信号DIG_C0~DIG_C7来选择。

被选通的数码管显示数据,其余关闭。

如在某一时刻DIG_C2为低电平“0”,其余选通信号为高电平“1”,这时仅DIG_C2对应的数码管显示来自段码信号端的数据,而其它7个数码管呈显示关闭状态。

根据这种电路状态,如果希望8个数码管显示希望的数据,就必须使得8个选通信号DIG_C0~DIG_C7分别被单独选通,并在此同时,在段信号输入口加上希望在该对应数码管上显示的数据,于是随着选通信号的扫描就能实现扫描显示的目的。

虽然每次只有一个LED显示,但只要扫描显示速率够快,由于人的视觉余辉效应,使我们仍会感觉所有的数码管都在同时显示。

扫描频率大小不许合适才能有很好的效果。

如果太小,而每个LED开启的时间大于人眼的视觉暂停时间,那么会产生闪烁现象。

而扫描频率太大,则会

图1 扫描数码管的原理图

造成LED的频繁开启和关断,大大增加LED功耗(开启和关断的时刻功耗很大)。

一般来说,扫描频率选在50Hz比较合适。

图2 设计原理框图

SW1为清零信号使能,dig为数码管片选信号端,seg为7段显示片选信号。

5、引脚分配情况

表1 引脚分配

6、实验步骤

1.新建工程,取名为seven_seg,如下图所示

图2 指定工程的目录、工程名和顶层实体名

2.新建VHDL设计文件,选择“File|New” ,在New对话框中选择Device Design Files下的VHDL File,单击OK,完成新建设计文件。

3.在新建设计文件中输入VHDL程序。

4.生成“Symbol”文件,新建“Block Diagram/Schematic File”文件,在文件中添加刚刚生成的“Symbol”以及输入输出管脚,最后完整的系统顶层模块图如图3所示。

图3 顶层模块图

5.保存文件,使用qsf或者tcl进行管脚分配(相应的文件在本工程里面都可以找到)。

6.对该工程文件进行全程编译处理,若在编译过程中发现错误,则找出并更正错误,直至编译成功为止。

7.新建“Vector Waveform File”文件进行波形仿真。

图4 利用vector file仿真数据选择器的波形

8.下载完成后,观察实验结果。

7、VHDL程序

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity seven_seg is

port

(

clk,clr :

in std_logic;

dig,seg :

out std_logic_vector(7 downto 0)

);

end seven_seg;

architecture rt1 of seven_seg is

signal clk_r:

std_logic;

signal scan:

std_logic_vector(2 downto 0);

signal dig_r:

std_logic_vector(7 downto 0);

signal data_r:

std_logic_vector(3 downto 0);

signal seg_r:

std_logic_vector(7 downto 0);

begin

dig <= dig_r;

seg <= seg_r;

a:

process(clk,clr)

variable count:

integer range 0 to 50000000;

begin

if clr = '0' then

count :

= 0;

elsif clk'event and clk = '1' then

if count = 49999999 then

count :

= 0;

else

count :

= count + 1;

end if;

if count <= 24999999 then

clk_r <= '0';

else

clk_r <= '1';

end if;

end if;

end process;

b:

process(clk_r,clr)

begin

if clr = '0' then

scan <= "000";

elsif clk_r'event and clk_r = '1' then

scan <= scan + '1';

end if;

end process;

c:

process(scan)

begin

case scan is

when "000" => dig_r <= "00000000"; data_r<="0001";

when "001" => dig_r <= "00000000"; data_r<="0011";

when "010" => dig_r <= "00000000"; data_r<="0101";

when "011" => dig_r <= "00000000"; data_r<="0111";

when "100" => dig_r <= "00000000"; data_r<="1001";

when "101" => dig_r <= "00000000"; data_r<="1011";

when "110" => dig_r <= "00000000"; data_r<="1101";

when "111" => dig_r <= "00000000"; data_r<="1111";

end case;

end process;

d:

process(data_r)

begin

case data_r is

when "0000" => seg_r <= "11000000";‐‐0

when "0001" => seg_r <= "11111001";‐‐1

when "0010" => seg_r <= "10100100";‐‐2

when "0011" => seg_r <= "10110000";‐‐3

when "0100" => seg_r <= "10011001";‐‐4

when "0101" => seg_r <= "10010010";‐‐5

when "0110" => seg_r <= "10000010";‐‐6

when "0111" => seg_r <= "11111000";‐‐7

when "1000" => seg_r <= "10000000";‐‐8

when "1001" => seg_r <= "10010000";‐‐9

when "1010" => seg_r <= "10001000";‐‐a

when "1011" => seg_r <= "10000011";‐‐b

when "1100" => seg_r <= "10100110";‐‐c

when "1101" => seg_r <= "10100001";‐‐d

when "1110" => seg_r <= "10000110";‐‐e

when "1111" => seg_r <= "10001110";‐‐f

end case;

end process;

end rt1;

实验三ADC0809模数转换实验

一、实验目的

1.了解AD转换原理,进一步了解、熟悉和掌握FPGA开发软件Quartus II的使用方法

2.学习Verilog HDL和VHDL的编程方法

3.学会使用Vector Wave功能仿真

4.掌握使用多种方法分配管脚

二、实验内容

编写一个AD转换的Verilog、VHDL 代码并仿真,编译下载验证。

三、实验环境

硬件:

EP2C35实验箱、USB ByteBlaster 下载电缆

软件:

Altera Quartus II 9.0 集成开发环境

四、实验原理

1.ADC0809是带有8位A/D转换器、8路多路开关以及微处理机兼容的控制逻辑的CMOS组件。

它是逐次逼近式A/D转换器,可以和单片机直接接口。

.ADC0809由一个8路模拟开关、一个地址锁存与译码器、一个A/D转换器和一个三态输出锁存器组成。

多路开关可选通8个模拟通道,允许8路模拟量分时输入,共用A/D转换器进行转换。

三态输出锁器用于锁存A/D转换完的数字量,当OE端为高电平时,才可以从三态输出锁存器取走转换完的数据。

ADC0809的主要技术指标为:

·分辨率:

8位

·单电源:

+5V

·总的不可调误差:

±1LSB

·转换时间:

取决于时钟频率

·模拟输入范围:

单极性0~5V

·时钟频率范围:

10KHZ~1280KHZ ADC0809芯片的内部结构如图1

图1 芯片的内部结构

2.芯片的管脚定义;

图2 芯片的管脚定义

IN0-IN7:

8条模拟量输入通道

ADC0809对输入模拟量要求:

信号单极性,电压范围是0-5V,若信号太小,必须进行放大;输入的模拟量在转换过程中应该保持不变,如若模拟量变化太快,则需在输入前增加采样保持电路。

地址输入和控制线:

4条。

ALE为地址锁存允许输入线,高电平有效。

当ALE线为高电平时,地址锁存与译码器将A,B,C三条地址线的地址信号进行锁存,经译码后被选中的通道的模拟量进转换器进行转换。

A,B和C为地址输入线,用于选通IN0-IN7上的一路模拟量输入。

数字量输出及控制线:

11条。

ST为转换启动信号。

当ST上跳沿时,所有内部寄存器清零;下跳沿时,开始进行A/D转换;在转换期间,ST应保持低电平。

EOC为转换结束信号。

当EOC为高电平时,表明转换结束;否则,表明正在进行A/D转换。

OE为输出允许信号,用于控制三条输出锁存器向单片机输出转换得到的数据。

OE=1,输出转换得到的数据;OE=0,输出数据线呈高阻状态。

D7-D0为数字量输出线。

CLK为时钟输入信号线。

因ADC0809的内部没有时钟电路,所需时钟信号必须由外界提供,通常使用频率为500KHZ,VREF(+),VREF(-)为参考电压输入。

图3 ADC0809的输出控制时序

3.设计原理框图如图4所示:

图4 原理框图

从原理图中可见,实验箱上的SW1、SW2、SW3为模拟信号选通端,选择AIN0,AIN1,AIN2,EOC为ADC0809的转换返回信号,LED1‐LED8显示转换的数字量。

如果将SW1‐SW3全部置为“000”,则选通AIN0,旋转按钮,LED1‐LED8灯的亮灭为转换的数字量值。

5、引脚分配情况

表1 引脚分配

六、实验步骤

1.新建工程,取名为ADC0809,如下图所示。

图5新建工程

2.新建VHDL设计文件,选择“File|New” ,在New对话框中选择Device Design Files下的VHDL File,单击OK,完成新建设计文件。

3.在新建设计文件中输入VHDL程序。

4.生成“Symbol”文件,新建“Block Diagram/Schematic File”文件,在文件中添加刚刚生成的“Symbol”以及输入输出管脚,最后完整的系统顶层模块图如图6所示。

图6 顶层模块图

5.保存文件,使用qsf或者tcl进行管脚分配(相应的文件在本工程里面都可以找到)。

6.对该工程文件进行全程编译处理,若在编译过程中发现错误,则找出并更正错误,直至编译成功为止。

7.新建“Vector Waveform File”文件进行波形仿真。

8.下载完成后,观察实验结果。

7、VHDL程序

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity adc0809 is

port

(

clk :

in std_logic; ‐‐system clock,reset signal

EOC :

in std_logic; ‐‐end of conversion signal

adc_in :

in std_logic_vector(2 downto 0); ‐‐ choose the channel

adc_D :

in std_logic_vector(7 downto 0); ‐‐the conversion data

ale,en,start:

out std_logic;

adc_clk :

out std_logic;

adc_out :

out std_logic_vector(2 downto 0); ‐‐adc0809 channel choose

led :

out std_logic_vector(7 downto 0)

);

end adc0809;

architecture rt1 of adc0809 is

signal cnt :

std_logic_vector(7 downto 0);

signal led_r :

std_logic_vector(7 downto 0);

type st is(st0,st1,st2,st3,st4,st5,st6);

signal p_state,n_state:

st:

=st0;

begin

adc_out <= adc_in;

p0:

process(clk) ‐‐get the adc's clock

begin

if clk'event and clk= '1' then