实验7BinaryVGAController.docx

《实验7BinaryVGAController.docx》由会员分享,可在线阅读,更多相关《实验7BinaryVGAController.docx(36页珍藏版)》请在冰点文库上搜索。

实验7BinaryVGAController

实验7Binary_VGA_Controller

一、实验目的

1.了解Binary_VGA_Controller,了解VGA显示;

2.熟悉Binary_VGA_Controller在工程中的应用;

3.改变VGA显示图像里光标形状和颜色。

二、简单介绍VGA控制器IP核的HDL代码

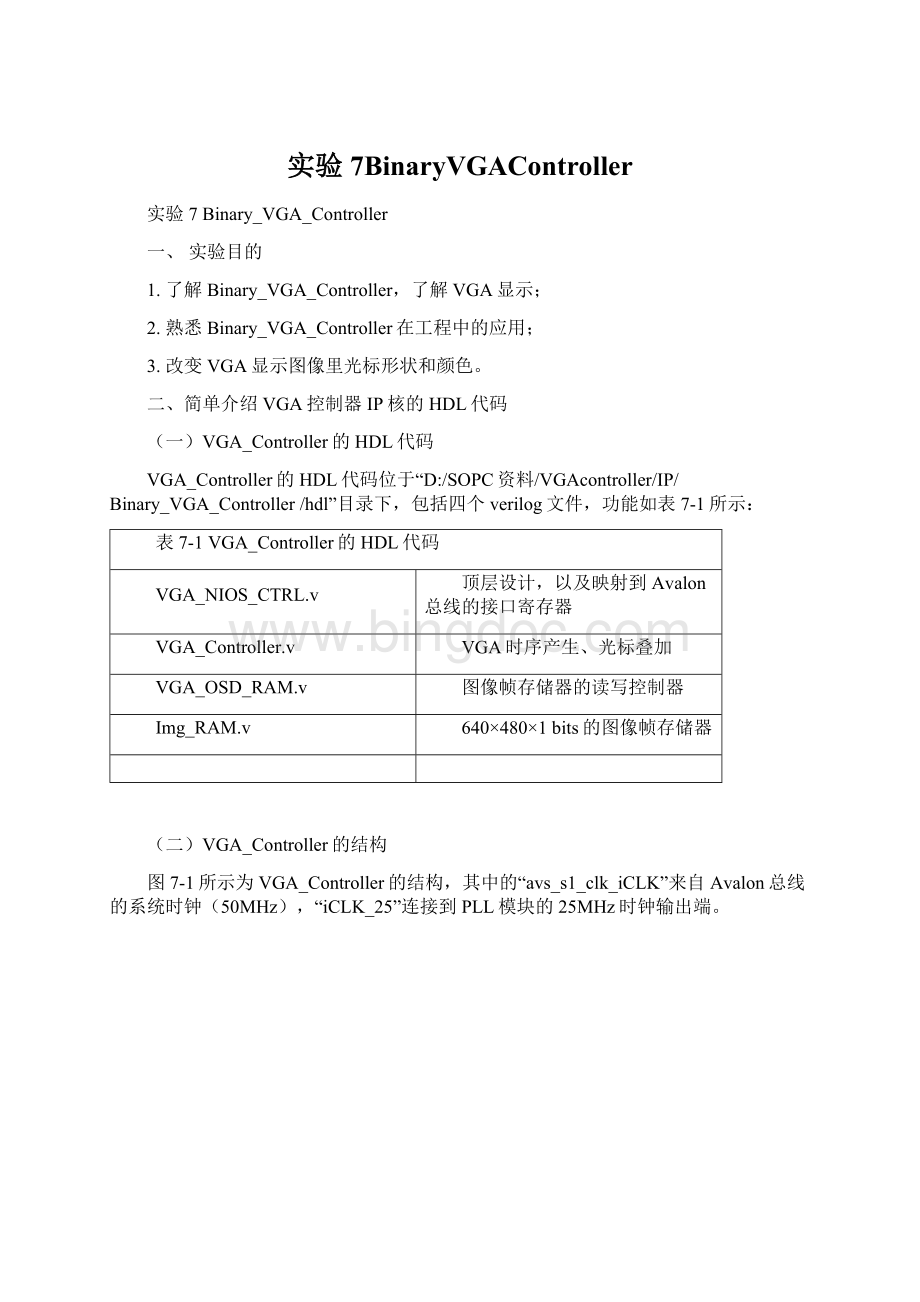

(一)VGA_Controller的HDL代码

VGA_Controller的HDL代码位于“D:

/SOPC资料/VGAcontroller/IP/Binary_VGA_Controller/hdl”目录下,包括四个verilog文件,功能如表7-1所示:

表7-1VGA_Controller的HDL代码

VGA_NIOS_CTRL.v

顶层设计,以及映射到Avalon总线的接口寄存器

VGA_Controller.v

VGA时序产生、光标叠加

VGA_OSD_RAM.v

图像帧存储器的读写控制器

Img_RAM.v

640×480×1bits的图像帧存储器

(二)VGA_Controller的结构

图7-1所示为VGA_Controller的结构,其中的“avs_s1_clk_iCLK”来自Avalon总线的系统时钟(50MHz),“iCLK_25”连接到PLL模块的25MHz时钟输出端。

三、实验步骤

(一)硬件初建:

新建“demo_vga”工程

鼠标左键双击桌面上的“QuartusII”快捷方式图标,耐心等待片刻,即可启动“QuartusII”设计页面,如图7-2所示。

在“QuartusII”设计页面内,鼠标左键单击“File‐>NewProjectWizard”。

弹出“NewProject

Wizard:

introduction”。

如图7-3所示。

鼠标左键单击“next”按钮跳过此页,进入“NewProjectWizard:

Directory,Name,Top-levelentity”页。

如图7-4所示。

“theworkingdirectoryforthisproject”(工程路径)可以任意填写,例如:

本实验中填写为“E:

\demo\demo_VGAcontroller”。

这里需要注意:

由于“SOPCBuiler”工具不能识别空格、中划线等符号,故实验步骤中如果需要命名,命名中不允许有空格、中划线出现,但“SOPCBuiler”工具能识别下划线。

工程的“工作目录”如前“E:

\demo\demo_VGAcontroller”,将会在E盘上产生一个文件夹“demo”,在“demo”文件夹里产生另一个文件夹“demo_VGAcontroller”(工程文件夹,保存工程文件),这个实验后续步骤中产生的各种文件会自动保存到路径“E:

\demo\demo_VGAcontroller”下。

“thenameofthisproject”(工程名字)也可以任意填写,填写为“demo_vga”。

“thenameofthetop-leveldesignentityforthisproject”(工程顶层实体名称)会自动与工程名字相同,也为“demo_vga”。

这里需要注意:

工程顶层设计实体名称一定要与编写的顶层文件“module***”中模块名字一致。

“NewProjectWizard:

Directory,Name,Top-levelentity”页面填写完成后,鼠标左键单击“next”按钮,弹出如图7-5所示的问句。

鼠标左键单击“是”按钮,进入“AddFiles[page2of5]”页面,如图7-6所示。

由于实验到这里还没有建立任何文档,再加上后面步骤中也可以添加,故这里跳过。

鼠标左键单击“Next”按钮跳过此页,进入“Family&DeviceSettings[page3of5]”页面。

“Family&DeviceSettings[page3of5]”页面:

“Devicefamily”栏里的“family”选择“CycloneII”;

“Availabledevices”栏里选择“EP2C70F896C6”器件。

其它为缺省设置,如图7-7所示。

鼠标左键单击“next”按钮的话,还会出现第4页EDA工具的设置和第5页的“Summary”,如果用到可以在此设置。

由于目前没有用到,所以在这里就可以用鼠标左键单击“Finish”按钮,完成新工程的初建。

新建的“QuartusII-E:

/demo/demo_VGAcontroller/demo_vga-demo_vga”工程如图7-8所示。

页面内“ProjectNavigator”(工程导航)下面的entity栏里,可以看到“CycloneII:

EP2C70F896C6”下面显示工程名字“demo_vga”。

初建的“QuartusII-E:

/demo/demo_VGAcontroller/demo_vga-demo_vga”工程页面,会自动保存在路径“E:

\demo\demo_VGAcontroller”下。

任何时候想要完成工程后续设计,可以打开此路径下的工程文件夹“demo_VGAcontroller”,如图7-9所示。

鼠标左键双击带有蓝色“Quartus”图标的“demo_vga”文件,就可以打开“QuartusII-E:

/demo/demo_VGAcontroller/demo_vga-demo_vga”工程页面。

(二)粘贴IP核到工程文件夹“demo_VGAcontroller”

在新建的“QuartusII-E:

/demo/demo_VGAcontroller/demo_vga-demo_vga”工程页面内,鼠标左键单击“open”按钮,弹出“打开”对话框。

在“打开”对话框的“查找范围”里,找到路径“D:

\SOPC实验资料\VGAcontroller资料”下的IP文件夹,拷贝到路径“E:

\demo\demo_VGAcontroller”下,如图7-10所示。

把IP核拷贝到此实验的工程文件夹“demo_VGAcontroller”后,“SOPCBuilder”工具会自动识别IP,此IP与Altera公司提供的其他共用IP核一起出现在“SOPCBuilder”工具页面共用IP库中,可以参与硬件配置。

(三)利用“SOPCBuilder”工具配置硬件

配置硬件是个繁琐的事情,如果一个硬件参数配置不对,整个系统就不能用,所以简便而实用的方法是从友晶科技的大师们提供的范例里拷贝硬件配置,另外还可以从已经做通的实验里拷贝硬件配置。

在“QuartusII-E:

/demo/demo_VGAcontroller/demo_vga-demo_vga”工程页面,鼠标左键单击“open”按钮,弹出“打开”对话框。

在“查找范围”选择某个实验所在的路径,把“nios0.sopc”文件拷贝到此实验所在的路径“E:

/demo/demo_VGAcontroller”下。

鼠标左键双击“nios0.sopc”文件,打开后可以重新配置硬件。

有些在此实验需要的硬件可以保留,有些用不到的硬件可以一个个删除:

鼠标左键单击硬件名称使其蓝色高亮,然后单击硬件默认显示栏下的“Remove”按钮,即可删去此硬件。

在此,作为参考再次把此实验所需硬件完整配置一遍。

在“QuartusII-E:

/demo/demo_VGAcontroller/demo_vga-demo_vga”工程页面内,鼠标左键单击Tools‐>SOPCBuilder。

弹出“CreateNewSystem”对话框:

“SystemName”填写“nios0”。

“TargetHDL”项一般选择“Verilog”。

如图7-11所示。

鼠标左键单击“OK”按钮,即初步建成了工程的硬件添加系统。

在这个页面里可以添加工程所需硬件,形成良好的硬件系统。

添加的硬件会显示在默认空白部分,并且可以修改,在此默认空白区还显示硬件的主从连接,如图7-12所示。

“SOPCBuiler”工程页面的“SystemContents”栏下出现“IMEofTsinghuaUniv./Binary_VGA_Controller_IF”。

选择Verilog,表示“SOPCBuilder”会将你稍后所配置的IP,以Verilog表示,若你熟悉VHDL,也可以选择VHDL。

这里的设定不是限制了日后只能用Verilog或VHDL写代码,因为QuartusII本来就允许Verilog与VHDL混合編程,也就是说Verilog的module可以使用VHDL的entity,VHDL的entity可以使用Verilog的module,最后都能顺利编译。

如果配置硬件的过程中暂停设计,关闭“SOPCBuilder”工具页面会弹出一个问句,如图7-13所示。

鼠标左键单击“Save”按钮,建立的硬件系统信息就保存到路径“E:

/demo/demo_VGAcontroller”下的文件“nios0.sopc”中。

任何时候,如果需要打开此工程的“SOPCBuilder”工具页面完成后续的硬件配置的话,可以先打开“QuartusII-E:

/demo/demo_VGAcontroller/demo_vga-demo_vga”工程页面(方法如图7-9所示),在工程页面内,鼠标左键单击“open”按钮弹出“打开”页面。

在“查找范围”找到路径“E:

\demo\demo_VGAcontroller”下的“nios0.sopc”文件,鼠标左键双击“nios0.sopc”文件即可打开本工程的“SOPCBuilder”工具页面。

(四)配置硬件

1.定义时钟

确认“SOPCBuilder”工具页面的“Target/DeviceFamily”是“CycloneII”。

在如图7-14所示的“ClockSettings”栏里可以看到50.0MHz,代表NiosIICPU在DE2-70可以运行在50.0MHz,但这时CPU降频在跑,正常情況下,NiosIICPU在DE2-70可以运行100.0MHz,所以可以用PLL将clk倍频成100.0Mhz。

2.增加用来保存Nios程序的片上存储器(OnChipMemory(RAMorROM))

“OnChipMemory”在FPGA芯片内,是DE2-70上所有存储器中存储量最小,但是速度最快的存储器。

在“SOPCBuilder”工具页面,鼠标左键单击SystemContents->ComponentLibrary->MemoriesandMemoryControllers->OnChip->OnChipMemory(RAMorROM)->Add。

弹出“onchipmemory”设置页面,如图7-15所示。

在“onchipmemory”设置页面:

“TotalMemorySize”设置为80960;其他为缺省设置,鼠标左键单击“Finish”按钮。

不用管状态框里的错误,添加Nios处理器后会自动消失。

“Totalmemorysize”与能使用的M4K存储器数量、FPGA、NiosIICPU和Megafunction(如fcfifo)都会影响“On-chipMemory”的size,本教程使用80k。

“OnChipMemory”会在“SOPCBuilder”工具页面默认空白区有显示如图7-16所示。

如果想修改“OnChipMemory”的设置,可以左键双击硬件名称,会重新弹出如图7-15所示的设置页面。

对于其他硬件来说,方法类似。

把“onchip_memory2_0”改成“onchip_mem”。

3.添加NiosII/s处理器(NiosIIProcessor)

在“SOPCBuilder”工具页面,鼠标左键单击SystemContents->ComponentLibrary->NiosIIProcessor->Add,弹出“NiosIIProcessor”设置页面。

在“NiosIIProcessor”设置页面:

CPU设置为NiosII/e处理器;ResetVector和ExceptionVector都指向速度最快的存储器,通常是on-chipmemory或SSRAM,如图7-17所示。

鼠标左键单击“Finish”按钮,把“cpu_0”改成“cpu”。

4.添加调试接口(JTAG-UART)

在“SOPCBuilder”工具页面,鼠标左键单击SystemContents->ComponentLibrary->InterfaceProtocols->Serial->JTAGUART->Add,弹出“JTAGUART”设置页,如图7-18所示。

使用缺省设置,鼠标左键单击“Finish”按钮。

把“jtag_uart_0”改成“jtag_uart”。

JTAGUART是PC与SOPC进行序列传输的一种方式,也是NiosIICPU标准的输出/输入设备。

如printf()通过JTAGUART,经过USBBlaster将输出结果显示在PC的NiosIIEDS上的console,scanf()通过USBBlaster经过JTAGUART将输入传给SOPC。

5.添加两个内部定时器(IntervalTimer)

在“SOPCBuilder”工具页面,鼠标左键单击SystemContents->ComponentLibrary->Peripherals->MicrocontrollerPeripherals->IntervalTimer->Add,弹出“IntervalTimer”设置页,按照图7-19所示设置,鼠标左键单击“Finish”按钮。

把“timer_0”改成“timer”。

6.添加系统ID(SystemID)

在“SOPCBuilder”工程页面,鼠标左键单击SystemContents->ComponentLibrary->Peripherals->DebugandPerformance->SystemIDPeripheral->Add,弹出“SystemIDperipheral”设置页面,如图7-20所示。

使用缺省设置,鼠标左键单击“Finish”按钮,把“sysid_0”的名称改为“sysid”。

“SOPCBuilder”会使用SystemID为每个系统提供识别符号,NiosIIEDS可以识别符号防止使用者往FPGA上烧录了与“.ptf”不符合的“.sof”。

7.增加PLL

在“SOPCBuilder”工具页面,鼠标左键单击SystemContents->ComponentLibrary->PLL->PLL->Add。

在弹出的对话框里,鼠标左键单击“LaunchAltera’sALTPLLMegaWizard”,使按钮周框内侧出现虚方框,如图7-21所示。

鼠标左键单击“next”按钮,进入ALTPLL多项设置页面。

默认进入的页面是:

1parametersettings栏的“General/Modes”设置页,显示为:

1parametersettings为深兰色背景,“General/Modes”为General/Modes,如图7-22左上角所示,此页缺省设置。

鼠标左键单击2outputclocks栏,默认转换到“c0-Core/Externaloutputclocks”的设置页面,在“c0-Core/Externaloutputclocks”的设置页面:

2outputclocks为深兰色背景,“clkc0”为clkc0,“clkc0”各参数按照图7-23所示页面设置。

图7-23

鼠标左键单击“Finish”按钮,并且单击经过的所有页面的“Finish”按钮。

设置了PLL后,在本工程硬件系统的“SOPCBuilder”工具页面,“ClockSettings”栏下:

“clk_0”改名为“clk_50”;

“pll_0_c0”改名为“clk_25”,如图7-24所示。

8.添加inputPIO

在“SOPCBuilder”工程页面,鼠标左键单击SystemContents‐>ComponentLibrary‐>Peripherals‐>MicrocontrollerPeripherals‐>PIO(ParallelI/O)‐>Add,弹出“PIO(ParallelI/O)”多项设置页面。

默认进入“ParameterSettings”的“BasicSettings”设置页面,如图7-25所示。

此页设置:

“Width”为4;“Direction”为input;其他为默认值。

鼠标左键单击“InputOptions”标签,弹出“InputOptions”设计页面,按照如图7-26所示设置。

将该硬件的名称改为“button_pio”,作为连接KEY0~1的PIO。

9.添加outputPIO

在“SOPCBuilder”工具页面,鼠标左键单击SystemContents‐>ComponentLibrary‐>Peripherals‐>MicrocontrollerPeripherals‐>PIO(ParallelI/O)‐>Add。

弹出“PIO(ParallelI/O)”多项设置页面。

在此页设置:

“Width”为8;“Direction”为output;其他为默认值,如图7-27所示。

将名称改为“led_pio”,作为连接绿LED的PIO。

10.添加VGA控制器

在“SOPCBuilder”工具页面,鼠标左键单击SystemContents‐>ComponentLibrary‐>IMEofTsinghuaUinv.‐>Binary_VGA_Controller_IF‐>Add,弹出“Binary_VGA_Controller_IF”设置页,全部缺省设置,鼠标左键单击“Finish”,该硬件名字改为“VGA”。

至此,已经完成了“nios0”硬件系统的搭建,结构如图7-28所示。

鼠标左键单击各个元器件“Clock”,会出现下拉三角,左键点开下拉三角:

全部器件选择“clk_50”。

(五)产生“.ptf”文件

在“SOPCBuilder”工程页面,鼠标左键单击System‐>Auto‐AssignBaseAddresses,菜单自动设置映射地址;

在“SOPCBuilder”工程页面,鼠标左键单击System‐>Auto‐AssignIRQs菜单自动设置中断号,中断号越小,优先级越高。

一般把Timer的优先级设为最高。

然后,在“SOPCBuilder”工程页面,鼠标左键单击“Generate”。

如果弹出问句,鼠标左键单击“Save”按钮。

“Generate”过程中,弹出的页面下面有进度提示,如图7-29所示。

“Generate”完成后点击“Exit”退出。

弹出“是否保存”的问句,鼠标左键单击“Save”。

这里需要注意:

“Generate”完成后生成的“.ptf”文件和其他文件都自动保存在路径“E:

/demo/demo_VGAcontroller”下。

在“QuartusII-E:

/demo/demo_VGAcontroller/demo_vga-demo_vga”工程页面,打开此实验的工程文件夹“demo_VGAcontroller”,可以看到生成的文件如图7-30所示。

特别需要注意“nios0_inst.v”文件,这个文件内容是编写顶层文件时,例化“nios0”的参考模板。

(六)编写顶层文件

“SOPCBuilder”工具已经产生了“nios0”硬件系统,下面要在QuartusII里例化“nios0”,并和其他的逻辑电路、芯片的输入输出管腿连接。

例化“nios0”可以用原理图方法,或者用Verilog编写顶层文件。

此处,采用“VerilogHDL”语言编写顶层文件例化“nios0”系统。

在“QuartusII-E:

/demo/demo_VGAcontroller/demo_vga-demo_vga”工程页面,鼠标左键单击File‐>New‐>VerilogHDLFile,打开“.v”文件录入区。

如图7-31中的红色箭头所示区内可以看到一条闪烁的录入光标。

就像平时使用word文档时一样,把下列篇幅中提供的“demo_vga.v”内容拷贝进去。

“demo_vga.v”内容:

moduledemo_vga(

inputiCLK_50,

output[9:

0]oVGA_B,

output[9:

0]oVGA_G,

output[9:

0]oVGA_R,

outputoVGA_CLOCK,

outputoVGA_BLANK_N,

outputoVGA_SYNC_N,

outputoVGA_HS,

outputoVGA_VS,

input[3:

0]iKEY,

output[7:

0]oLEDG

);

wirereset_n=1'b1;

wireclk_25;

//SetusuptheDut

nios0

(

.avs_s1_export_iCLK_25_to_the_vga(clk_25),//VGAIPInputClock

.avs_s1_export_VGA_R_from_the_vga(oVGA_R),//VGARoutputtoADV7123

.avs_s1_export_VGA_G_from_the_vga(oVGA_G),//VGAGoutputtoADV7123

.avs_s1_export_VGA_B_from_the_vga(oVGA_B),//VGABoutputtoADV7123

.avs_s1_export_VGA_CLK_from_the_vga(oVGA_CLOCK),//VGAClockoutputtoADV7123

.avs_s1_export_VGA_BLANK_from_the_vga(oVGA_BLANK_N),//VGABlankoutputtoADV7123

.avs_s1_export_VGA_SYNC_from_the_vga(oVGA_SYNC_N),//VGASYNCoutputtoADV7123

.avs_s1_export_VGA_HS_from_the_vga(oVGA_HS),//VGAHSoutputtoDB15Socket

.avs_s1_export_VGA_VS_from_the_vga(oVGA_VS),//VGAVSoutputtoDB15Socket

.clk_25(clk_25),//PLL25MHzoutput

.in_