EDA四选一选择器设计Word文档格式.doc

《EDA四选一选择器设计Word文档格式.doc》由会员分享,可在线阅读,更多相关《EDA四选一选择器设计Word文档格式.doc(5页珍藏版)》请在冰点文库上搜索。

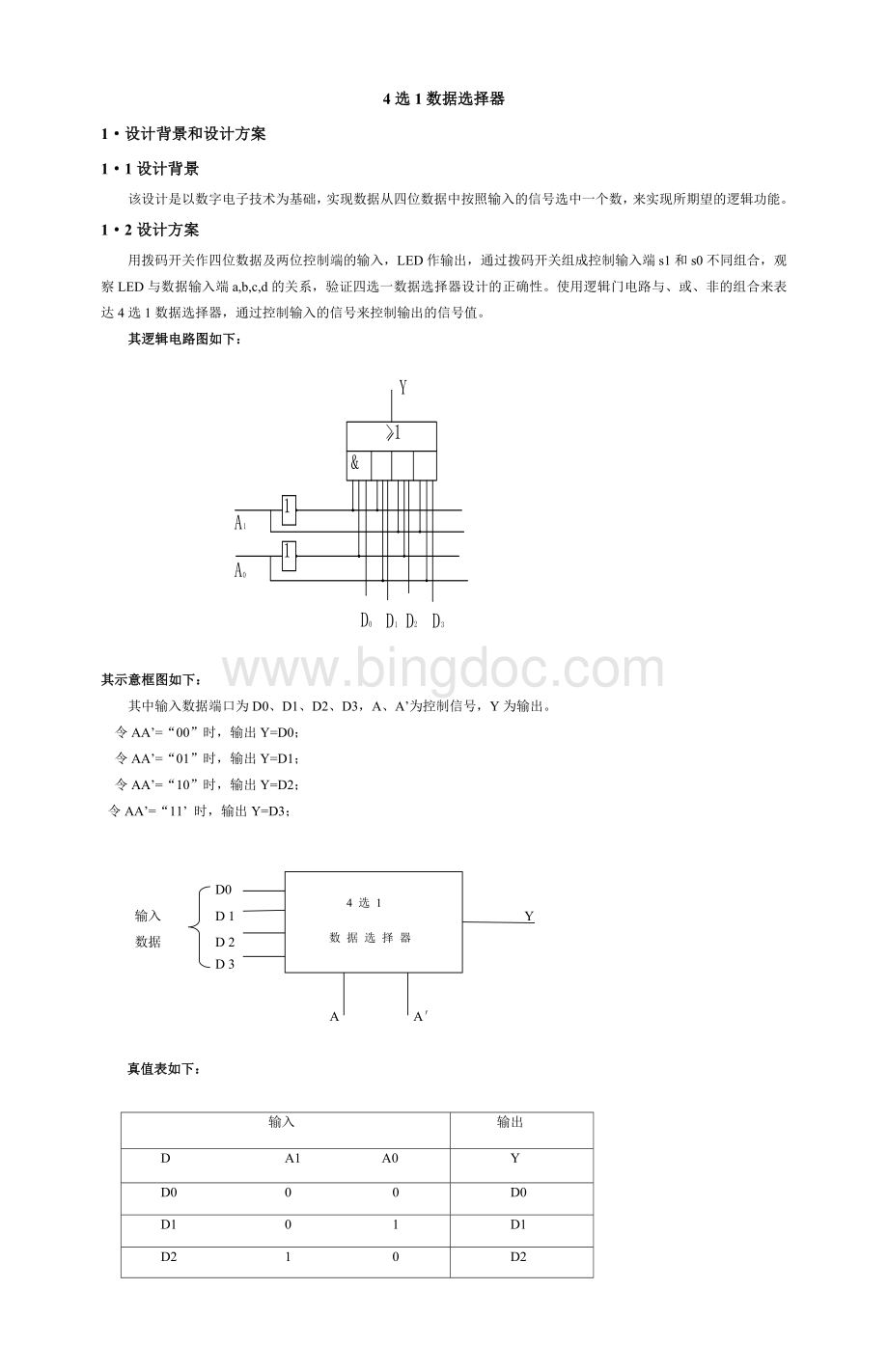

令AA’=“10”时,输出Y=D2;

令AA’=“11’时,输出Y=D3;

4选1

数据选择器

D0

输入D1Y

数据D2

D3

AA′

真值表如下:

输入

输出

DA1A0

Y

D000

D0

D101

D1

D210

D2

D311

D3

2·

方案实施

1)程序1

1

设计思路

四选一多路选择器设计时,定义输入S为标准以内漏记为STD_LOGIC,输出的信号Z的数据类型定义为2位标准逻辑矢量位STD_LOGIC_VECTOR(1DOWNTO0).使用LIBRATY语句和USE语句,来打开IEEE库的程序包STD_LOGIC_1164.ALL。

当输入信号时,程序按照输入的指令来选择输出,例如输入信号为“00”时,将a的值给z,进而输出z的值,输入信号为“11”是,将a的值给z,进而输出z的值。

若输入信号是已经定义的四个信号之外的值时(即当IF条件语句不满足时),输出值为x,并将x的值给输出信号z。

这样即可实现四选一数据选择的功能。

2

程序

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYmux41is

PORT(a,b,c,d:

INSTD_LOGIC;

s:

INSTD_LOGIC_VECTOR(1DOWNTO0);

z:

OUTSTD_LOGIC);

ENDmux41;

ARCHITECTUREoneOFmux41IS

BEGIN

PROCESS(s,a,b,c,d)

BEGIN

CASEsIS

WHEN"

00"

=>

z<

=a;

01"

=b;

10"

=c;

11"

=d;

WHENOTHERS=>

=null;

ENDCASE;

ENDPROCESS;

ENDone;

3

运行结果

当输入信号“00”时,输出信号z的值为‘a’;

当输入信号“01”时,输出信号z的值为‘b’;

当输入信号“10”时,输出信号z的值为‘c’;

当输入信号“11”时,输出信号z的值为‘d’;

4

波形仿真及描述

输入:

a的波形周期为10ns,b的波形周期为5ns,c的波形周期为15ns,d的波形周期为8ns。

s[1]的波形周期为5ns,s[2]的波形周期为10ns。

输出:

2)程序2

定义6个输入信号,一个输出信号,当控制信号A=‘1’时,muxval的值加1,即muxval=muxval+1;

当控制信号B=‘1’时muxval的值加2,即muxval=muxval+2。

当输入值为‘i0’时,输出q的值为0,当输入的值为‘i1’时,输出q的值为1,当输入值为‘i2’时,输出q的值为2,当输入值为‘i3’时,输出q的值为3。

2程序

ENTITYmux41IS

PORT(i0,i1,i2,i3,a,b:

INSTD_LOGIC;

q:

OUTSTD_LOGIC);

ENSmux4;

ARCHITECTUREb_mux4OFmux4IS

Process(i0,i1,i2,i3,a,b)

Variablemuxval:

integerrang7downto0;

Begin

muxval:

=0;

if(a='

1'

)thenmuxval:

muxval+1;

endif;

if(b='

muxval+2;

casemuxvalis

when0=>

q<

=i0;

when1=>

=i1;

when2=>

=i2;

when3=>

=i3;

Whenothers=>

null;

endcase;

endprocess;

ENDb_mux4;

当输入信号“00”时,输出信号z的值为‘i0’;

当输入信号“01”时,输出信号z的值为‘i1’;

当输入信号“10”时,输出信号z的值为‘i2’;

当输入信号“11”时,输出信号z的值为‘i3’;

a的波形周期为20ns,b的波形周期为15ns,c的波形周期为20ns,d的波形周期为15ns,s[1]的波形周期为8ns,s[2]的波形周期为16ns。

3·

结果和结论

经过对以上程序的运行和编译,可得出以下仿真图结论和所设计一致。

4·

参考文献

[1]余孟尝主编《数字电子技术基础简明教程》,1998-12。

[2]潘松黄继业编著《EDA技术使用个教程》,2006-9。