第5章-锁存器和触发器.doc

《第5章-锁存器和触发器.doc》由会员分享,可在线阅读,更多相关《第5章-锁存器和触发器.doc(9页珍藏版)》请在冰点文库上搜索。

5锁存器和触发器

5.2锁存器

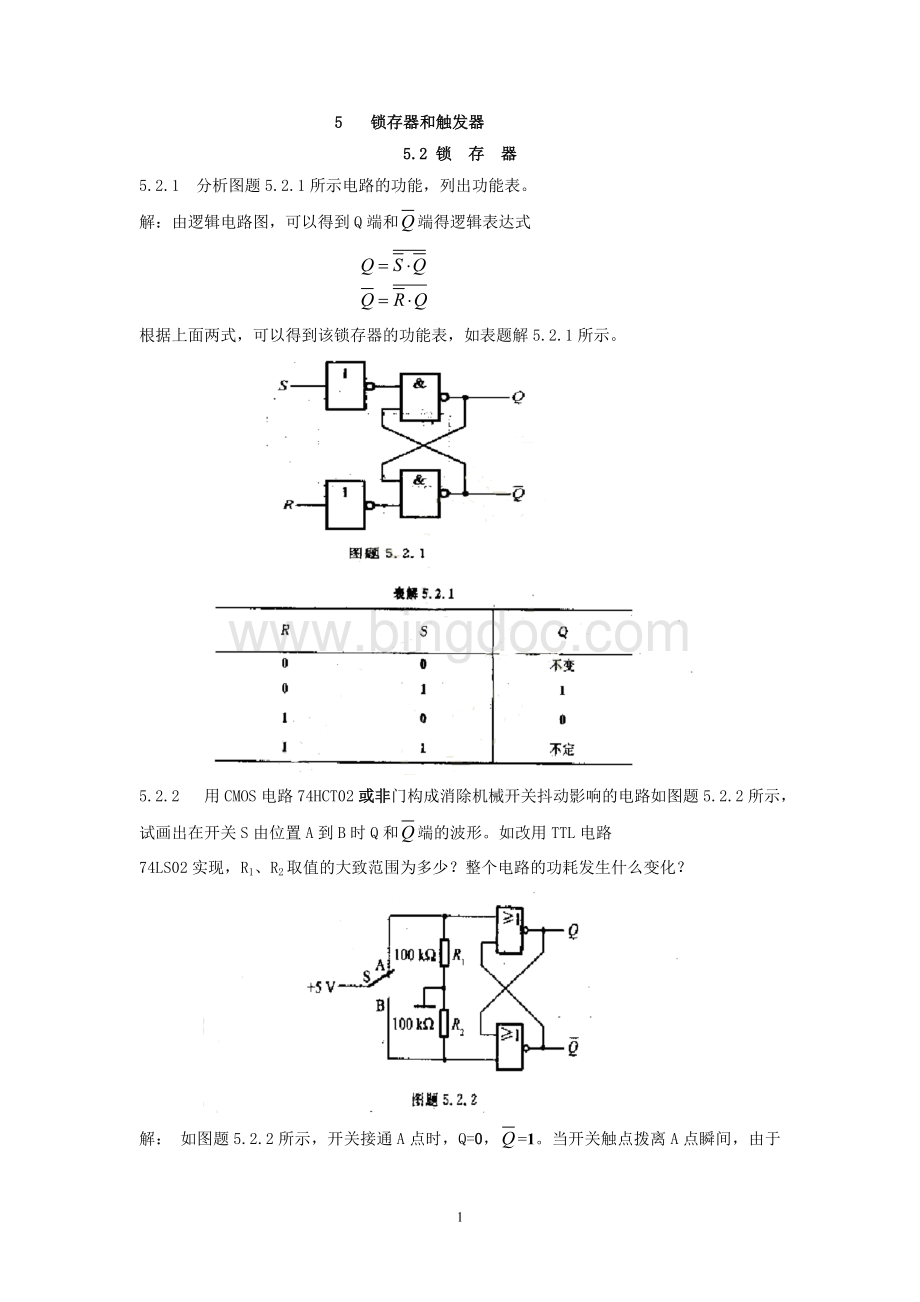

5.2.1分析图题5.2.1所示电路的功能,列出功能表。

解:

由逻辑电路图,可以得到Q端和端得逻辑表达式

根据上面两式,可以得到该锁存器的功能表,如表题解5.2.1所示。

5.2.2用CMOS电路74HCT02或非门构成消除机械开关抖动影响的电路如图题5.2.2所示,试画出在开关S由位置A到B时Q和端的波形。

如改用TTL电路

74LS02实现,R1、R2取值的大致范围为多少?

整个电路的功耗发生什么变化?

解:

如图题5.2.2所示,开关接通A点时,Q=0,=1。

当开关触点拨离A点瞬间,由于=1的作用,其抖动不会影响Q=0的状态。

在开关悬空期间,锁存器保持状态不变。

开关触点第一次接通B点,就使翻转为0,Q翻转为1.此时开关触点已离开A点,在Q=1的作用下,即使触点的抖动会使B点电平发生跳动,也不会改变=0的状态。

该过程中的Q和的波形如图题解5.2.2(a)所示。

如果改用TTL电路74LS02实现,由于其输入电路如图题解5.2.2(b)点画线框

内所示,所以当开关未接通A点时,电源﹢VCC将通过集成电路内部的电阻r1和肖特基二极管D1向电路外接电阻R1注入电流。

如果R1阻值过大,在该电阻上产生的压降有可能超过TTL电路所允许的低电平输入电压最大值,从而电路可能发生逻辑混乱。

可以列出下列不等式

74LS系列电路规定VCC=﹢5V,=0.8V。

74LS02中,r�1的典型值为20kΩ,肖特基二极管正向导通时的典型压降=0.4V。

将上述参数代入不等式,可得R1≤4.2kΩ。

为了降低电路功耗,R1取值不宜过小,一般应大于500Ω。

所以R1得取值范围应为500Ω≤R1≤4.2kΩ

的取值与R1相同。

TTL电路的静态功耗大于CMOS电路,同时考虑到R1和R2的功耗,用74LS02构成图题5.2.2所示的电路,功耗将显著增大。

5.2.5若图5.2.8(a)所示电路的初始状态为Q=1,E、S、R端的输入信号如图题5.2.5所示,试画出相应Q和端的波形。

解:

设初态Q=1,按照图题5.2.5所示波形,推导出图5.2.8(a)电路的输出端Q和的波形如图题解5.2.5所示。

5.3触发器的电路结构和工作原理

5.3.1触发器的逻辑电路如图题5.3.1所示,确定其属于何种电路结构的触发器并分析工作原理。

解:

图题5.3.1所示电路是由两个传输门控D锁存器级联构成的COMS主从D触发器。

其中G1、G2构成主锁存器,G3、G4构成从锁存器。

、分别为直接置

1端和直接置0端,当触发器处于以下触发工作状态时,应将它们置为高电平。

(1)当CP=0时,,TG1和TG4导通,TG2和TG3断开。

D端信号进入主锁存器,G1输出为,并随D变化。

由于TG3断开、TG4导通,主、从锁存器相互隔离,从锁存器构成双稳态存储单元,使触发器输出维持原来的状态不变。

(2)当CP由0跳变到1后,0,C=1,TG1和TG4断开,TG2和TG3导通。

这时D端与主锁存器之间的联系被切断,TG2的导通使主锁存器维持在CP上升沿到来前瞬间的状态。

同时由于TG3导通,G1输出信号送至Q端,得到=D,并在CP=1期间维持不变。

(3)当CP由1跳变到0后,则再次重复

(1)的过程。

5.3.2触发器的逻辑电路如图题5.3.2所示,确定其应属于何种电路结构的触发器。

解:

图题5.3.2所示的电路是由两个逻辑门控SR锁存器级联构成的主从SR触发器。

5.4触发器的逻辑功能

5.4.1上升沿触发和下降沿触发的D触发器逻辑符号及时钟信号CP()和D的波形如图题5.4.1所示。

分别画出它们的Q端波形。

设触发器的初始状态为0。

解:

设触发的触发器输出波形为Q1,CP触发的触发器输出的波形为Q2,二者波形如图题解5.4.1所示。

5.4.2设下降沿触发的JK触发器初始状态为0,、J、K信号如图题5.4.3所示,试画出触发器Q端的输出波形。

解:

Q端的波形如图题解5.4.3所示。

5.4.3逻辑电路如图题5.4.4所示,试画出在CP作用下,φ0、φ1、φ2和φ3的波形。

解:

由逻辑电路图和SR触发器特性方程

可列出表达式

设初态Q1=Q0=0,列出真值表,如表题解5.4.4所示。

继而画出波形图。

如图题解5.4.4所示。

5.4.5电路如图题5.4.5所示,设各触发器的初态为0,画出在脉冲作用下Q端的波形。

解:

由JK触发器的特性方程,对照图题5.4.5各触发器电路可得:

于是,画出各触发器Q端的波形,如图题解5.4.5所示。

5.4.6逻辑电路如图题5.4.6所示,已知和X的波形,试画出Q1和Q2的波形。

触发器的初始状态为0。

5.4.7逻辑电路如图题5.4.7所示,已知和A的波形,画出触发器Q端的波形,设触发器的初始状态为0。

解:

如题5.4.7所示电路Q端的波形如图题解5.4.7所示。

5.4.8两相脉冲产生电路如图题5.4.8所示,试画出在作用下φ1、φ2的波形,并说明φ1和φ2的时间关系。

各触发器的初始状态为0。

解:

由图题5.4.8得φ1、φ2的逻辑表达式:

φ1=Q2,。

、的波形图如图题解5.4.8所示。

由波形图可知φ1超前φ2一个周期。

5.4.9逻辑电路和各输入信号波形如图题5.4.9所示,画出两触发器Q端的波形。

两触发器的初始状态均为0。

解:

图题5.4.9中Q1、Q2的波形图如题解5.4.9所示。

5.4.10逻辑电路和输入信号波形如图题5.4.10所示,画出各触发器Q端的波形。

触发器的初始状态均为0。

解:

图题5.4.10中的R端是异步置零端,高电平有效,当R=1时Q=0。

先列真值表,如表题解5.4.10所示。

分别分析CP1和R1对Q1的影响及CP2和对的影响,画出如图题解5.4.10所示波形。

9