固态硬盘控制器设计 需求分析文档.docx

《固态硬盘控制器设计 需求分析文档.docx》由会员分享,可在线阅读,更多相关《固态硬盘控制器设计 需求分析文档.docx(9页珍藏版)》请在冰点文库上搜索。

固态硬盘控制器设计需求分析文档

需求分析描述文档

项目名称:

固态硬盘控制器设计

小组成员:

一、用例描述

1.项目背景:

随着信息技术的发展,人们对数据处理速度的要求越来越高,而基于温彻斯特技术的传统机械硬盘虽然仍广泛的应用各种数据存储环境中,其缺点却越来越不容忽视:

读写速度慢、存储性能不稳定、功耗大、噪音大等,尤其是读写速度和硬盘容量已经成为计算机技术发展的瓶颈。

因此传统硬盘已经不能满足人们对数据存储的需求。

近年来闪存芯片等半导体存储器快速发展,以闪存芯片等为存储介质的固态硬盘也越来越成熟,其具有高数据传输率、低功耗、低噪音、性能稳定等优点,逐渐成为传统机械硬盘的理想替代品,每年都有大量的固态硬盘和混合硬盘被用户使用。

固态硬盘设计的核心技术就是固态硬盘控制器的设计,其主要功能包括对闪存芯片等半导体存储器的管理和对外部处理器(存储设备使用者)提供硬盘接口。

而FPGA作为发展快速的先进半定制集成电路芯片,能够快速实现许多功能电路,被广泛应用在各种电路的设计。

本项目即为应用FPGA设计固态硬盘控制器,在一块FPGA芯片上通过VHDL编程实现固态硬盘控制器的功能,以NandFlash芯片为存储介质,实现固态硬盘的功能。

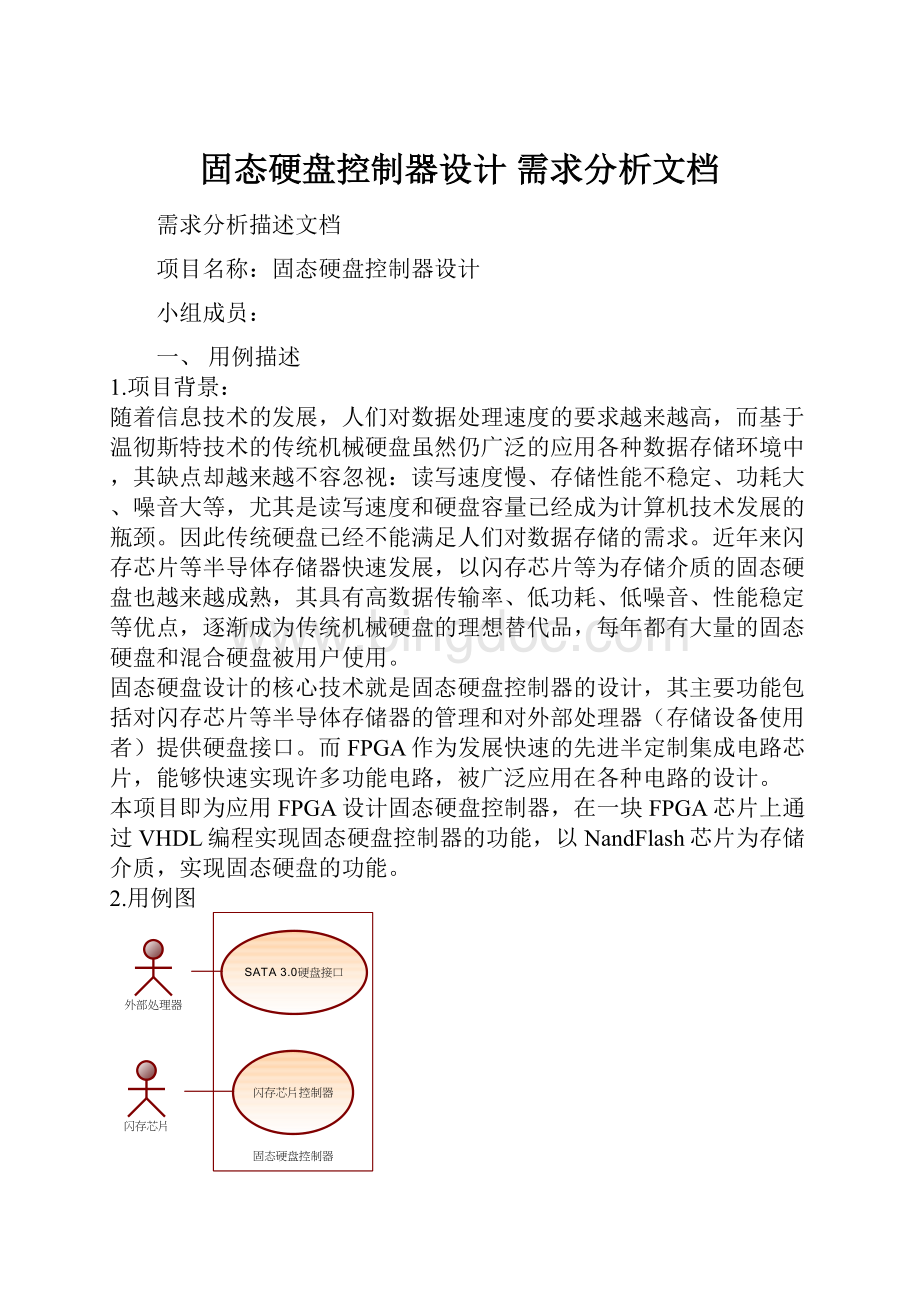

2.用例图

图1固态硬盘控制器用例图

3.用例场景描述

本项目所设计的固态硬盘可应用在各种存储环境,对外有两个接口:

标准硬盘接口,与存储设备的使用者(外部处理器等)相连,为使用者提供大容量的存储空间;nandflash芯片接口,与nandflash芯片相连,对存储芯片进行管理和控制。

总体而言,固态硬盘控制器拥有两个外部用户:

外部处理器和nandflash芯片,分别通过两个不同的接口传输数据和控制命令。

图2固态硬盘控制器外部视图

由图2可见,外部用户向固态硬盘控制器发送控制命令(如读命令、写命令)、地址信息,固态硬盘控制器将接收到的控制命令和地址信息经过分析和转换,继续传递给NandFlash阵列,NandFlash阵列接收地址信息后,根据控制命令进行相应的数据存取操作。

4.固态硬盘系统时序图

图3.读操作系统时序图

读操作时,处理器向固态硬盘(SSD)发送读命令,接着发送地址信息(逻辑地址),然后固态硬盘进行内部读操作,将数据输出传给处理器。

见图3。

写操作时,处理器向固态硬盘发送写命令,然后发送地址信息,接着发送数据到固态硬盘缓存器缓存,固态硬盘进行内部写操作,将缓存器中的数据存储至NandFlash芯片。

见图4。

固态硬盘控制器内部业务功能描述

1.固态硬盘控制器内部结构

固态硬盘控制器包含三个IP核:

SATA协议IP核,MicroBlaze软处理器核,NandFlash控制器IP核。

内部结构见图5。

本项目就是在一块FPGA芯片上实现上述三个IP核。

图5固态硬盘控制器内部结构图

2.固态硬盘内部业务功能描述

MicroBlaze软处理器核:

MicroBlaze嵌入式软核是一个被Xilinx公司优化过的可以嵌入在FPGA中的RISC处理器软核,具有运行速度快、占用资源少、可配置性强等优点,广泛应用于通信、军事、高端消费市场等领域。

MicroBlaze是基于Xilinx公司FPGA的微处理器IP核,和其它外设IP核一起,可以完成可编程系统芯片(SOPC)的设计。

MicroBlaze处理器采用RISC架构和哈佛结构的32位指令和数据总线,可以全速执行存储在片上存储器和外部存储器中的程序,并访问其的数据。

MicroBlaze作为固态硬盘控制器的核心部分,主要提供处理SATA的控制命令、数据流的分发、NANDFLASH文件系统和阵列管理的功能。

本设计中移植MicroBlaze软控制器核到FPGA芯片中并编写实现相关控制命令。

SATAIP核:

SATA的全称是SerialAdvancedTechnologyAttachment(串行高级技术附件),是一种基于行业标准的串行硬件驱动器接口,是由Intel、IBM、Dell、APT、Maxtor和Seagate公司共同提出的硬盘接口规范,是目前最通用的硬盘接口标准。

SATA协议分为四层:

应用层、传输层、链路层、物理层,其体系结构图见图6。

图6SATA协议体系结构图

应用层面向顶层,负责所有ATA命令的执行,生成读写请求,并可读取和设置设备的工作性能模式,包括对控制命令模块寄存器的访问;传输层根据应用层的读写请求和来自数据链路层的应答启动数据包的传送,传输层在主机和硬盘设备之间以帧信息结构(FIS)的形式传输控制命令和数据;链路层通过维持数据的完整性来保证数据包通过链路可靠地传输。

它包括8B/10B编解码,数据包的循环冗余校验(CRC),并可在信号失败时自动重新尝试数据包传送。

链路层发送和接收数据包,并发送来自于传输层的控制信号的原始字符,接收来自于物理层的原始字符并将其转化为控制信号给传输层;物理层包含两条高速单工通道的低压差分信号收发器,分别负责接收和发送数据。

本设计中,SATA部分主要负责对外部处理器提供一个统一硬盘接口,实现外部处理器与固态硬盘控制器之间的通信。

IP核实现SATA3.0协议的各层功能,并采用Xilinx公司Virtex-4系列FPGA内部集成的千兆级收发器(RoeketlOMGT)实现物理层传输。

NandFlash控制器IP核:

NANDFLASH控制器核实现NANDFLASH芯片控制和管理,根据NANDFLASH闪存芯片指令系统和接口时序,移植PicoBlaze可编程状态机实现NANDFLASH芯片控制,将复杂的NANDFLASH接口转化成简单通用的SRAM接口,提高系统主控制器的访问效率,并设计实现ECC检验算法,保证数据存储和读取正确。

3.固态硬盘控制器顺序图

固态硬盘控制器所进行的操作(活动)分为读操作和写操作,分别由不同的对象以及对象之间的一系列活动实现。

①读操作顺序图:

见图7。

图7固态硬盘控制器读操作顺序图

外部用户(处理器)要进行读操作,则首先向SATAIP核发送读命令,接着发送地址信息至SATAIP核的地址缓存器中。

SATAIP核将接收到的读命令和地址信息进行解析,然后发送给MicroBlaze软处理器核(即MicroController)。

MicroBlaze软处理器核先向NandFlash控制器IP核发送读命令,然后将接收到的地址信息解析(即将外部处理器的逻辑地址转换为NandFlash阵列中的物理地址),将解析出来的地址信息发送至NandFlash控制器。

Nandflash控制器将接收到的读命令和地址信息以符合Nandflash芯片接口的格式发送给NandFlash芯片阵列,即对NandFlash芯片进行读操作。

NandFlash芯片按地址读出数据,依次经过NandFlash控制器IP核、MicroBlazeIP核和SATAIP核发送给外部处理器。

②写操作顺序图:

见图8.

图8写操作顺序图

写操作顺序图与读操作顺序图大致相同,但在进行写操作时,外部处理器在发送完写命令和地址信息后,立即将要写入的数据发送至SATAIP核的缓存器中储存。

SATAIP核和MicroBlaze软处理器核同样是将数据先发送至下一级IP核的缓存器中缓存。

而NandFlash控制器IP核在发送完地址信息后还要发送一个擦除命令,即将要写入数据的存储空间预先擦除(如果存储空间原本为空则不进行擦除操作),然后写入数据。

4.固态硬盘控制器设计工作要求

在FPGA中使用VHDL设计SATAIP核和NandFlash控制器IP核,并移植MicroBlaze软处理器核,完成三个IP核之间的通信,并通过MicroBlaze软处理器核对SATAIP核和NandFlash控制器IP核进行管理,处理SATA的控制命令、数据流的分发、NANDFLASH文件系统和阵列管理。

逻辑框图见图9.