EDA电子钟课程设计.docx

《EDA电子钟课程设计.docx》由会员分享,可在线阅读,更多相关《EDA电子钟课程设计.docx(16页珍藏版)》请在冰点文库上搜索。

EDA电子钟课程设计

多功能数字钟

设计说明:

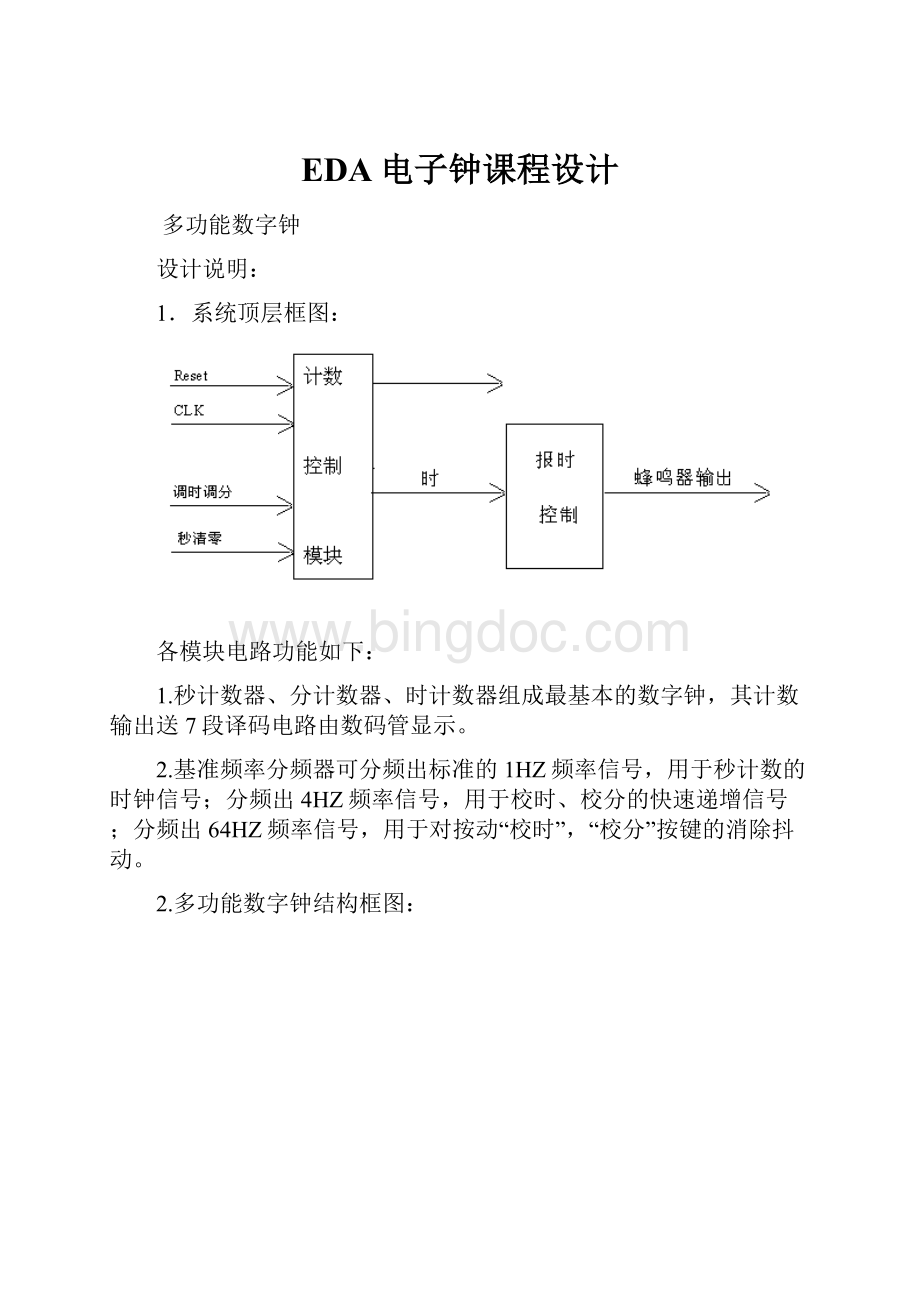

1.系统顶层框图:

各模块电路功能如下:

1.秒计数器、分计数器、时计数器组成最基本的数字钟,其计数输出送7段译码电路由数码管显示。

2.基准频率分频器可分频出标准的1HZ频率信号,用于秒计数的时钟信号;分频出4HZ频率信号,用于校时、校分的快速递增信号;分频出64HZ频率信号,用于对按动“校时”,“校分”按键的消除抖动。

2.多功能数字钟结构框图:

一、系统功能概述

已完成功能

1.完成时/分/秒的依次显示并正确计数,利用六位数码管显示;

2.时/分/秒各段个位满10正确进位,秒/分能做到满60向前进位,有系统时间清零功能;

3.定时器:

实现整点报时,通过扬声器发出高低报时声音;

4.时间设置,也就是手动调时功能:

当认为时钟不准确时,可以分别对分/时钟进行调整;

5.闹钟:

实现分/时闹钟设置,在时钟到达设定时间时通过扬声器响铃。

有静音模式。

待改进功能:

1.系统没有万年历功能,正在思考设计方法。

2.应添加秒表功能。

二、系统组成以及系统各部分的设计

1.时计数模块

时计数模块就是一个2位10进制计数器,记数到23清零。

VHDL的RTL描述如下:

----cnt_h.vhd

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitycnt_his

port(en,clk,clr:

instd_logic;

dout:

outstd_logic_vector(7downto0);

c:

outstd_logic);

endcnt_h;

architecturertlofcnt_his

signalt:

std_logic_vector(7downto0);

begin

process(en,clk,clr)

variablet:

std_logic_vector(7downto0);

begin

ifen='1'then--异步使能

ifclk'eventandclk='1'then

t:

=t+1;

ift(3downto0)=X"A"then--个位等于10则十位加1

t(7downto4):

=t(7downto4)+1;

t(3downto0):

=X"0";--个位清零

endif;

ift>X"23"then--大于23清零

t:

=X"00";

endif;

endif;

ifclr='1'then--异步清零

t:

=X"00";

endif;

endif;

dout<=t;

endprocess;

endrtl;

时计数器模块仿真波形如下

从仿真波形可知,当计数到23时,下一个时钟上升沿到来时就清零了,符合设计要求。

时计数模块框图如下

2.分及秒计数模块

分及秒计数模块也是一个2位10进制计数器,记数到59清零。

VHDL的RTL描述如下:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitycnt_sis

port(en,clk,clr:

instd_logic;

dout:

bufferstd_logic_vector(7downto0);

c:

outstd_logic);

endcnt_s;

architecturertlofcnt_sis

begin

process(en,clk,clr)

begin

ifen='1'then

ifclr='1'then--异步清零

dout<=X"00";

elsifclk'eventandclk='1'then

ifdout(3downto0)<9then

dout(3downto0)<=dout(3downto0)+1;

c<='0';

elsifdout(7downto4)<5then

dout(3downto0)<=X"0";

dout(7downto4)<=dout(7downto4)+1;

else

dout<=X"00";

c<='1';

endif;

endif;

elsedout<="ZZZZZZZZ";

endif;

endprocess;

endrtl;

分和秒计数器模块仿真波形如下

从仿真波形可知,当计数到59时,下一个时钟上升沿到来时就清零了,并且产生进位信号,符合设计要求。

分和秒计数模块框图如下

3.按键消抖动模块

按键消抖动有很多方案,这里选择的是计数消抖,即只当有效电平到来后开始计数,当计数值大于一定值后再输出该有效电平,否则不输出,从而达到消抖目的。

VHDL的RTL描述如下:

libraryieee;

useieee.std_logic_1164.all;

entityhaoinis

port(din,clk:

instd_logic;

dout:

outstd_logic);

endhaoin;

architecturertlofhaoinis

begin

process(din)

variablet:

integerrange0to63:

=0;

begin

ifdin='1'then

ifclk'eventandclk='1'then

t:

=t+1;

ift>10then

dout<='1';t:

=t-1;

elsedout<='0';

endif;

endif;

elsedout<='0';t:

=0;

endif;

endprocess;

endrtl;

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityringis

port(

clk:

instd_logic;

clk500:

instd_logic;

clk1k:

instd_logic;

beep:

outstd_logic);

endring;

architecturertlofringis

begin

process(clk)

variablet:

std_logic;

variablen:

integerrange0to15:

=0;

begin

ifclk'eventandclk='1'then

t:

=nott;n:

=n+1;

endif;

ift='1'andn<11then

beep<=clk500;

elsifn=11then

beep<=clk1k;

elsebeep<='Z';

endif;

endprocess;

endrtl;

libraryIEEE;

useIEEE.std_logic_1164.all;

useIEEE.std_logic_arith.all;

useIEEE.std_logic_unsigned.all;

entityclockis

port(

SA:

instd_logic;

SB:

instd_logic;

SC:

instd_logic;

SD:

instd_logic;

clk1:

instd_logic;

dout:

bufferstd_logic_vector(23downto0);

--seg_data:

outstd_logic_vector(7downto0);

--seg_com:

outstd_logic_vector(3downto0);

beep:

outstd_logic

--led:

outstd_logic_vector(3downto0)

);

endentityclock;

architecturertlofclockis

componentcnt_sis

port(en,clk,clr:

instd_logic;

dout:

bufferstd_logic_vector(7downto0);

c:

outstd_logic);

endcomponent;

componentcnt_his

port(en,clk,clr:

instd_logic;

dout:

bufferstd_logic_vector(7downto0)

);

endcomponent;

--componentsegmainis

--port(clk,reset_n:

instd_logic;

--datain:

instd_logic_vector(15downto0);

--seg_data:

outstd_logic_vector(7downto0);

--seg_com:

outstd_logic_vector(3downto0));

--endcomponent;

--componentringis

--port(en:

instd_logic;

--clk:

instd_logic;

--clk500:

instd_logic;

--clk1k:

instd_logic;

--beep:

outstd_logic);

--endcomponent;

componenthaoinis

port(din,clk:

instd_logic;

dout:

outstd_logic);

endcomponent;

componentnaolingis

port(h,m:

instd_logic_vector(7downto0);

clk4hzh,clk4hzm:

instd_logic;

sys_en,sys_rst:

instd_logic;

h_o,m_o:

outstd_logic_vector(7downto0);

beep:

outstd_logic);

endcomponent;

signalreg_h:

std_logic_vector(7downto0);

signalreg_m:

std_logic_vector(7downto0);

signalreg_s:

std_logic_vector(7downto0);

signalreg_m_s:

std_logic_vector(7downto0):

=X"59";

signalreg_m_m:

std_logic_vector(7downto0):

=X"59";

signalreg_m_h:

std_logic_vector(7downto0):

=X"59";

signalclk_h:

std_logic;

signalclk_m:

std_logic;

signalclk_s:

std_logic;

signalc_s:

std_logic;

signalc_m:

std_logic;

signalc_h:

std_logic;

signalsys_clk1:

std_logic;

signalsys_clk4:

std_logic;

signalsys_clk64:

std_logic;

signalsys_clk500:

std_logic;

signalsys_clk1k:

std_logic;

signalclki:

integer:

=750000;

signalsys_rst:

std_logic:

='0';

signalsys_en:

std_logic:

='1';

signalclk_ring,mh:

std_logic;

signalSAc,SBc,SCc,SDc:

std_logic;

signalen_r:

std_logic;

signalNL_reg_h,NL_reg_m:

std_logic_vector(7downto0);

signalNL_ring:

std_logic;

signalsys_clk4_NL_h,sys_clk4_NL_m:

std_logic;

begin

h:

cnt_hportmap(en=>sys_en,clk=>clk_h,clr=>sys_rst,dout=>reg_h);

m:

cnt_sportmap(en=>sys_en,clk=>clk_m,clr=>sys_rst,dout=>reg_m,c=>c_m);

s:

cnt_sportmap(en=>sys_en,clk=>sys_clk1,clr=>SCc,dout=>reg_s,c=>c_s);

--sled:

segmainportmap(clk=>clk1,reset_n=>SCc,seg_data=>seg_data,seg_com=>seg_com,datain=>dout(15downto0));

--ring0:

ringportmap(en=>en_r,clk=>clk_ring,clk500=>sys_clk500,clk1k=>sys_clk1k,beep=>beep);

haoin1:

haoinportmap(SA,sys_clk64,SAc);

haoin2:

haoinportmap(SB,sys_clk64,SBc);

haoin3:

haoinportmap(SC,sys_clk64,SCc);

haoin4:

haoinportmap(SD,sys_clk64,SDc);

NL:

naolingportmap(beep=>NL_ring,h=>reg_h,m=>reg_m,clk4hzh=>sys_clk4_NL_h,clk4hzm=>sys_clk4_NL_m,sys_en=>sys_en,sys_rst=>sys_rst,h_o=>NL_reg_h,m_o=>NL_reg_m);

beep<=clk_ringandmh;

--led<=reg_s(3downto0);

p_sys_clk:

process(clk1)

variablet1,t4,t64,t500,t1k:

integerrange0to50000000;

begin

ifclk1'eventandclk1='1'then

t1:

=t1+1;

t4:

=t4+1;

t64:

=t64+1;

t500:

=t500+1;

t1k:

=t1k+1;

ift1=clki/2then

t1:

=0;

sys_clk1<=notsys_clk1;

endif;

ift4=clki/8then

t4:

=0;

sys_clk4<=notsys_clk4;

endif;

ift64=clki/128then

t64:

=0;

sys_clk64<=notsys_clk64;

endif;

ift500=clki/1000then

t500:

=0;

sys_clk500<=notsys_clk500;

endif;

ift1k=clki/2000then

t1k:

=0;

sys_clk1k<=notsys_clk1k;

endif;

endif;

endprocessp_sys_clk;

p_c:

process(SAc,SBc,SCc,SDc)

begin

ifSAc='1'andSDc='0'then

clk_h<=sys_clk4;

else

clk_h<=c_m;

endif;

ifSAc='1'andSDc='1'then

sys_clk4_NL_h<=sys_clk4;

else

sys_clk4_NL_h<='0';

endif;

ifSBc='1'andSDc='0'then

clk_m<=sys_clk4;

else

clk_m<=c_s;

endif;

ifSBc='1'andSDc='1'then

sys_clk4_NL_m<=sys_clk4;

else

sys_clk4_NL_m<='0';

endif;

ifSDc='0'then

dout(7downto0)<=reg_s;

dout(15downto8)<=reg_m;

dout(23downto16)<=reg_h;

else

dout(7downto0)<="ZZZZZZZZ";

dout(15downto8)<=NL_reg_m;

dout(23downto16)<=NL_reg_h;

endif;

endprocessp_c;

P_ring:

process(reg_m,reg_s,sys_clk1k)

variableclk_ring_t:

std_logic;

variablet:

std_logic_vector(3downto0);

begin

ifreg_m=X"59"and(reg_s=X"50"orreg_s=X"52"orreg_s=X"54"orreg_s=X"56"orreg_s=X"58")then

clk_ring_t:

=sys_clk500;

elsifreg_m=X"00"andreg_s=X"00"then

clk_ring_t:

=sys_clk1k;

elseclk_ring_t:

='Z';

endif;

ifNL_ring='1'then

clk_ring_t:

=sys_clk1k;

endif;

ifsys_clk1k'eventandsys_clk1k='1'then

t:

=t+1;

endif;

ift>1thenmh<='1';

endif;

clk_ring<=clk_ring_t;

endprocessp_ring;

endrtl;