电子技术基础数字部分第五版康光华主编第4章习题答案.docx

《电子技术基础数字部分第五版康光华主编第4章习题答案.docx》由会员分享,可在线阅读,更多相关《电子技术基础数字部分第五版康光华主编第4章习题答案.docx(17页珍藏版)》请在冰点文库上搜索。

电子技术基础数字部分第五版康光华主编第4章习题答案

第四章习题答案

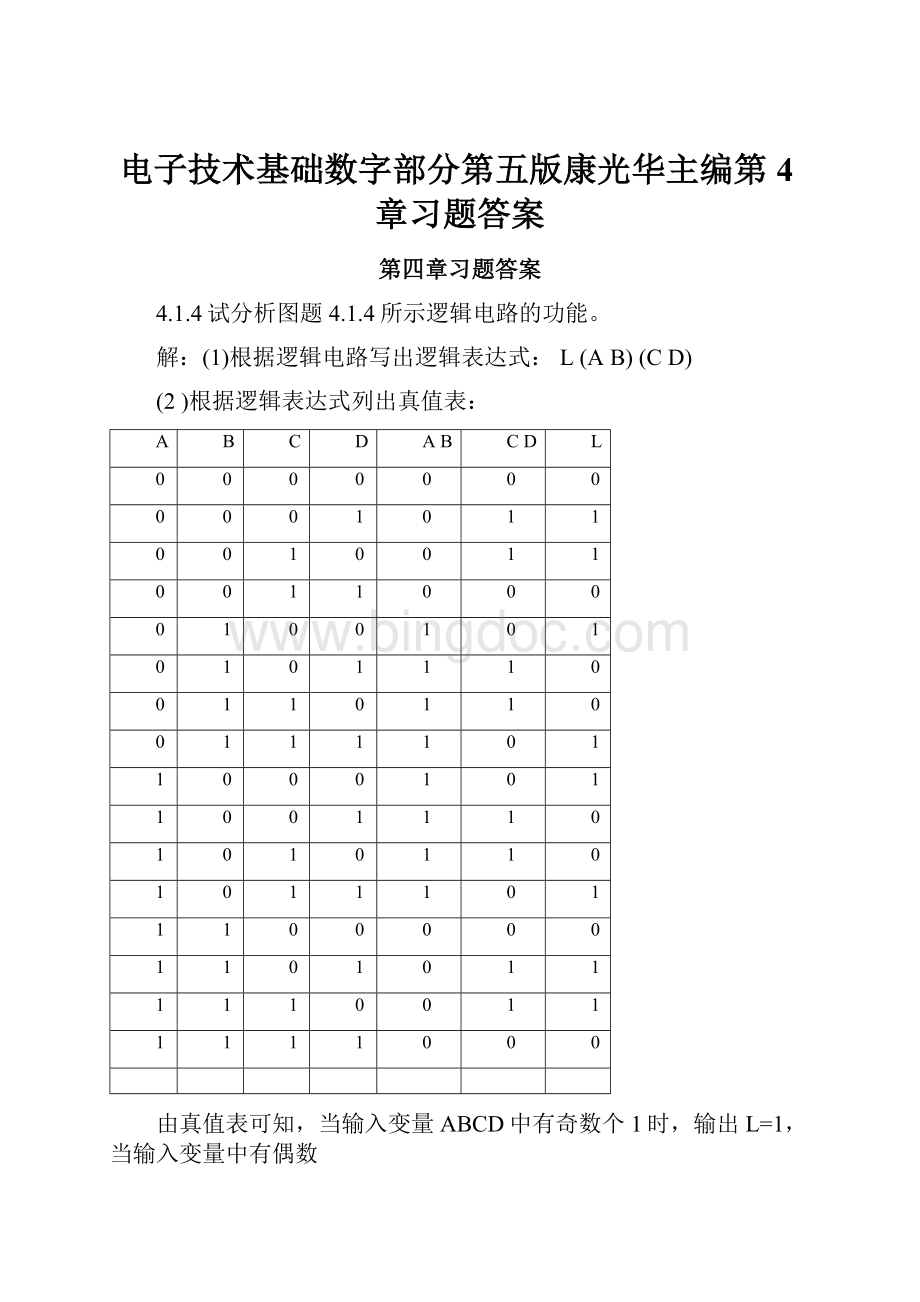

4.1.4试分析图题4.1.4所示逻辑电路的功能。

解:

(1)根据逻辑电路写出逻辑表达式:

L(AB)(CD)

(2)根据逻辑表达式列出真值表:

A

B

C

D

AB

CD

L

0

0

0

0

0

0

0

0

0

0

1

0

1

1

0

0

1

0

0

1

1

0

0

1

1

0

0

0

0

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

0

1

1

0

0

1

1

1

1

0

1

1

0

0

0

1

0

1

1

0

0

1

1

1

0

1

0

1

0

1

1

0

1

0

1

1

1

0

1

1

1

0

0

0

0

0

1

1

0

1

0

1

1

1

1

1

0

0

1

1

1

1

1

1

0

0

0

由真值表可知,当输入变量ABCD中有奇数个1时,输出L=1,当输入变量中有偶数

个1时,输出L=0。

因此该电路为奇校验电路。

4.2.5试设计一个组合逻辑电路,能够对输入的4位二进制数进行求反加1的运算。

可以用

任何门电路来实现。

解:

(1)设输入变量为A、B、C、D,输出变量为L3、L2、L1、L0。

(2)根据题意列真值表:

输

入

输

出

A

B

C

D

L3

L2

L1

L0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

0

0

1

0

1

1

1

0

0

0

1

1

1

1

0

1

0

1

0

0

1

1

0

0

0

1

0

1

1

0

1

1

0

1

1

0

1

0

1

0

0

1

1

1

1

0

0

1

1

0

0

0

1

0

0

0

1

0

0

1

0

1

1

1

1

0

1

0

0

1

1

0

1

0

1

1

0

1

0

1

1

1

0

0

0

1

0

0

1

1

0

1

0

0

1

1

1

1

1

0

0

0

1

0

1

1

1

1

0

0

0

1

殴CD

10

AB\

00

01

11

00

0

厂

1

7n

1:

01

(厂

b

U

1〕

11

0

0

0

0

10

1

0

0

0

(3)由真值表画卡诺图

(4)由卡诺图化简求得各输出逻辑表达式

L2BCBDBCDB(CD)B(CD)B(CD)

L1CDCDCD

LoD

(5)根据上述逻辑表达式用或门和异或门实现电路,画出逻辑图如下:

4.3.1判断下列函数是否有可能产生竞争冒险,如果有应如何消除。

(2)L2(A,B,C,D)m(5,7,8,9,10,11,13,15)

(4)L4(A,B,C,D)m(0,2,4,6,12,13,14,15)

解:

根据逻辑表达式画出各卡诺图如下:

(2)L2ABBD,在卡诺图上两个卡诺圈相切,有可能产生竞争冒险。

消除办法:

在卡诺图上增加卡诺圈(虚线)包围相切部分最小项,使

L2ABBDAD,可消除竞争冒险。

(4)L4ABAD,在卡诺图上两个卡诺圈相切,有可能产生竞争冒险。

消除办法:

在卡诺图上增加卡诺圈(虚线)包围相切部分最小项,使

L4ABADBD,可消除竞争冒险。

434画出下列逻辑函数的逻辑图,电路在什么情况下产生竞争冒险,怎样修改电路能消除

竞争冒险。

L(A,B,C)(AB)(BC)

解:

根据逻辑表达式画出逻辑图如下:

当a=C=0时,L(A,B,C)BB,可能产生竞争冒险。

消除竞争冒险办法:

(1)将逻辑表达式变换为L(代B,C)ABACBC,根据这个逻辑表达式组成的

逻辑电路就不会产生竞争冒险。

逻辑图如下:

(2)用卡诺图法在增加卡诺圈,包围卡诺圈相切部分,增加或与表达式中的或项

得到L(A,B,C)(AB)(BC)(AC),根据这个逻辑表达式组成的逻辑电路就不

会产生竞争冒险。

逻辑图如下:

441优先编码器CD4532的输入端Ii=l3=l5=1,其余输入端均为0,试确定其输出端

Y2Y1Y0。

解:

优先编码器CD4532的输入端除li外,还有使能端EI,由于EI=0,因此编码器不工作,其输出端Y2Y1Y0=000。

4.4.5为了使74HC138译码器的第十脚输出低电平,试标出各输入端应置的逻辑电平。

解:

查74HC138译码器的引脚图,第十脚为Y5,对应的A2A1A°=101,控制端E3、E2、

E1分别接1、0、0,电源输入端Vcc接电源,接地端GND接地,如下图所示:

FABCABCABCABC。

解:

用74HC138译码器实现逻辑函数,需要将函数式变换为最小项之和的形式

FABCABCABCABCm0m4m6m7

mogm4gm6gm7YocY4gY6gY7

在译码器输出端用一个与非门,即可实现所要求的逻辑函数。

逻辑图如下:

+5V

E

Ei

E2

74HC138

A2

Ai

Ao

4.4.12试用一片74x154译码器和必要的与非门,设计一个乘法器电路,实现2位二进

制数相乘,并输出结果。

解:

设2位二进制数分别为AB和CD,P3P2P1P0为相乘的结果,列出真值表如下:

输

入

输

出

A

B

C

D

P3

P2

P1

P0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

1

0

0

0

0

0

0

0

1

1

0

0

0

0

0

1

0

0

0

0

0

0

0

1

0

1

0

0

0

1

0

1

1

0

0

0

1

0

0

1

1

1

0

0

1

1

1

0

0

0

0

0

0

0

1

0

0

1

0

0

1

0

1

0

1

0

0

1

0

0

1

0

1

1

0

1

1

0

1

1

0

0

0

0

0

0

1

1

0

1

0

0

1

1

1

1

1

0

0

1

1

0

1

1

1

1

1

0

0

1

由真值表可直接写出各输出端的最小项逻辑表达式:

P2m14m11m10mi4gmiigmioYi4gYii(Yio

m14m13m11m9m7

mi4gmi3miigm9gm7gm6

丫14*13丫11*9*7*6

Pomi5mi3m7

mi5gmi3gm7gm5Y15g^13*7*5

用一片74x154和4个与非门即可实现所要求的乘法电路,逻辑电路图如下:

4.4.147段译码显示电路如图4414(a)所示,对应图4414(b)所示输入波形,试确定显示器显示的字符序列。

解:

当LE=O时,图4414(a)所示译码器能正常工作,所显示的字符就是A3A2A1A0

所表示的十进制数,显示的字符序列为0、1、6、9、4。

当LE由0跳变为1时,数字4被锁存,所以持续显示4。

4.4.21应用74HC151实现如下逻辑函数:

(1)LABCABCABC

(2)L(AeB)eC

解:

用74HC151实现逻辑函数,首先要将逻辑函数化成最小项的形式,根据最小项表达式确定数据输入端Di的取值,并注意变量的高低位与地址输入端的连接顺序。

⑴LABCABCABCm4m5m1

与数据选择器74HC151的标准表达式相比较

YS2SiSoD0S2S1SQS2S1S0D2S2S1SQ3

S2SiSoD4

S2SiS0D5S2S1SoD6S2S1S0D7

m0D0m1D1m2D2m3D3m4D4m5D5m6D6m7D7

将L与Y比较可得:

Do=D2=D3=D6=D7=O,D1=D4=D5=1

将A、B、C分别与地址输入端S2、S1、So连接,逻辑电路如图所示:

Do=D3=D5=D6=0,D1=D2=D4=D7=1

通道选通道选

择信号择信号

解:

应用教材中介绍的中规模组合逻辑电路

8选1数据选择器74HC151和3线8线译

码器74HC138(作为分配器使用)各一片组成数据传输电路,逻辑电路图如下:

+5V

电路通过74HC151根据通道选择信号A2A1A0选择数据,通过74HC138分配至由A2A1A0决定的输出端。

4.4.26试用数值比较器74HC85设计一个8421BCD码有效性测试电路,当输入为8421BCD码时,输出为1,否则输出0。

解:

8421BCD码的范围是0000~1001,即所有有效的8421BCD码均小于1010。

用74HC85构成的测试电路如下图所示,将8421BCD码输入接A3A2A1A0,B3B2B1B0接1010,当输入的8421BCD码小于1010时,FaBCD码输入

a3a2A1A01010

A3A2A1A0

A>B

B3B2B1B0

1A=B

1AFA=BFab

4433试用若干片74x283构成一个12位二进制加法器画出连接图。

解:

构成一个12位二进制加法器需要3片74x283以串行进位的方式进行连接,逻辑电

路图如下所示:

CO

A7B7A6B6A5B5A4B4

A3B3A2B2a1B1A0B0

A11B11A10B10A9B9a8B8

Iso

T—s

2

s

3

S4

5

^1s

6

s

S7

kkS8

9

s

o

I0——S11