数电实验.docx

《数电实验.docx》由会员分享,可在线阅读,更多相关《数电实验.docx(15页珍藏版)》请在冰点文库上搜索。

数电实验

一,实验结果分析

实验一:

QuartusII原理图输入法设计

(2)实验名称:

设计实现全加器

实验任务要求:

用实验内容

(1)中生成的半加器模块和逻辑门设计实现一个全加器,仿真并验证其功能,并下载到实验板测试,要求用拨码开关设定输入信号,发光二极管显示输出信号。

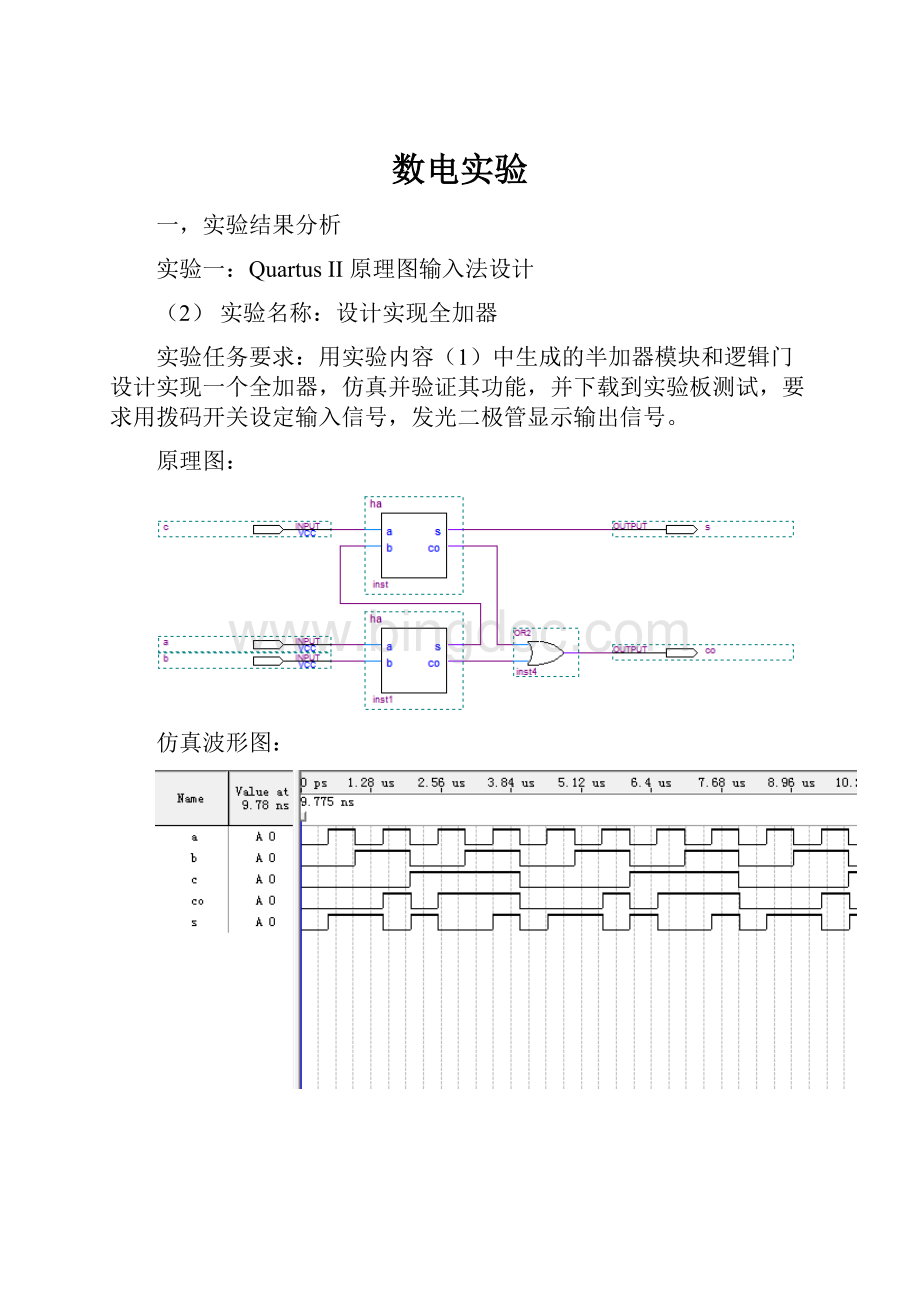

原理图:

仿真波形图:

仿真波形图分析:

输入a,b代表加数与被加数,输入c代表低位向本位的进位。

输出s代表本位和,输出co代表向高位的进位。

可得真值表为:

a

b

c

s

co

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

与上边的仿真波形图对比可知电路设计正确。

实验三:

用VHDL设计与实现时序逻辑电路

(3)实验名称:

连接8421计数器,分频器和数码管译码器

实验任务要求:

用VHDL语言设计实现一个带异步复位的8421码十进制计数器,分频器的分频系数为25k,并用数码管显示数字。

VHDL代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

entitydivis

port(clk1:

instd_logic;

clk_out:

outstd_logic);

end;

architecturedofdivis

signalcnt:

integerrange0to12499999;

signalclk_tmp:

std_logic;

begin

process(clk1)

begin

if(clk1'eventandclk1='1')then

ifcnt=12499999then

cnt<=0;

clk_tmp<=notclk_tmp;

else

cnt<=cnt+1;

endif;

endif;

endprocess;

clk_out<=clk_tmp;

end;

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYcount10IS

PORT(

clk2,clear2:

INSTD_LOGIC;

q:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDcount10;

ARCHITECTUREcountOFcount10IS

SIGNALq_temp:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

PROCESS(clk2,clear2)

BEGIN

IFclear2='1'THENq_temp<="0000";

ELSIF(clk2'eventANDclk2='1')THEN

IFq_temp="1001"THEN

q_temp<="0000";

ELSE

q_temp<=q_temp+1;

ENDIF;

ENDIF;

ENDPROCESS;

q<=q_temp;

ENDcount;

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

ENTITYseg7IS

PORT(a:

INSTD_LOGIC_VECTOR(3DOWNTO0);

b:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

cat1:

OUTSTD_LOGIC_VECTOR(5DOWNTO0)

);

ENDseg7;

ARCHITECTUREshowOFseg7IS

BEGIN

PROCESS(a)

BEGIN

CASEaIS

WHEN"0000"=>b<="1111110";

WHEN"0001"=>b<="0110000";

WHEN"0010"=>b<="1101101";

WHEN"0011"=>b<="1111001";

WHEN"0100"=>b<="0110011";

WHEN"0101"=>b<="1011011";

WHEN"0110"=>b<="1011111";

WHEN"0111"=>b<="1110000";

WHEN"1000"=>b<="1111111";

WHEN"1001"=>b<="1111011";

WHENOTHERS=>B<="0000000";

ENDCASE;

ENDPROCESS;

cat1<="111011";

ENDshow;

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entityjishuqi8421is

port(clk,clear:

INSTD_LOGIC;

cout:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

cat:

OUTSTD_LOGIC_VECTOR(5DOWNTO0)

);

endjishuqi8421;

architecturejiofjishuqi8421is

componentdiv25m

port(clk1:

instd_logic;

clk_out:

outstd_logic);

endcomponent;

componentcount10

PORT(

clk2,clear2:

INSTD_LOGIC;

q:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

endcomponent;

componentseg7

PORT(a:

INSTD_LOGIC_VECTOR(3DOWNTO0);

b:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

cat1:

OUTSTD_LOGIC_VECTOR(5DOWNTO0)

);

endcomponent;

signalc:

std_logic;

signald:

std_logic_vector(3downto0);

begin

u1:

divportmap(clk1=>clk,clk_out=>c);

u2:

count10portmap(clk2=>c,clear2=>clear,q=>d);

u3:

seg7portmap(a=>d,b=>cout,cat1=>cat);

endji;

仿真波形图:

(由于实际使用的50000000分频不方便仿真,仿真时使用12分频)

仿真波形图分析:

每隔12个时钟信号计数器的值会增加1,直到计数器的值为9时,再次返回0计数。

端口说明及连接图:

输入端口:

clk:

输入时钟信号。

clear:

输入复位信号。

输出端口:

cat[5]-cat[0]:

控制哪个数码管亮。

cout[6]-cout[0]:

控制数码管的哪一部分亮。

实验四:

用VHDL实现相关电路

(1)实验名称:

用VHDL语言设计并实现六个数码管串行扫描电路

实验任务要求:

要求同时显示0,1,2,3,4,5这6个不同的数字图形到6个数码管上,仿真验证其功能,并下载到实验板测试。

VHDL代码:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityshumakongzhiis

port(clk_in:

instd_logic;

cat:

outstd_logic_vector(5downto0);

a_out:

outstd_logic_vector(6downto0));

endshumakongzhi;

architectureaofshumakongzhiis

signaltmp:

std_logic_vector(6downto0);

signalcnt:

integerrange0to599;

signalcat_tmp:

std_logic_vector(5downto0);

begin

process(clk_in)

begin

if(clk_in'eventandclk_in='1')then

ifcnt=99then

cat_tmp<="011111";

cnt<=cnt+1;

elsifcnt=199then

cat_tmp<="101111";

cnt<=cnt+1;

elsifcnt=299then

cat_tmp<="110111";

cnt<=cnt+1;

elsifcnt=399then

cat_tmp<="111011";

cnt<=cnt+1;

elsifcnt=499then

cat_tmp<="111101";

cnt<=cnt+1;

elsifcnt=599then

cat_tmp<="111110";

cnt<=0;

elsecnt<=cnt+1;

endif;

endif;

casecat_tmpis

when"011111"=>tmp<="1111110";

when"101111"=>tmp<="0110000";

when"110111"=>tmp<="1101101";

when"111011"=>tmp<="1111001";

when"111101"=>tmp<="0110011";

when"111110"=>tmp<="1011011";

whenothers=>tmp<="0000000";

endcase;

endprocess;

cat<=cat_tmp;

a_out<=tmp;

enda;

仿真波形图:

仿真波形图分析:

cat[i]为0时,第i个数码管亮。

仿真时使cat[5]-cat[0]依次为0且每次只有一个为0。

cat[5]为0时显示0,cat[4]为0时显示1,cat[3]为0时显示2,cat[2]为0时显示3,cat[1]为0时显示4,cat[1]为0时显示5。

当扫描频率足够大时,就可以看到六个数码显示管同时显示,从左到右依次为012345。

端口说明及连接图:

输入:

clk_in:

输入时钟信号。

输出:

cat[5]-cat[0]:

控制哪个数码管亮。

a_out[6]-a_out[0]:

控制数码管的哪一部分亮。

(2)实验名称:

用VHDL语言设计并实现六个数码管滚动显示电路

实验任务要求:

向左滚动,用全灭的数码管填充右边直至全部变灭,然后再依次从右边一个一个地点亮。

状态为:

0012345->12345X->2345XX->

345XXX->45XXXX->5XXXXX->XXXXXX->XXXXX0->XXXX01->XXX012->XX0123->

X01234->012345。

VHDL代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYshumasaomiao3IS

PORT(CLK:

INSTD_LOGIC;

SG:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

BT:

OUTSTD_LOGIC_VECTOR(5DOWNTO0));

ENDshumasaomiao3;

ARCHITECTUREACEOFshumasaomiao3IS

componentfen2k

port(clk_in:

instd_logic;

clk_out:

outstd_logic);

endcomponent;

SIGNALCNT6:

INTEGERRANGE0TO11;

SIGNALA:

INTEGERRANGE0TO11;

SIGNALCOUNT:

INTEGERRANGE0TO4999:

=0;

SIGNAlFLAG:

INTEGERRANGE0TO12:

=0;

SIGNAlFLAG_A:

INTEGERRANGE0TO11;

SIGNALclk_tmp:

STD_LOGIC;

BEGIN

u1:

fen2kportmap(clk_in=>CLK,clk_out=>clk_tmp);

P1:

process(CNT6)

BEGIN

CASECNT6IS

WHEN0=>BT<="011111";A<=0;

WHEN1=>BT<="101111";A<=1;

WHEN2=>BT<="110111";A<=2;

WHEN3=>BT<="111011";A<=3;

WHEN4=>BT<="111101";A<=4;

WHEN5=>BT<="111110";A<=5;

WHEN6=>BT<="111111";A<=6;

WHEN7=>BT<="111111";A<=7;

WHEN8=>BT<="111111";A<=8;

WHEN9=>BT<="111111";A<=9;

WHEN10=>BT<="111111";A<=10;

WHEN11=>BT<="111111";A<=11;

WHENOTHERS=>NULL;

ENDCASE;

ENDPROCESSP1;

P2:

process(clk_tmp)

BEGIN

IFclk_tmp'EVENTANDclk_tmp='1'THEN

ifCNT6=11then

CNT6<=0;

else

CNT6<=CNT6+1;

endif;

IF(FLAG=12)THEN

FLAG<=0;

ENDIF;

IFCOUNT=4999THEN

COUNT<=0;

FLAG<=FLAG+1;

ELSE

COUNT<=COUNT+1;

ENDIF;

ENDIF;

ENDPROCESSP2;

P3:

process(A,FLAG,FLAG_A)

BEGIN

FLAG_A<=((A+FLAG)mod12);

CASEFLAG_AIS

WHEN0=>SG<="1111110";

WHEN1=>SG<="0110000";

WHEN2=>SG<="1101101";

WHEN3=>SG<="1111001";

WHEN4=>SG<="0110011";

WHEN5=>SG<="1011011";

WHEN6=>SG<="0000000";

WHEN7=>SG<="0000000";

WHEN8=>SG<="0000000";

WHEN9=>SG<="0000000";

WHEN10=>SG<="0000000";

WHEN11=>SG<="0000000";

WHENOTHERS=>NULL;

ENDCASE;

ENDPROCESSP3;

ENDACE;

仿真波形图:

仿真波形图的分析:

由波形可见,随着大计数周期的增加,依次产生0012345-12345X-2345XX-345XXX-45XXXX-5XXXXX-XXXXXX-XXXXX0-XXXX01-XXX012-XX0123-X01234-012345,这样便实现了循环移位。

端口说明及连接图:

输入:

clk:

输入时钟信号。

输出:

BT[5]-BT[0]:

控制哪个数码管亮。

SG[6]-SG[0]:

控制数码管的哪一部分亮。

二,故障及问题分析:

1.代码反复报错,其逻辑语句在分析后并未出错,可能是文件头出错或分号忘写,注意检查自己VHDL语言的规范性。

2.仿真波形不出现,可能是文件名错误;时钟周期设置错误;文件未编译;clear有效电平设计错误。

若问题无法解决,则考虑自己的电路设计逻辑是否出错。

3.电路下载到实验板后不能正常工作,首先检查仿真波形,检查实验板的时钟状态,检查程序无误后,检查管脚连接是否出错。

4.出现冒险:

尝试消除,有时候无法消除。

三,总结和结论:

1.实验前应测试实验板所需部件能否正常工作,保证实验的顺利进行。

2.上课前做好预习,上课时认真听讲,不遗漏老师的建议,课后及时复习掌握。

3.课前查阅相关资料,对实验的惯例和常识有更多的了解。

方便自己根据实验需要来进行模块的搭建或程序的编写。

4.应规范VHDL语言的使用习惯,变量名清晰明了,程序层次分明,一目了然,尽量避免冒险的出现,写程序时细心细致,避免出现低级错误,根据软件下方错误提示进行查错。

5.进一步掌握QuartusII,做好仿真,并学会分析仿真结果的正确性,实验前应先明确步骤,查好资料,确定思路,加以实现。

6.在电路出现问题时,要耐心细心的去寻找,去排查,去测试,查阅书籍,尝试解决。

若遇到自己无法解决的问题,及时与同学讨论或询问老师。

7.收获:

通过本次实验,对于数字电路与逻辑设计实验有了初步的了解,与课本上的内容对照,加深了对知识的理解,提高了自己的动手能力。