系统时序基础理论.docx

《系统时序基础理论.docx》由会员分享,可在线阅读,更多相关《系统时序基础理论.docx(15页珍藏版)》请在冰点文库上搜索。

系统时序基础理论

系统时序基础理论

对于系统设计工程师来说,时序问题在设计中是至关重要的,尤其是随着时钟频率的提高,留给数据传输的有效读写窗口越来越小,要想在很短的时间限制里,让数据信号从驱动端完整地传送到接收端,就必须进行精确的时序计算和分析。

同时,时序和信号完整性也是密不可分的,良好的信号质量是确保稳定的时序的关键,由于反射,串扰造成的信号质量问题都很可能带来时序的偏移和紊乱。

因此,对于一个信号完整性工程师来说,如果不懂得系统时序的理论,那肯定是不称职的。

本章我们就普通时序(共同时钟)和源同步系统时序等方面对系统时序的基础知识作一些简单的介绍。

一.普通时序系统(共同时钟系统)

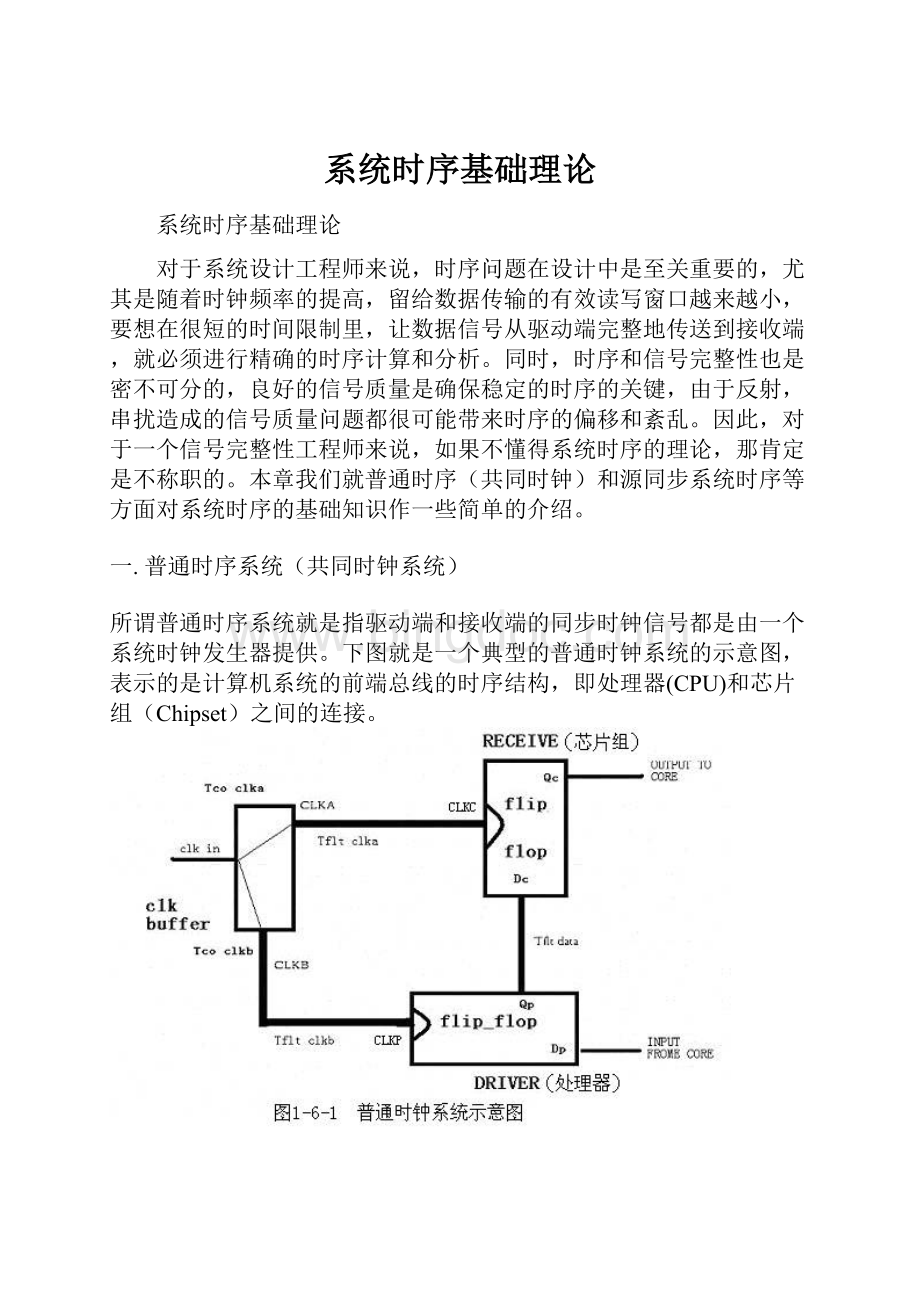

所谓普通时序系统就是指驱动端和接收端的同步时钟信号都是由一个系统时钟发生器提供。

下图就是一个典型的普通时钟系统的示意图,表示的是计算机系统的前端总线的时序结构,即处理器(CPU)和芯片组(Chipset)之间的连接。

在这个例子中,驱动端(处理器)向接收端(芯片组)传送数据,我们可以将整个数据传送的过程考虑为三个步骤:

1.核心处理器提供数据;

2.在第一个系统时钟的上升沿到达时,处理器将数据Dp锁存至Qp输出;

3.Qp沿传输线传送到接收端触发器的Dc,并在第二个时钟上升沿到达时,将数据传送到芯片组内部。

一般来说,标准普通时钟系统的时钟信号到各个模块是同步的,即图中的Tflightclka和Tflightclkb延时相同。

通过分析不难看出,整个数据从发送到接收的过程需要经历连续的两个时钟沿,也就是说,如果要使系统能正常工作,就必须在一个时钟周期内让信号从发送端传输到接收端。

如果信号的传输延迟大于一个时钟周期,那么当接收端的第二个时钟沿触发时,就会造成数据的错误读取,因为正确的数据还在传输的过程中,这就是建立时间不足带来的时序问题。

目前普通时序系统的频率无法得到进一步提升的原因就在于此,频率越高,时钟周期越短,允许在传输线上的延时也就越小,200-300MHz已经几乎成为普通时序系统的频率极限。

那么,是不是传输延时保持越小就越好呢?

当然也不是的,因为它还必须要满足一定的保持时间。

在接下来几节里,我们就建立和保持时间来分析一下时序设计需要考虑的一些问题以及正确的系统时序所必须满足的条件。

1. 时序参数的确定

对于时序问题的分析,我们首先要清楚地理解相关的一些时序参数的具体含义,比如Tco,缓冲延时,传播延迟,最大/小飞行时间,建立时间,保持时间,建立时间裕量,保持时间裕量,时钟抖动,时钟偏移等等,如果对这些参数的概念理解不深刻,就很容易造成时序设计上的失误。

首先要阐明的是Tco和缓冲延时(bufferdelay)的区别。

从定义上来说,Tco是指时钟触发开始到有效数据输出的器件内部所有延时的总和;而缓冲延时是指信号经过缓冲器达到有效的电压输出所需要的时间。

可以看出,Tco除了包含缓冲延时,还包括逻辑延时。

通常,确定Tco的方法是在缓冲输出的末端直接相连一个测量负载,最常见的是50欧姆的电阻或者30pF的电容,然后测量负载上的信号电压达到一定电平的时间,这个电平称为测量电压(Vms),一般是信号高电平的一半。

如Tco和缓冲延时的确定如下图所示:

信号从缓冲器出来之后,就要经过传输线到接收终端,信号在传输线上的传输的延时我们称为传播延迟(propagationdelay),它只和信号的传播速度和线长有关。

然而我们在大多数时序设计里面,最关键的却不是传播延迟这个参数,而是飞行时间(FlightTime)参数,包括最大飞行时间(MaxFlightTime)和最小飞行时间(MinFlightTime)。

飞行时间包含了传播延迟和信号上升沿变化这两部分因素,从下图中可以很容易看出两者的区别。

在较轻的负载(如单负载)情况下,驱动端的上升沿几乎和接收端的信号的上升沿平行,所以这时候平均飞行时间和传播延迟相差不大;但如果在重负载(如多负载)的情况下,接收信号的上升沿明显变缓,这时候平均飞行时间就会远远大于信号的传播延迟。

这里说的平均飞行时间是指Buffer波形的Vms到接收端波形Vms之间的延时,这个参数只能用于时序的估算,准确的时序分析一定要通过仿真测量最大/最小飞行时间来计算。

上面只是对信号上升沿的分析,对于下降沿来说,同样存在着最大/最小飞行时间的参数,如下图。

在时序计算时我们实际取的最大飞行时间是在上升沿和下降沿中取最长的那个飞行时间,而最小飞行时间则是取上升和下降沿中最短的那个飞行时间。

也有些时候,人们对信号的最大/最小飞行时间还有其它称谓,比如在Cadence软件中,就将最大飞行时间称为最终稳定延时(FinalSettleDelay),而将最小飞行时间称为最早开关延时(FirstSwitchDelay),如下图。

信号经过传输线到达接收端之后,就牵涉到建立时间和保持时间这两个时序参数,它们是接收器本身的特性,表征了时钟边沿触发时数据需要在锁存器的输入端持续的时间。

通俗地说,时钟信号来的时候,要求数据必须已经存在一段时间,这就是器件需要的建立时间(SetupTime);而时钟边沿触发之后,数据还必须要继续保持一段时间,以便能稳定的读取,这就是器件需要的保持时间(HoldTime)。

如果数据信号在时钟沿触发前后持续的时间均超过建立和保持时间,那么超过量就分别被称为建立时间裕量和保持时间裕量。

见图1-6-6,其中还考虑了时钟误差的因素。

每个器件的建立和保持时间参数,一般都可以在相应的DataSheet查到,对于设计者来说最大的目的是提高时序的裕量,这样即使信号完整性上出现一点问题,或者外界环境发生一定的变化,系统仍然能正常工作,这就是一个设计优良的系统应该体现出的超强的稳定性。

系统时序设计中对时钟信号的要求是非常严格的,因为我们所有的时序计算都是以恒定的时钟信号为基准。

但实际中时钟信号往往不可能总是那么完美,会出现抖动(Jitter)和偏移(Skew)问题。

所谓抖动,就是指两个时钟周期之间存在的差值,这个误差是在时钟发生器内部产生的,和晶振或者PLL内部电路有关,布线对其没有影响,如图1-6-7。

除此之外,还有一种由于周期内信号的占空比发生变化而引起的抖动,称之为半周期抖动。

总的来说,jitter可以认为在时钟信号本身在传输过程中的一些偶然和不定的变化之总和。

时钟偏移(skew)是指两个相同的系统时钟之间的偏移。

它表现的形式是多种多样的,既包含了时钟驱动器的多个输出之间的偏移,也包含了由于PCB走线误差造成的接收端和驱动端时钟信号之间的偏移,比如在图1-6-1中所示,CLKA和CLKB之间的差异,CLKC和CLKP之间的差异均为时钟偏移,这些偏移量在时序计算中需要全部考虑。

除了上面提到的这些概念,还有一点要注意的是,时刻不能忽略信号完整性对时序的影响,比如串扰会影响微带线传播延迟;反射会造成数据信号在逻辑门限附近波动,从而影响最大/最小飞行时间;时钟走线的干扰会造成一定的时钟偏移。

有些误差或不确定因素是仿真中无法预见的,设计者只有通过周密的思考和实际经验的积累来逐步提高系统设计的水平。

2 时序约束条件

下面来具体讨论一下系统时序需要满足的一些基本条件。

我们仍然以图1-6-1的结构为例,并可以据此画出相应的时序分析示意图(图1-6-8)。

在上面的时序图中,存在两个时序环,我们称实线的环为建立时间环,而虚线的环我们称之为保持时间环。

可以看到,这两个环都不是闭合的,缺口的大小就代表了时序裕量的多少,因此设计者总希望尽可能增大这个缺口。

同时还要注意到,每个环上的箭头方向不是一致的,而是朝着正反两个方向,因为整个系统时序是以时钟上升沿为基准的,所以我们时序环的起点为系统时钟clkin的上升沿,而所有箭头最终指向接收端的控制时钟CLKC的边沿。

先来分析建立时间环:

缺口的左边的半个时序环代表了从第一个系统时钟上升沿开始,直到数据传输至接收端的总的延时,我们计为数据延时,以Tdatatot表示:

Tdatatot=Tcoclkb+Tfltclkb+Tcodata+Tfltdata

上式中:

Tcoclkb是系统时钟信号CLKB在时钟驱动器的内部延迟;Tfltclkb是CLKB从时钟驱动器输出后到达发送端(CPU)触发器的飞行时间;Tcodata是数据在发送端的内部延迟;Tfltdata是数据从发送端输出到接收端的飞行时间。

从CLKC时钟边沿的右边半个时序环代表了系统时钟到达接收端的总的沿时,我们计为时钟延时,以Tclktot表示:

Tclktot=Tcycle+Tcoclka+Tfltclka–Tjitter

其中,Tcycle是时钟信号周期;Tcoclka是系统时钟信号CLKA(第二个上升沿)在时钟驱动器的内部延迟;Tfltclka是时钟信号从时钟驱动器输出到达接收端触发器的飞行时间;Tjitter是时钟的抖动误差。

因此我们可以根据建立时间裕量的定义,得到:

Tsetupmargin=Tclktot–Tdatatot–Tsetup

将前面的相应等式带入可得:

Tsetupmarin=Tcycle+Tcoclka+Tfltclka–Tjitter–Tcoclkb–Tfltclkb–Tcodata–Tfltdata–Tsetup

我们定义时钟驱动器(PLL)的两个时钟输出之间的偏移为TclockSkew,两根CLOCK走线之间的时钟偏移为TPCBSkew,即:

TclockSkew=Tcoclkb-Tcoclka;TPCBSkew=Tfltclkb-Tfltclka

这样就可以得到建立时间裕量的标准计算公式:

Tsetupmarin=Tcycle–TPCBskew–Tclockskew–Tjitter–Tcodata–Tfltdata-Tsetup (1.6.1)

再来看保持时间环:

对照图1-6-8,我们可以同样的进行分析:

Tdatadelay=Tcoclkb+Tfltclkb+Tcodata+Tfltdata

Tclockdelay=Tcoclka+Tfltclka

于是可以得出保持时间裕量的计算公式:

Tholdmargin=Tdatadelay–Tclockdalay–Tholdtime

即:

Tholdmargin=Tcodata+Tfltdata+Tclockskew+Tpcbskew–Thold (1.6.2)

可以看到,式1.6.2中不包含时钟抖动Jitter的参数。

这是因为Jitter是

指时钟周期间(CycletoCycle)的误差,而保持时间的计算和时钟周期无关。

对于任何时钟控制系统,如果要能保证正常工作,就必须使建立时间余量和保持时间裕量都至少大于零,即Tsetupmarin>0;Tholdmargin>0,将公式1.6.1和1.6.2分别带入就可以得到普通时钟系统的时序约束条件不等式:

TPCBskew+Tclockskew+Tjitter+Tcodata+Tfltdata+Tsetup Tcodata+Tfltdata+Tclockskew+Tpcbskew>Thold (1.6.4)

需要注意的是:

1.数据在发送端的内部延时Tcodata可以从芯片的datasheet查到,这个值是一个范围,在式1.6.3中取最大值,在式1.6.4中取最小值。

2.数据在传输线上的飞行时间Tfltdata在实际计算中应该取最大/最小飞行时间参数,在式1.6.3中取最大飞行时间,在式1.6.4中取最小飞行时间。

3.时钟的偏移TPCBskew和Tclockskew也是一个变化的不确定参数,一般为+/-Nps,同样,在建立时间约束条件1.6.3中取+Nps,而在保持时间约束条件1.6.4中取-Nps。

从上面的分析可以看到,对于PCB设计工程师来说,保证足够稳定的系统时序最有效的途径就是尽量减小PCBskew和信号传输的飞行时间,而其它的参数都只和芯片本身的性能有关。

实际中经常采取的措施就是严格控制时钟和数据的走线长度,调整合理的拓补结构,并尽可能减少信号完整性带来的影响。

然而,即便我们已经考虑的很周全,普通时钟系统的本身的设计瓶颈始终是无法打破的,也就是建立时间的约束,我们在尽可能减少由PCB布线引起的信号延迟之外,器件本身的特性如Tco、Jitter、TSetup等等将成为最主要的制约因素,尽管我们可以通过提高工艺水平和电路设计技术来不断提高数字器件的性能,但得到的效果也仅仅是在一定范围之内提升了系统的主频,在频率超过300MHz的情况下,我们将不得不放弃使用这种普通时钟系统设计。

二. 源同步时序系统

针对普通时钟系统存在着限制时钟频率的弊端,人们设计了一种新的时序系统,称之为源同步时序系统。

它最大的优点就是大大提升了总线的速度,在理论上信号的传送可以不受传输延迟的影响。

下面我们来看看这种源同步时钟系统的结构。

1. 源同步系统的基本结构

图1-6-9是一个基本的源同步时钟系统的结构示意图。

可以看到,驱动芯片在发送数据信号的同时也产生了选通信号(Strobe),而接收端的触发器由该选通信号脉冲控制数据的读取,因此,这个选通信号也可以称为源同步时钟信号。

源同步时钟系统中,数据和源同步时钟信号是同步传输的,我们保证这两个信号的飞行时间完全一致,这样只要在发送端的时序是正确的,那么在接收端也能得到完全正确的时序。

整个系统在时序上的稳定性完全体现在数据和选通信号的匹配程度上,包括传输延迟的匹配,器件性能的匹配等等,只要两者条件完全相同,那么我们就可以保证系统的时序绝对正确,而对系统的最高时钟频率没有任何限制。

当然,对于任何数据接收来说,一定的建立和保持时间都是必须满足的,源同步时钟系统也同样如此,主要体现在数据信号和选通信号之间的时序要求上。

最理想的情况就是选通信号能在数据信号的中央部分读取,如图1-6-10所示,这样才能保证最充分的建立和保持时间。

为了保证选通信号和数据信号相对保持正确的时序,在源同步时钟系统中是通过驱动芯片内部的数字延时器件DLL来实现(见图1-6-9),而不是通过PCB走线来控制,因为相比较而言,DLL器件能做到更为精确的延时,同时还可以受芯片电路控制,调节起来更为方便。

2. 源同步时序要求

前面已经提到源同步时钟系统设计中最重要的一点就是保证data和strobe信号之间的偏移(Skew)最小,引起这些误差的最主要的因素就是实际系统中各器件的时序参数Tco的不同,此外还有布线上引起的差异,为了更好地说明这些Skew对时序的具体影响,下面我们还是通过时序图分析的方法来计算一下源同步时钟系统中信号的建立时间裕量和保持时间裕量。

首先考虑建立时间裕量:

和普通时序分析的方法一下,我们也是从建立时间环的角度考虑,参考1-6-9的结构图,我们可以作出驱动端和接收端的时序示意图(1-6-11)。

Tdata=Tcodata+Tfltdata

Tstrobe=Tcostrobe+Tfltstrobe+Tdelay

其中,Tco和Tflt分别代表数据/选通信号在器件的内部延迟和信号传输的飞行时间,Tdelay是指数据信号和选通信号之间的延迟,由系统内DLL延时器件决定,图中假设为一个时钟周期。

将上式带入建立时间裕量的计算公式:

Tsetupmargin=Tclk–Tdata–Tsetup

可以得到:

Tsetupmargin=(Tcostrobe+Tfltstrobe+Tdelay)-(Tcodata+Tfltdata)–Tsetup

如果我们将数据和Strobe信号在器件内的延时差异定义为Tvb;将PCB走线引起的延时差异定义为Tpcbskew:

Tvb=Tcodata–(Tcostrobe+Tdelay)

Tpcbskew=Tfltdata–Tfltstrobe

这样可以得到一个简单的建立时间裕量方程:

Tsetupmargin=-Tvb–Tsetup–Tpcbskew (1.6.5)

注意:

公式1.6.5中Tvb是一个负值,从公式中可以看出,如果数据和选通信号的Tco相同的话,其大小就是-Tdelay,也就说明数据信号必须提前于选通信号发送。

再考虑保持时间裕量,如图1-6-12,同样分析可以得到:

Tholdmargin=(Tcodata+Tfltdata+Tdelay)–(Tcostrobe+Tfltstrobe)–Thold

如果定义:

Tva=Tcodata–Tcostrobe+Tdelay,为正值;Tpcbskew定义不变。

则保持时间裕量的计算公式为:

Tholdmargin=Tva–Thold–Tpcbskew (1.6.6)

在公式1.6.5和1.6.6中,两个重要的参数是Tvb和Tva,Tvb表示“Validbefore”,即数据在选通脉冲前有效存在的时间;Tva表示“Validafter”,指选通信号脉冲之后数据仍然有效持续的时间。

这两个时序参数一般都可以在器件的datasheet上会找到。

和普通时钟系统相比,源同步总线在PCB布线的设计上反而更为方便,设计者只需要严格保证线长的匹配就行了,而不用太多的考虑信号走线本身的长度。

当然,尽管源同步数据传输在理论上突破了频率的限制,但随着频率的提高,在控制Skew上也变得越来越困难,尤其是一些信号完整性因素带来的影响也越发显得突出,而且目前的高速系统设计中,往往综合应用了普通时钟和源同步时钟技术,比如对于地址/控制信号采用普通时钟总线,而高速的数据传输则是采用源同步总线。

这些对于高速PCB设计分析人员来说是一个非常严峻的挑战。