同步加法器毕业课程设计.docx

《同步加法器毕业课程设计.docx》由会员分享,可在线阅读,更多相关《同步加法器毕业课程设计.docx(18页珍藏版)》请在冰点文库上搜索。

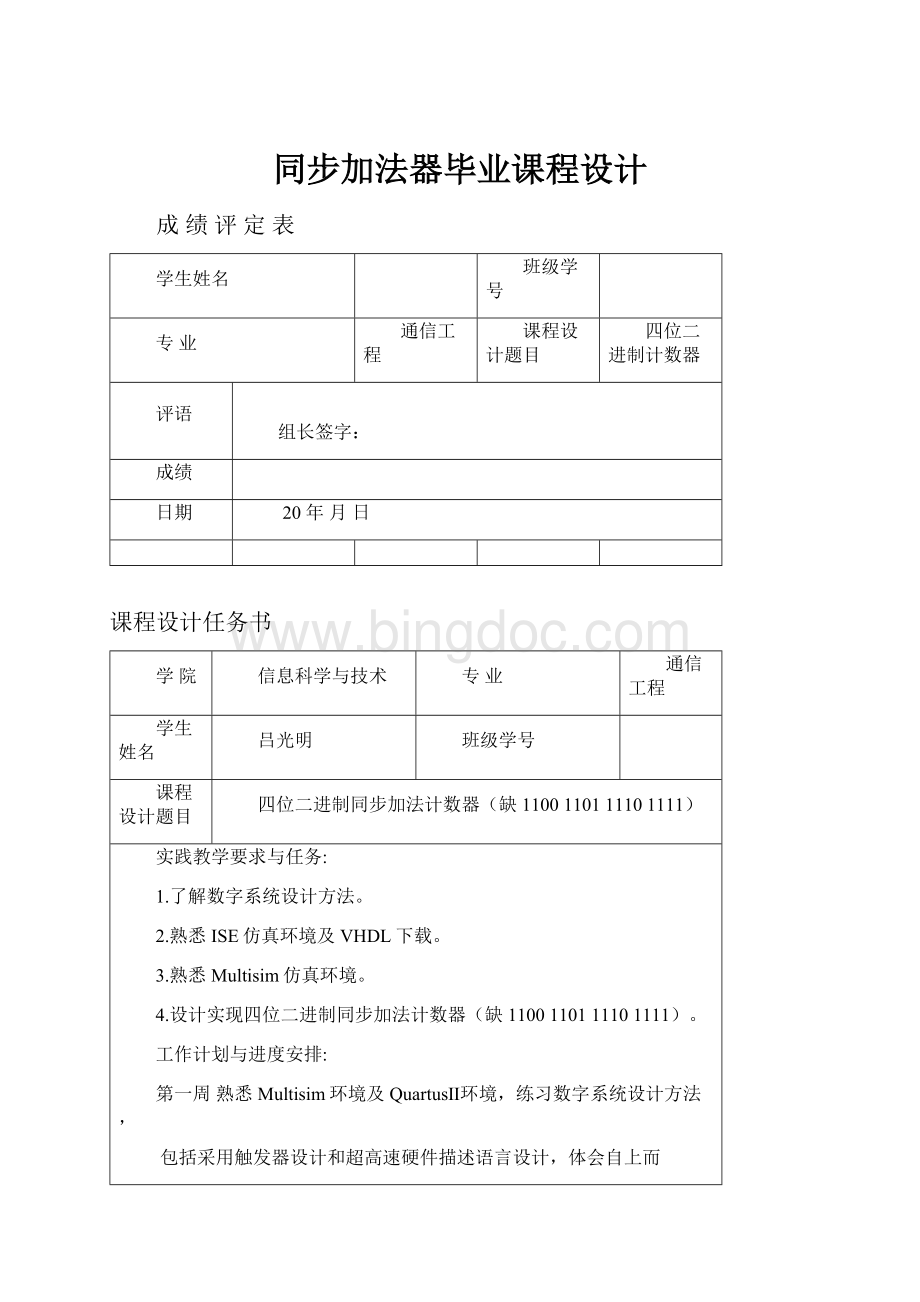

同步加法器毕业课程设计

成绩评定表

学生姓名

班级学号

专业

通信工程

课程设计题目

四位二进制计数器

评语

组长签字:

成绩

日期

20年月日

课程设计任务书

学院

信息科学与技术

专业

通信工程

学生姓名

吕光明

班级学号

课程设计题目

四位二进制同步加法计数器(缺1100110111101111)

实践教学要求与任务:

1.了解数字系统设计方法。

2.熟悉ISE仿真环境及VHDL下载。

3.熟悉Multisim仿真环境。

4.设计实现四位二进制同步加法计数器(缺1100110111101111)。

工作计划与进度安排:

第一周熟悉Multisim环境及QuartusⅡ环境,练习数字系统设计方法,

包括采用触发器设计和超高速硬件描述语言设计,体会自上而

下、自下而上设计方法的优缺点。

第二周在QuartusⅡ环境中用VHDL语言实现四位二进制同步加法计

数器(缺1100110111101111),在仿真器上显示结果波形,

并下载到目标芯片上,在实验箱上观察输出结果。

在Multisim环境中仿真实现四位二进制同步加法计数器(1100110111101111),并通过虚拟仪器验证其正确性。

指导教师:

刘洋,喻红婕

201年月日

专业负责人:

201年月日

学院教学副院长:

201年月日

摘要

本文利用QuartusII与Multisim两种软件,在QuartusⅡ环境中用VHDL语言实现四位二进制同步加法计数器(缺1100110111101111)在仿真器上显示结果波形,并下载到目标芯片上,在实验箱上观察输出结果。

在Multisim环境中仿真实现同样效果,并通过虚拟仪器验证其正确性。

关键词:

VHDL;四位二进制;同步加法计数器

一、课程设计目的1

二、设计框图1

三、实现过程2

1、Quartusii实现过程2

1.1建立工程2

1.2VHDL源程序7

1.3编译及仿真10

1.4引脚锁定及下载15

1.5仿真结果分析16

2、multisim实现过程16

2.1求驱动方程16

2.2画逻辑电路图20

2.3逻辑分析仪的仿真20

2.4结果分析21

四、总结21

五、参考书目23

一、课程设计目的

1:

了解同步加法计数器工作原理和逻辑功能。

2:

掌握计数器电路的分析、设计方法及应用。

3:

学会正确使用JK触发器。

二、设计框图

状态转换图是描述时序电路的一种方法,具有形象直观的特点,即其把所用触发器的状态转换关系及转换条件用几何图形表示出来,十分清新,便于查看。

在本课程设计中,四位二进制同步加法计数器用四个CP下降沿触发的JK触发器实现,其中有相应的跳变,即跳过了1100110111101111四个状态,这在状态转换图中可以清晰地显示出来。

具体结构示意框图和状态转换图如下:

B:

状态转换图

三、实现过程

1.1建立工程

图1.1QUARTUS软件的启动界面

(1)点击File–>NewProjectWizard创建一个新工程,系统显示如图1.1:

图1.2工程创建向导的启始页

(2)点击Next,为工程选择存储目录、工程名称、顶层实体名等,如图1.3所示;

(3)点击Next,若目录不存在,系统可能提示创建新目录,如图1.4所示,点击“是”按钮创建新目录,系统显示如图1.5所示;

(4)系统提示是否需要加入文件,在此不添加任何文件;

(5)点击Next,进入设备选择对话框,如图1.6,这里选中实验箱的核心芯片CYCLONE系列FPGA产品EP1C6Q240C8;

(6)点击Next,系统显示如图1.7,提示是否需要其他EDA工具,这里不选任何其他工具;

(7)点击Next后,系统提示创建工程的各属性总结,若没有错误,点击Finish,工程创建向导将生成一个工程,这时软件界面如图1.8,在窗口左侧显示出设备型号和该工程的基本信息等。

图1.3输入工程名称、存储目录

图1.5提示是否添加文件

图1.6芯片型号选择

图1.7提示是否利用其他EDA设计工具

图1.8工程阐述汇总

至此工程创建好完成。

1.2VHDL源程序

为实现四位二进制同步加法计数器(缺1100110111101111)的功能,可用VHDL编写一个程序实现,具体操作过程如下:

(1)点击File->New创建一个设计文件,系统显示如图1.9;

图1.9创建一个设计文件

(2)选择设计文件的类型为VHDLFile;

(3)点击OK,系统显示如图1.10,窗口右侧为VHDL的编辑窗口。

图1.10新建的一个VHDL源文件的编辑窗口

(4)在编辑窗口中编辑以下程序:

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entitycount16is

port(CP,r:

instd_logic;

q:

outstd_logic_vector(3downto0));

endcount16;

architecturebehavioralofcount16is

signalcount:

std_logic_vector(3downto0);

beginprocess(cp,r)

begin

ifr='0'then

count<="0000";

elsifcp'eventandcp='1'

thencount<=count+1;

ifcount="1011"then

count<="0000";

endif;

endif;

endprocess;

q<=count;

endbehavioral;

(5)输入程序后,存盘,如图1.11所示:

图1.11存盘

1.3编译及仿真

(1)点击Processing->StartCompilation编译该文件,系统将开始编译,结束后,给出提示信息和编译结果,如图1.12所示:

图1.12编译结果显示

(2)建立时序仿真文件,如图1.13所示,选择“VectorWaveformFile”,出现图1.14的界面,在Name空白处击右键,Insert→InsertNodeorBus。

图1.13

图1.14

在图1.14中单击

图1.15

在图1.15中单击,再单击→OK→OK。

如图1.16所示

图1.16

仿真文件存盘时,文件名字必须与顶层文件同名,即count16,默认即可。

图1.17

图1.18

图1.18是为仿真输入赋值的。

如想赋值‘1’,单击。

(2)单击菜单进行仿真

图1.19

仿真结果如图1.20所示

图1.20仿真波形

1.4引脚锁定及下载。

(1)进行引脚锁定。

点击Assignments->pins分配引脚,具体数值为:

CP-PIN28、r-PIN49、q3-PIN114、q2-PIN115、q1-PIN116、q0-PIN117。

如图1.21所示

图1.21

回到quartusII环境:

点击Processing——〉StartCompliation重新编译,锁定引脚,如图1.22所示

图1.22

(2)进行引脚锁定。

点击Tools——〉Programmer——>HardwareSetup进行下载前设置,如图1.23:

图1.23

点击Start进行下载,下载完成后,实验结果将在实验箱上显示。

1.5仿真结果分析

由仿真波形图可以清楚地看到在一个周期之内,即由小到大,依次完成了四位二进制加法计数的功能。

其中由于缺了1000100110101011四个状态,即缺了十进制数中的891011四个数,在波形仿真中,在这几个状态处发生跳变,即由0111跳到1100,再由1111直接跳回到0000,即完成一个周期的计数,不断循环往复。

四、总结

通过这次课程设计,加强了我们动手、思考和解决问题的能力。

在设计过程中,我对课本的知识得到了巩固和加强,由于课本上的知识太多,平时课间的学习并不能很好的理解和运用各个软件的功能,而且考试内容有限,所以在这次课程设计过程中,我们了解了很多元件的功能,并且对于其在电路中的使用有了更多的认识。

平时看课本时,有时问题老弄不懂,做完课程设计,那些问题就迎刃而解了。

而且还可以记住很多知识。

在设计过程中,出现了各种各样的问题,有些是单一原因引起的,有的是综合原因引起的,这些都很考验我的毅力与坚持。

其中有些问题是由于理论课上的知识没有掌握好,导致求驱动方程时总是有错误,但经过反复认真仔细的计算,最终还是得出正确结果。

由此让我学会了遇到问题不要逃避,要勇敢面对!

这次课程设计虽然在功能上完全实现了课题的要求,即实现了四位二进制加法计数器的全部要求,但是相应的不足之处还应该考虑到。

例如在Multism环境下设计逻辑电路时,怎样更好地布局以及连线,使整个电路图不至于杂乱无章等等问题,虽然是细节问题,但往往可以决定成败,这些问题都应该引以为戒并作为以后设计相关电路时的参考。

经过两个星期的课程设计,过程曲折可谓一言难尽。

在此期间我也失落过,也曾一度热情高涨。

从开始时满富激情到最后汗水背后的复杂心情,点点滴滴无不令我回味无穷。

生活就是这样,汗水预示着结果也见证着收获。

劳动是人类生存生活永恒不变的话题。

五.参考书目

1.李世雄,丁康源.数字集成电子技术教程.北京:

高等教育出版社,1993.

2.潘松,王国栋.VHDL实用教程.西安:

电子科技大学出版社,2001.

3.童诗白,徐振英.现代电子学及应用.北京:

高等教育出版社,1994.

4.阎石.数字电子技术基础.4版.北京:

高等教育出版社,1998.

5.黄正瑾.在系统编程技术及其应用.南京;东南大学出版社,1997.