BJ8M601A规格书final修改版0708.docx

《BJ8M601A规格书final修改版0708.docx》由会员分享,可在线阅读,更多相关《BJ8M601A规格书final修改版0708.docx(116页珍藏版)》请在冰点文库上搜索。

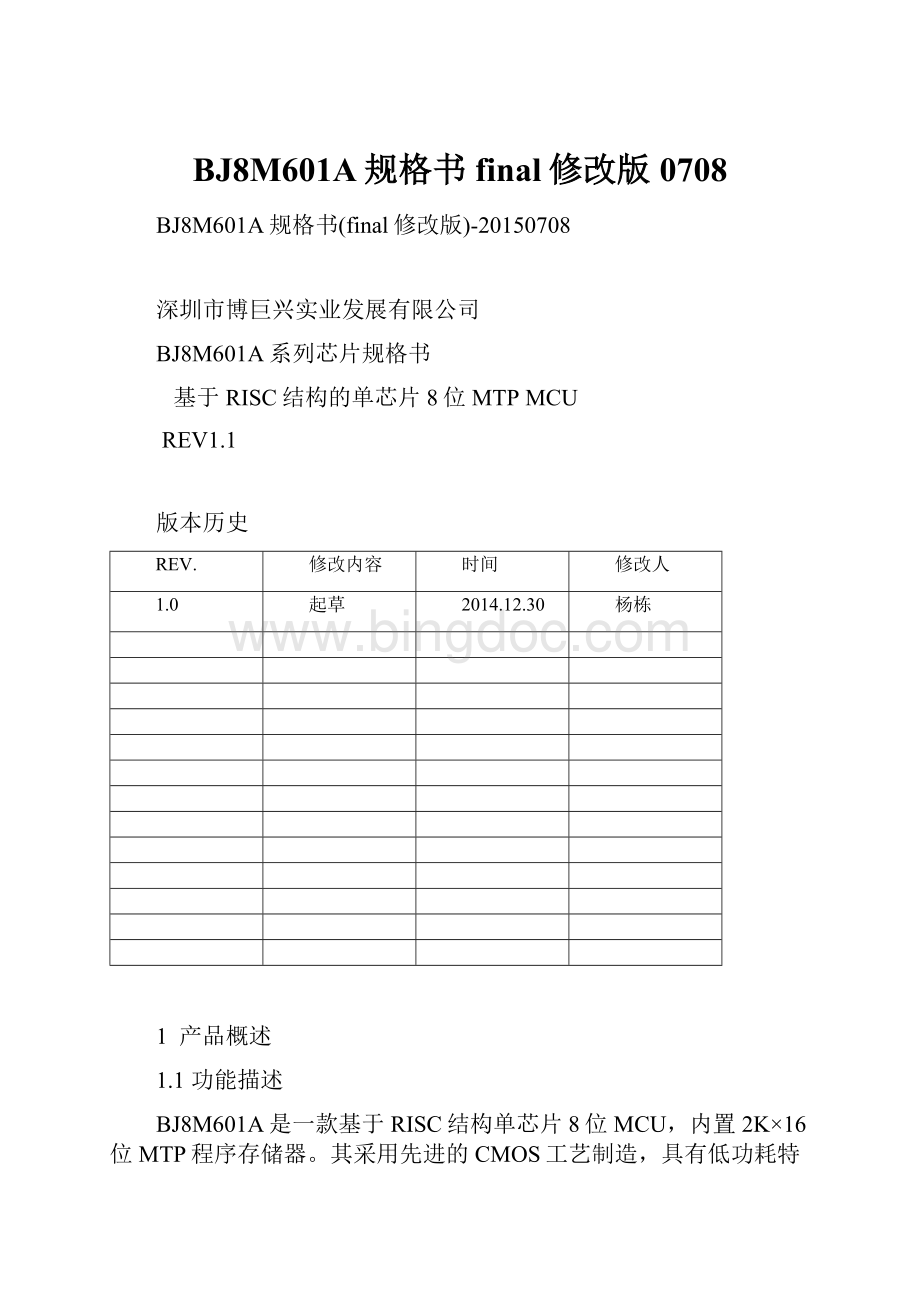

BJ8M601A规格书final修改版0708

BJ8M601A规格书(final修改版)-20150708

深圳市博巨兴实业发展有限公司

BJ8M601A系列芯片规格书

基于RISC结构的单芯片8位MTPMCU

REV1.1

版本历史

REV.

修改内容

时间

修改人

1.0

起草

2014.12.30

杨栋

1产品概述

1.1功能描述

BJ8M601A是一款基于RISC结构单芯片8位MCU,内置2K×16位MTP程序存储器。

其采用先进的CMOS工艺制造,具有低功耗特性和低工作电压能力。

芯片具有睡眠等(低功耗)模式。

是一款集成了Timer/Counter/PWM/ADC等功能的通用MCU,是消费品等电子应用领域的理想选择。

1.1.1CPU

RISC内核

8级堆栈

1.1.2存储器

ROM:

2K*16位

RAM:

224*8位

1.1.3指令集

68条指令

1.1.4中断

一个中断入口地址(08h)

8个中断源(T0/T1/INT0/INT1/LVD/ADC/PWM0占空比中断/PWM1占空比中断)

1.1.5I/O口

一共14个I/O端口,其中P1.2作为输出时只能为开漏输出

所有引脚都可单独编程操作

8个引脚有唤醒功能:

P1口

14个引脚有内部上拉功能

7个引脚有内部下拉功能:

P1口

8个引脚有开漏功能:

P1口

2个外部中断口:

P1.5(外部中断1)、P1.7(P0.1)(外部中断0)

2个引脚有40mA低驱动能力P0.3、P1.3

1.1.6定时器/计数器

定时器/计数器0

--基本定时器/计数器

--支持预分频功能

定时器1

--16位可配置定时器/计数器

--支持两路PWM功能

--蜂鸣器(Buzzer)输出

--支持预分频功能

1.1.7看门狗定时器

支持预分频功能

可配置溢出复位和唤醒

1.1.8时钟系统

内部RC振荡器(主时钟)

--频率:

1MHz、4MHz、8MHz、16MHz、24MHz

--误差:

±1%

内部RC振荡器(WDT时钟)

--频率:

128KHz

--误差:

±3%

可配置外接晶体振荡器

--支持32768Hz~24MHz外部晶振

--支持晶体振荡器和陶瓷振荡器

外部RC振荡器

--频率:

100KHz~10MHz

--误差:

±5%

外部时钟源

--工作频率:

32768Hz~24MHz

可双时钟工作

振荡器可分频:

1、2、4、8

1.1.9工作模式

普通模式:

高低速时钟都正常工作

低速模式:

只有低速时钟正常工作

STOP模式:

全部都停止工作

IDLE模式:

CPU停止工作,外设可以工作.

1.1.10低电压复位(LVR)

低电压复位选择:

1.6V(默认)、1.8V、2.3V、2.7V、3.0V、3.3V、3.6V、3.9V

复位时间选择:

140us、6.5ms、18ms(默认)、72ms、228ms

1.1.11低电压检测(LVD)

低电压检测选择:

2.2V、2.4V、2.6V、2.9V、3.2V、3.5V、3.8V、4.1V

可配置产生中断

1.1.12低功耗模式

停止模式下功耗小于1.2uA。

外部中断、定时器0和看门狗可唤醒

1.1.13工作温度范围

-40℃~+85℃

1.1.14电压工作范围

1.8V~5.5V@4MHz,-40℃~+85℃

1.1.15抗干扰能力

ESD:

优于±4000V

EFT:

优于±4000V

1.1.16封装形式

SOP16、TSSOP16、SOP14

1.2PIN配置

表1引脚说明表

管脚名称

输入/输出

管脚序号

描述

VDD

P

1

电源

P1.0/ADC9/OSCI

I/O

2

IO;具有开漏输出功能;具有唤醒功能;ADC输入通道9;外部时钟端;

P1.1/ADC8/OSCO/ROUT/PDA

I/O

3

IO;具有开漏输出功能;具有唤醒功能;ADC输入通道8;系统时钟(SYSCK)输出端;外部时钟端;烧录引脚PDA;

P1.2/RESET/VPP

I/O

4

IO;芯片复位口;具有唤醒功能;作为输出时只能为开漏输出;烧录引脚VPP;

P1.3/PWM1/(PWM0_N)

I/O

5

IO;具有开漏输出功能;具有唤醒功能;PWM1输出;

(通过代码选项可配置为PWM0互补输出);

P1.4/T1/PWM0

I/O

6

IO;具有开漏输出功能;具有唤醒功能;PWM0输出;定时器1计数输入;

P1.5/PWM0_N/INT1

I/O

7

IO;具有开漏输出功能;具有唤醒功能;PWM0互补输出;外部中断1输入端;

P1.6/ADC7

I/O

8

IO;具有开漏输出功能;具有唤醒功能;ADC输入通道7;

P1.7/INT0/ADC6/T0

I/O

9

IO;具有开漏输出功能;具有唤醒功能;外部中断0输入端;定时器0计数输入;

P0.5/ADC5/PWM1_N

I/O

10

IO;ADC输入通道5;PWM1互补输出;

P0.4/ADC4/VREF

I/O

11

IO;ADC输入通道4;ADC参考电压端口;

P0.3/ADC3/(PWM1_N)

I/O

12

IO;ADC输入通道3;(通过代码选项可配置为PWM1互补输出);

P0.2/ADC2

I/O

13

IO;ADC输入通道2;

P0.1/ADC1/(INT0)

I/O

14

IO;ADC输入通道1;通过代码选项可配置为外部中断0输入端;

P1.0/ADC0/PCL

I/O

15

IO;ADC输入通道0;烧录引脚PCL;

VSS

P

10

地;

2标准功能

2.1CPU核

CPU核主要包含7个主要寄存器及2个存储器单元。

表2MCU架构说明

模块名称

描述

程序计数器

此寄存器在CPU的工作周期间起到很重要的作用,它记录CPU每个周期处理程序存储器中指令的指针。

在一个CPU周期中,程序计数器将程序存储器地址(10bits),指令指针推送到程序存储器,然后自动加1以进行下一次周期。

堆栈寄存器

堆栈寄存器是用来记录程序返回的指令指针。

当程序调用函数,程序计数器会将指令指针推送到堆栈寄存器。

在函数执行结束之后,堆栈寄存器会将指令指针送回到程序计数器以继续原来的程序处理。

指令寄存器

程序计数器将指令指针(程序存储器地址)推送到程序存储器,程序存储器将程序存储器的数据(16bits)及指令推送到指令寄存器。

BJ8M601A的指令是16bits,包括3种信息:

直接地址,立即数及控制信息。

CPU能将立即数推送到工作寄存器,或者进行某些处理后,根据控制信息,将立即数存储到直接地址所指向的数据存储器寄存器中。

直接地址(8bits)

数据存储器的地址。

CPU能利用此地址来对数据存储器进行操作。

直接数据(8bits)

CPU通过ALU利用此数据对工作寄存器进行操作。

控制信息

它记录着ALU的操作信息。

指令译码器

指令寄存器将控制信息推送到指令译码器以进行译码,然后译码器将译码后的信息发送到相关的寄存器。

算术逻辑单元

算术逻辑单元不仅能完成8位二进制的加,减,加1,减1等算术计算,还能对8位变量进行逻辑的与,或,异或,循环移位,求补,清零等逻辑运算。

工作寄存器

工作寄存器是用来缓存数据存储器中某些存储地址的数据。

状态寄存器

“状态寄存器包括与算法运算指令相关的进位标注位(C),辅助进位标注位(AC),零标注位(Z),溢出标注位(OV);以及数据存储器分页配置位(DPAGE)”

间接寻址地址寄存器

在BJ8M601A的指令集中,MP0是用于间接寻址地址。

程序存储器

BJ8M601A内带2K×16位的MTP作为程序存储器。

由于指令的操作码(OPCODE)是16bits,用户最多只能编程1K的指令。

程序存储器的地址总线是11bits,数据总线是16bits。

数据存储器

BJ8M601A内带224bytes的SRAM作为数据存储器。

此数据存储器的地址总线是8bits,数据总线是8bits。

SRAM存储器分为2页。

分页的选择由特殊功能寄存器STATUS的DPAGE来指定。

DPAGE为0时,选择的是分页0数据存储区。

DPAGE为1时,选择的是分页1数据存储区。

2.1.1存储器

(1)程序存储器

程序存储器主要用于指令的存储,在BJ8M601A中,该程序存储器是2K*16bit的程序MTP,对于程序员来说,该存储器只读,如要改写则需要严格按MTP自编程操作方可写入。

系统的reset地址为0x000。

严格来说,程序存储器并没有2K的大小,它的可用地址范围为0x000~0x7f7,程序编译时地址段不应超出这个范围,否则将会出错。

地址范围为0x7f8~0x7ff共8个word用作预留的代码选项区。

图1程序存储器

(2)数据存储器

数据存储器主要用于程序运行过程中,全局以及中间变量的存储。

在BJ8M601A中,数据存储器一共有224个单元。

它可被划分为3个区域。

不分页数据存储区:

0x40~0x7f(当DPAGE=0或1时)

分页0数据存储区:

0x80~0xff(当DPAGE=0时)

分页1数据存储区:

0x80~0x9f(当DPAGE=1时)

分页的选择由特殊功能寄存器STATUS的DPAGE来指定。

DPAGE为0时,选择的是分页0数据存储区。

DPAGE为1时,选择的是分页1数据存储区。

分页1数据存储区的寻址范围是0x80~0x9f,一共只有32个byte,超出此范围为无效的地址。

不分页数据存储区的访问不受DPAGE的限制,不管DPAGE为0或者1,对地址段0x40~0x7f的访问都是有效的,对应物理存储的同一段存储空间。

进入中断服务程序时,STATUS会被压入堆栈区;退出中断服务程序时STATUS恢复为对应的值。

因此,DPAGE也会被进栈保护和出栈恢复。

图2数据存储器分页

2.1.2状态寄存器

状态寄存器包含ALU的算术状态及复位状态。

状态寄存器类似于其它寄存器,可以作为任何指令的目标寄存器。

表1状态寄存器列表

地址

名称

POR值

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

04h

STSTUS

---00000

-

-

-

DPAGE

OV

Z

AC

C

地址

名称

POR值

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

08h

STA1

-----000

-

-

-

-

-

LVDOUT

PD

-

表1状态寄存器各位功能表

STSTUS

04H

位

符号

读写

说明

4

DPAGE

R/W

数据存储器页选择位

1:

选择数据存储器的PAGE1

0:

选择数据存储器的PAGE0

3

OV

R/W

溢出标志(用于有符号数运算时才有意义)

1:

BIT7有进位(或借位),但BIT6没有进位(或没有借位)

0:

有符号数算术结果是错误

2

Z

R/W

零标志

1:

算术或逻辑操作结果为0

0:

算术或逻辑操作结果不为0

1

AC

R/W

半进位标志/借位标志

用于借位时,极性相反

1:

结果的最高位出现进位溢出

0:

结果的最高位不出现进位溢出

0

C

R/W

进位标志/借位标志

用于借位时,极性相反

1:

结果的最高位出现进位溢出

0:

结果的最高位不出现进位溢出

STA1

08H

位

符号

读写

说明

2

LVDOUT

R

低电压标注位。

当检查电压低于低电压阈值时由硬件置位,检查到电压高于设置的低电压阈值时由硬件清零。

1:

有效;

0:

无效。

1

PD

R/C

低功耗模式标注位。

一旦软件执行“STOP”指令,此标志位便会置位;只有当软件写0清除、或上电复位、或低电压复位时才会重新置0。

1:

低功耗模式标注位有效

0:

低功耗模式标注位无效

0

N/A

N/A

N/A

2.1.3中断寄存器

BJ8M601A有8个中断源,只有一个中断入口地址。

只要有中断标志位,就会有中断响应,响应中断之后需要软件将中断标志位清除,否则会不断响应中断。

表2中断寄存器列表

地址

名称

POR值

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

06h

IF0

--000000

ADF

LVDIF

INT1F

T1F

T0F

INT0F

07h

IEN0

0-000000

EA

EAD

ELVD

EINT1

ET1

ET0

EINT0

27h

EXINTS

----0000

-

-

-

-

E1EG[1:

0]

E0EG[1:

0]

2Dh

IF1

------00

PWM1DF

PWM0DF

2Eh

IEN1

------00

EPWM1D

EPWM0D

表3中断寄存器各位功能表

IF0

06H

位

符号

读写

说明

5

ADF

R/W

AD中断标志位

4

LVDIF

R/W

低电压检测(LVD)中断标志位

3

INT1F

R/W

外部中断1中断标志位

2

T1F

R/W

定时器/计数器1中断标志位

1

T0F

R/W

定时器/计数器0中断标志位

0

INT0F

R/W

外部中断0中断标志位

IEN0

07H

位

符号

读写

说明

7

EA

R/W

全局中断使能位

1:

使能全局中断

0:

禁止全局中断

5

EAD

R/W

AD中断使能位

1:

使能AD中断

0:

禁止AD中断

4

ELVD

R/W

低电压检测(LVD)中断使能位

1:

使能低电压检测(LVD)中断

0:

禁止低电压检测(LVD)中断

3

EINT1

R/W

外部中断1使能位

1:

使能外部中断1

0:

禁止外部中断1

2

ET1

R/W

定时器/计数器1中断使能位

1:

使能定时器/计数器1中断

0:

禁止定时器/计数器1中断

1

ET0

R/W

定时器/计数器0中断使能位

1:

使能定时器/计数器0中断

0:

禁止定时器/计数器0中断

0

EINT0

R/W

外部中断0使能位

1:

使能外部中断0

0:

禁止外部中断0

EXINTS

27H

位

符号

读写

说明

3:

2

E1EG[1:

0]

R/W

外部中断1边沿触发选择位

E1EG[1:

0]

边沿触发选择

00

下降沿触发

01

上升沿触发

10

高电平触发

11

低电平触发

1:

0

E0EG[1:

0]

R/W

外部中断0边沿触发选择位

E0EG[1:

0]

边沿触发选择

00

下降沿触发

01

上升沿触发

10

高电平触发

11

低电平触发

IF1

2DH

位

符号

读写

说明

1

PWM1DF

R/W

PWM1占空比中断标志

0

PWM0DF

R/W

PWM0占空比中断标志

IEN1

2EH

位

符号

读写

说明

1

EPWM1D

R/W

PWM1占空比中断使能位

1:

使能PWM1占空比中断

0:

禁止PWM1占空比中断

0

EPWM0D

R/W

PWM0占空比中断使能位

1:

使能PWM0占空比中断

0:

禁止PWM0占空比中断

2.2SFR

特殊功能寄存器(SFR)包含系统专用寄存器和辅助专用寄存器。

表4寄存器列表

地址

名称

POR值

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

00h

IAR0

00000000

01h

00000000

02h

MP0

00000000

03h

00000000

04h

STATUS

---00000

DPAGE

OV

Z

AC

C

05h

ACC

00000000

06h

IF0

--000000

ADF

LVDF

INT1F

T1F

T0F

INT0F

07h

IEN0

0-000000

EA

EAD

ELVD

EINT1

ET1

ET0

EINT0

08h

STA1

-----00-

LVDOUT

PD

09h

PCL

00000000

0AH

0BH

0CH

0Dh

CLKCON

-0--00-1

SYSCKOEN

RUNWCK

WCKEN

SYSCKEN

0Eh

WDTCON

000-0000

WDTRST

WDTSEL

WDTEN

-

WDTS[3:

0]

0Fh

WDTOVR

00000000

WDTOVR[7:

0]

10h

T0CON

00-00000

T0CLR

T0M

-

T0EG

T0PSC[2:

0]

T0EN

11h

T0C

00000000

T0C[7:

0]

12h

T0OVR

00000000

T0OVR[7:

0]

13h

T1CON0

00-00000

T1CLR

T1M

T1EG

T1PSC[2:

0]

T1EN

14h

T1CON1

00000000

PWM1NS

PWM1S

PWM0NS

PWM0S

PWM1NEN

PWM1EN

PWM0NEN

PWM0EN

15h

T1CH

00000000

T1C[15:

8]

16h

T1CL

00000000

T1C[7:

0]

17h

T1OVRH

00000000

T1OVR[15:

8]

18h

T1OVRL

00000000

T1OVR[7:

0]

19h

T1D0H

00000000

T1D0[15:

8]

1Ah

T1D0L

00000000

T1D0[7:

0]

1Bh

T1D1H

00000000

T1D1[15:

8]

1Ch

T1D1L

00000000

T1D1[7:

0]

1Dh

PWM0DZH

00000000

PWM0DZ[15:

8]

1Eh

PWM0DZL

00000000

PWM0DZ[7:

0]

1Fh

PWM1DZH

00000000

PWM1DZ[15:

8]

20h

PWM1DZL

00000000

PWM1DZ[7:

0]

21h

P0

---00000

-

-

P0[5:

0]

22h

P0OE

---00000

-

-

P0OE[5:

0]

23h

P0PU

---00000

-

-

P0PU[5:

0]

24h

25h

P1

00000000

P1[7:

0]

26h

P1OE

00000000

P1OE[7:

0]

27h

P1PU

00000000

P1PU[7:

0]

28h

P1PD

00000-00

P1PD[7:

3]

-

P1PD[1:

0]

29h

ODCON

00000000

P1OD[7:

0]

2Ah

PWK

00000000

P17WK

P16WK

P15WK

P14WK

P13WK

P12WK

P11WK

P10WK

2Bh

EXINTS

----0000

E1EG[1:

0]

E0EG[1:

0]

2Ch

LVDCON

----0000

LVDS[2:

0]

LVDEN

2Dh

IF1

------00

PWM1DF

PWM0DF

2Eh

IEN1

------00

EPWM1D

EPWM0D

2Fh

HDCON

------00

HDP13

HDP03

30h

ADDOH

----0000

ADDO[11:

8]

31h

ADDOL

00000000

ADDO[7:

0]

32h

ADCHH

00000000

ADCH[15:

8]

33h

ADCHL

00000000

ADCH[7:

0]

34h

ADCON0

0-000000

ADRDY

VREFSEL[1:

0]

AINS[3:

0]

35h

ADCON1

00000100

TGAP[2:

0]

TSAD[2:

0]

ADCKSEL[1:

0]

36h

ADCON2

0000--00

ADEN

DRDY

ADS

SC

VREFP[1:

0]

37h

ADDO

00000000

ADDO[11:

4]

38h

MTPOP

00000000

MTPOP[7:

0]

39h

IAPCON

0--0--00

VPPF

MTPWREN

MTPRD

MTPWR

3Ah

IAPADRH

------00

IAPADRH[10:

8]

3Bh

IAPADRL

00000000

IAPADRL[7:

0]

3Ch

IAPDATH

00000000

IAPDATH[15:

8]

3Dh

IAPDATL

00000000

IAPDATL[7:

0]

3Eh

METCH

00000000

METCH[7:

0]

3Fh

2.3时钟系统

图3BJ8M601A振荡器状态框图

BJ8M601A有两个时钟源。

一个是内部集成的时钟,另一个是外部时钟。

由代码选项选择CPU跑内部或外部时钟。

表5时钟系统寄存器列表

地址

名称

POR值

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

0Dh

CLKCON

00000001

SYSCKOEN

RUNWCK

WCKEN

SYSCKEN