常规型硬布线控制器Word格式文档下载.docx

《常规型硬布线控制器Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《常规型硬布线控制器Word格式文档下载.docx(20页珍藏版)》请在冰点文库上搜索。

T3下降沿

M1=1时DR1接收数据总线DBUS数据

LDDR2

M2=0时DR2接收寄存器堆B端口数据

M2=1时DR2接收数据总线DBUS数据

WRD

控制双端口寄存器堆RF的写操作

1且T2上升沿

RS_BUS#

控制RF的B端口数据是否能送DBUS上

LDER

将DBUS上的数据打入暂存寄存器ER

1且T4上升沿

SW_BUS#

将SW7-SW0数据送往DBUS

CEL#

选中双端口存储器RAM左端口

LRW

允许RAM左端口读操作

1且T3上升沿

允许RAM左端口写操作

0且T3上升沿

CER

RAM右端口读出数据并放到指令总线INS上

禁止右端口操作

LDAR1

将DBUS数据打入地址寄存器AR1

AR1_INC

AR1的值加1

LDAR2

M3=0时AR2的数据从程序计数器PC打入

1且T2下降沿

M3=1时AR2的数据从DBUS打入

LDR4

M4=1时R4的数据从DBUS打入

M4=0时R4的数据从IR0-IR3打入

PC_ADD

ALU2完成PC和IR低4位相加即PC+D

PC_INC

PC+1

LDPC

程序计数器PC接收来自DBUS的地址

LDIR

将来自RAM的指令打入指令寄存器IR

S2,S1,S0

选择运算器ALU的运算类型

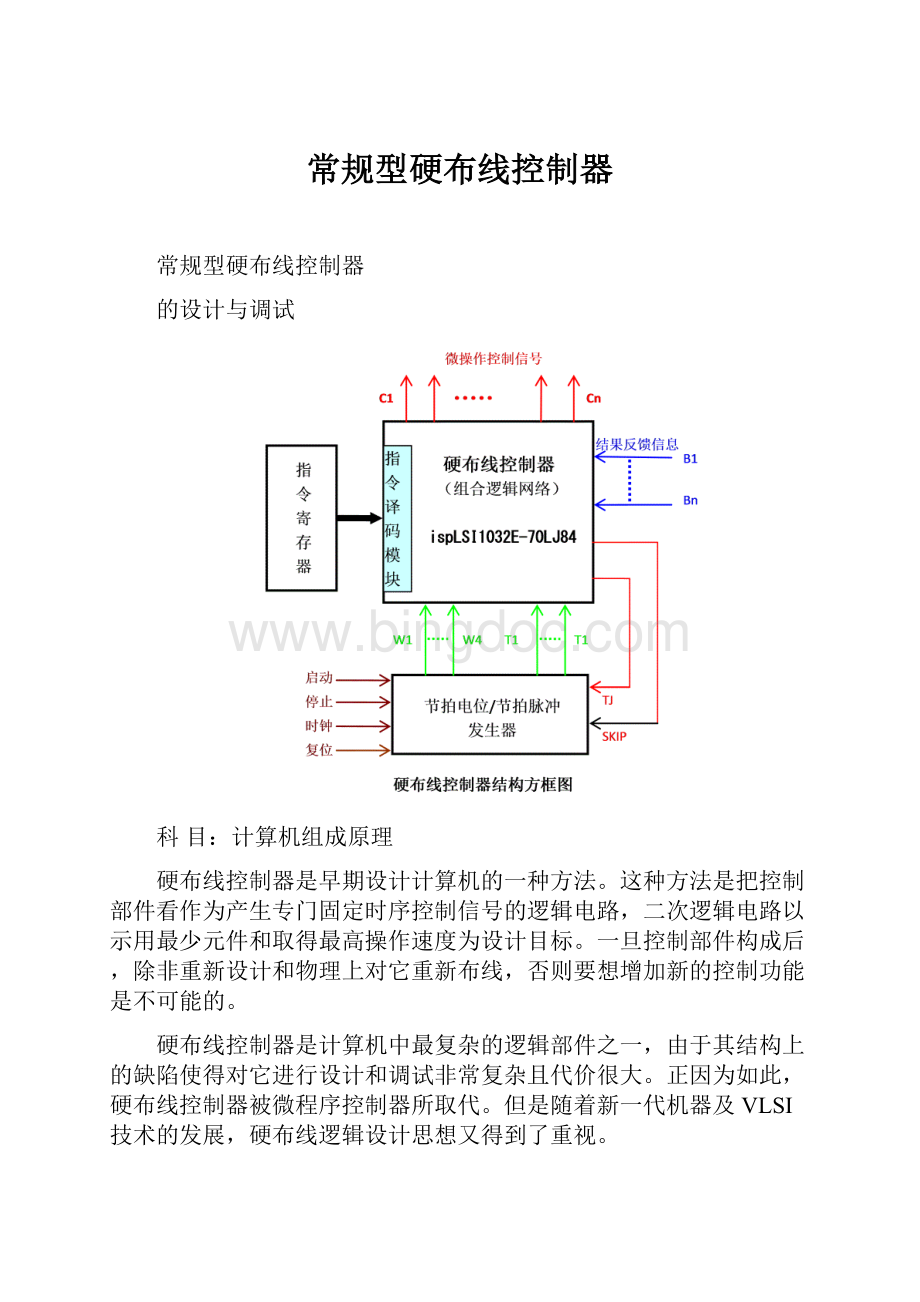

数据通路图:

设计说明书

设计步骤

分别画出控制台指令及机器指令流程图。

根据流程图作出微操作控制信号的译码与时序分布表,然后用逻辑表达式表示出每个信号。

由逻辑表达式写出ABEL语言源代码。

对程序进行编译,下载到芯片。

连线,调试。

测试。

具体设计思路

根据要求,列出所需的控制台指令和机器指令

控制台指令名称

指令功能

指令格式

SWC

SWB

SWA

KRR

读寄存器堆方式

KRD

读双端口存储器方式

KWE

写双端口存储器方式

KLD

加载寄存器堆方式

PR

启动程序方式

机器指令名称

助记符

R7

R6

R5

R4

R3

R2

R1

R0

加法

ADDRd,Rs

Rd+Rs->

Rd

RS1

RS0

RD1

RD0

减法

SUBRd,Rs

Rd-Rs->

乘法

MULRd,Rs

Rd*Rs->

逻辑与

ANDRd,Rs

Rd&

Rs->

存数

STARd,[Rs]

Rd->

[Rs]

取数

LDARd,[Rs]

[Rs]->

Rd

无条件转移

JMP[Rs]

PC

条件转移

JCD

C=1

PC+D->

D3

D2

D1

D0

停机

STP

暂停运行

X

设计指令流程图

硬布线控制器的指令流程图与微程序控制器的指令流程图基本一致。

实验台对每步程序的执行提供的节拍只有四个W1-W4,而控制台指令所需要的节拍要大于四个,这就需要我们在设计时将指令拆分一下,即一个指令占用两步,八个节拍,并能够在后四个节拍实现指令的循环执行。

于是,我们加了个ST内部信号作为标志位,当ST=0时,标志执行指令的前四个节拍,当ST=1时,标志执行指令的后四个节拍。

注意到只有CLR#到来后的第四拍时ST信号才发生翻转,所以又设了一个SSTO信号作为ST信号的触发信号。

具体实现ST-SSTO模块如下:

我们增加了一个标志位RUN,由于按CLR#按钮复位后,实验系统的时序停止在T4,W4,ST的值为0,这样SSTO=!

ST&

W4的值为1.按QD启动按钮后,由于立即产生T1信号,在T1的上升沿使ST置1,在第一组W1,W2,W3,W4时,ST的值为1,这是我们不希望看到的。

增加了标志位RUN后,按CLR#按钮复位,使RUN为0。

由于SSTO=!

ST*W4*RUN,因此复位后的SSTO=0.按QD启动按钮,在T1的上升沿,使RUN=1。

根据SSTO的布尔表达式,在W1,W2,W3时,SSTO=0,直到W4时,才使SSTO=1,由于ST:

=CLR#*SSTO#CLR*ST,在W4过后的下一个T1的上升沿,才使ST置1,从而将控制台操作的两种状态区分开来。

设计的控制台指令流程图,机器指令流程图如下:

根据流程图,进行微操作信号的译码并列出时序表

说明:

我们将控制台指令KRR,KRD,KWE,KLD,PR分别拆分为KRR1,KRR2,KRD1,KRD2,

KWE1,KWE2,KLD1,KLD2和PR1,PR2。

每个小指令分别占用W1-W4四个节拍。

OUTPUT

ST=0

ST=1

KRR1

KRD1

KWE1

KLD1

PR1

KRR2

KRD2

KWE2

KLD2

W4

W1

W2

W3

M1

M2

M3

M4

S0

S1

S2

W1,W3

SKIP

TJ

W2,W4

SSTO

ST=1PR2

PR2

ADD

SUB

MUL

AND

LDA

STA

JMP

JC

W4&

图中绿色信号代表此时的微操作信号为低有效。

根据表格,列写出每个信号的逻辑表达式,并写出ABEL语言的源程序

ABEL语言源代码如下:

MODULEComputeDECLARATIONS

"

INPUT

SWC,SWB,SWAPIN3..5;

IR7,IR6,IR5,IR4PIN6..9;

MF,T1,W1,W2,W3,W4,C,CLRPIN10..17;

ALU_BUS,AR1_INC,CEL,CER,LDAR1,LDAR2,LDDR1,LDDR2,LDER,LDIR,LDPC,LDR4,LRWPIN29..41;

PC_INC,PC_ADD,RS_BUS,SW_BUS,WRD,SKIP,TJ,M1,M2,M3,M4,S0,S1,S2PIN63..76;

TEMP

MF1,SSTONODEISTYPE'

COM'

;

RUN,STNODEISTYPE'

REG'

tKRR,tKRD,tKWE,tKLD,tPRNODEISTYPE'

KRR1,KRD1,KWE1,KLD1,PR1,KRR2,KRD2,KWE2,KLD2,PR2NODEISTYPE'

ADD,SUB,MUL,AND,LDA,STA,JMP,JC,STPNODEISTYPE'

CLK=.C.;

EQUATIONS

MF1=!

CLR&

MF#T1&

CLR;

RUN:

=CLR;

RUN.CLK=MF1;

ST:

=CLR&

SSTO#CLR&

ST;

ST.CLK=MF1;

SSTO=!

RUN&

W4;

“指令译码部分

tKRR=SWC&

!

SWB&

SWA;

tKRD=!

SWC&

tKWE=!

tKLD=!

tPR=!

KRR1=!

tKRR;

KRR2=ST&

KRD1=!

tKRD;

KRD2=ST&

KWE1=!

tKWE;

KWE2=ST&

KLD1=!

tKLD;

KLD2=ST&

PR1=!

tPR;

PR2=ST&

ADD=PR2&

(!

IR7)&

IR6)&

IR5)&

IR4);

SUB=PR2&

(IR4);

MUL=PR2&

(IR5)&

AND=PR2&

LDA=PR2&

(IR6)&

STA=PR2&

JMP=PR2&

(IR7)&

JC=PR2&

STP=PR2&

“输出管脚

ALU_BUS=(ADD#SUB#MUL#AND)&

W3#(STA&

W4);

AR1_INC=(KRD2#KWE2)&

CEL=!

((KRD2#KWE2#KLD2#KRR2)&

W1#(W3&

LDA)#(W4&

STA));

CER=(KLD2#KRR2)&

W2#(W1&

PR2);

LDAR1=W4&

(KRR1#KRD1#KWE1#KLD1)#(W2&

LDA)#(W2&

STA);

LDAR2=W4&

(KRR1#KLD1)#(PR2&

W1);

LDDR1=W2&

(ADD#SUB#MUL#AND);

LDDR2=LDDR1#(W2&

LDER=W3&

(KLD2#ADD#SUB#MUL#AND#LDA);

LDIR=CER;

LDPC=W4&

(PR1#JMP#(JC&

C));

LDR4=LDPC;

LRW=W1&

KRD2#W3&

LDA;

M1=!

LDDR1;

M2=!

LDDR2;

M3=W4&

(KRR1#KLD1);

M4=W4&

(PR1#JMP);

PC_INC=W1&

PR2;

PC_ADD=W4&

JC&

C;

RS_BUS=!

(W2&

(LDA#STA)#W4&

(KRR2#JMP));

SW_BUS=!

(W1&

(KWE2#KLD2#KRR2)#(W3&

KLD2)#(W4&

ST));

S0=SUB#STA;

S1=ADD#SUB;

S2=MUL;

SKIP=W1&

ST#(W1&

(KRD2#KWE2))#(W2&

(KRR2#STA))#W2&

(JMP#JC#STP);

TJ=W1&

KRD2#W2&

KLD2#W4&

(tKRR#tKWE#tKLD)#W4&

STP;

WRD=W4&

END

对程序进行编译,无误后下载到芯片

连线,调试,验收

连线表格如下:

3

Input

PULLUP

35

Output

4

36

5

37

IR7

6

38

IR6

7

39

IR5

8

40

IR4

9

41

MF

10

63

T1

11

64

12

RS_BUS

65

13

SW_BUS

66

14

67

15

68

16

69

CLR

17

70

29

71

30

72

CEL

31

73

32

74

33

75

34

76

验收程序:

地址

指令

机器代码

00H

LDAR0[R2]

58H

01H

LDAR1[R3]

5DH

02H

ADDR0R1

04H

03H

JC+5

95H

ANDR1R0

31H

05H

SUBR0R3

1CH

06H

STAR0[R1]

44H

07H

MULR0R1

24H

08H

60H

09H

JMP[R1]

84H

初始化:

寄存器

存入内容

61H

内存单元

83H

计算结果:

内容

46H

12H

标志信号RUN的分析及测试

由控制台指令流程图可知一条控制台指令被分割成了两部分,一部分可以看作是指令执行的初始化(如选定中转地址,指定初始地址等),另一部分看作是指令的执行阶段(可以循环执行)。

每条指令执行时第一部分只执行一遍,第二部分是循环执行的,所以要保证ST信号第一遍执行时为0,之后保持为1。

该部分实现图如下所示:

代码

当按一下CLR时将使得RUN和ST都变为零,且时序停留在W4,T4时刻,由于RUN=0,所以虽然在W4时刻,但是SSTO信号仍然为零,是无效的

启动程序后,在第一的T1的上升沿RUN变为1,于是当W4=1时SSTO=1,那么触发器ST的输入也变为1,在下一个T1的上升沿,ST将变为0,控制信号就由流程图的左半部跳至右半部。